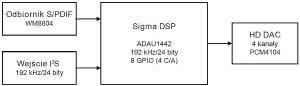

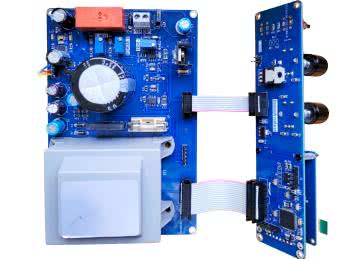

Schemat blokowy zestawu MegaDSP+ pokazano na rysunku 1. Bazuje on na procesorze sygnałowym ADAU1442 (można też użyć ADAU1445) z rodziny Sigma DSP. Układ pracuje w trybie SELFBOOT, co oznacza, że po załączeniu zasilania lub restarcie pobiera program z zewnętrznej pamięci EEPROM. W tym trybie nie jest wymagany zewnętrzny procesor sterujący, a wszystkie zmiany konfiguracji lub parametrów wykonywane za pomocą interfejsu GPIO.

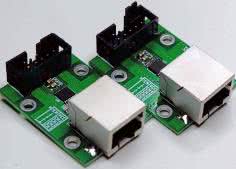

Moduł pracuje tylko z cyfrowym sygnałem wejściowym w standardzie S/PDIF (gniazdo "SPDIF") lub I²S (gniazdo "I²S"). Dzięki wbudowanemu wielokanałowemu konwerterowi częstotliwości próbkowania jest możliwa współpraca ze źródłami sygnału o różnej częstotliwości próbkowania z przedziału 32...192 kHz. Wewnętrzna obróbka sygnału oraz przetwarzanie C/A odbywa się z częstotliwością 192 kHz.

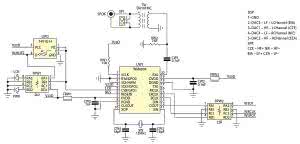

Schemat ideowy Sigma DSP_Plus podzielono na bloki funkcjonalne. Na rysunku 2 pokazano odbiornik S/PDIF. Sygnał wejściowy poprzez transformator separujący TW jest doprowadzony do odbiornika/dekodera UW1 typu WM8804.

W zależności od potrzeb, jest możliwe doprowadzenie sygnału poprzez gniazdo SPDIF typu RCA lub przez SP1 w postaci listwy kołkowej. Układ WM8804 pracuje w typowej aplikacji, z własnym generatorem kwarcowym 12 MHz i konfiguracją sprzętową I²S/24-bity.

Restart po załączeniu zasilania zapewnia U3 z bloku DSP. Dioda LCK sygnalizuje prawidłowy odbiór sygnału cyfrowego, a PWR obecność zasilania. Sygnał LCK wykorzystywany jest do wyciszania obwodów przetwornika C/A (bramka Schmitta UW2), gdy nie ma prawidłowego odbioru sygnału wejściowego S/PDIF.

Sygnał wejściowy I²S jest doprowadzony poprzez złącze I²S i połączony z portem szeregowym ADAU1442 (sygnały I²S: ISDI, ILRCK, IBCK). Podobnie jak w odbiorniku S/PDIF, jest możliwe zewnętrzne wyciszanie przetwornika C/A za pomocą sygnału IMUTE doprowadzonego do GPIO MP6.

Sygnał wyjściowy I²S (WSDI, WBLCK, WLRCK) o częstotliwości fs z zakresu 32...192 kHz jest doprowadzony do portu szeregowego I²S układu ADAU1442. Sygnał wyciszania WMUTE jest doprowadzony do GPIO MP6.

Układ odbiornika S/PDIF uzupełniają elementy filtrujące zasilanie. Każdy z bloków funkcjonalnych układów UW1 jest zasilany poprzez filtr LC. Rezystor RP2 ogranicza przerost amplitudy szybkich sygnałów I²S.

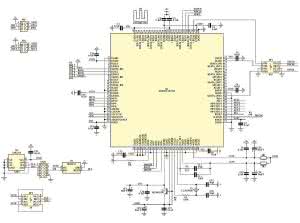

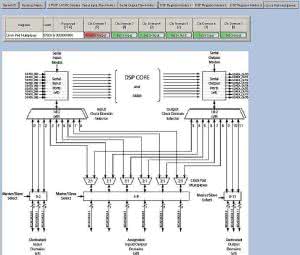

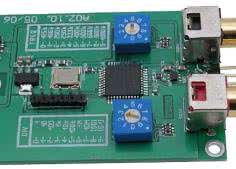

Schemat DSP zamieszczono na rysunku 3. Aplikacja procesora DSP1442 (U1) jest typowa, układ pracuje w trybie SELFBOOT. Parametry i program są przechowywane w pamięci EEPROM (U2).

Zawartość pamięci jest programowana poprzez złącze USBI za pomocą programatora USBi. Układ ADM811T (U3) zapewnia poprawny restart układów po włączeniu zasilania. Procesor DSP jest taktowany za pomocą rezonatora kwarcowego o częstotliwości 12,288 MHz. Układ ma aktywny obwód generatora sygnałowego MCLK dla przetwornika C/A.

Blok DSP jest zasilany napięciem 3,3 V. Stabilizator z tranzystorem Q1 zapewnia zasilanie 1,8 V dla rdzenia procesora DSP. Poszczególne są zasilane poprzez odpowiednie filtry LC. Do złącza MP są doprowadzone cztery cyfrowe sygnały GPIO dla zewnętrznych przycisków lub układów sygnalizujących pracę DSP. Uwaga!

GPIO ma niewielką obciążalność, więc do sterowania diodami LED należy użyć wzmacniaczy prądowych. Do złącza ADC są doprowadzone wejścia przetwornika A/C, które służą do przyłączenia potencjometrów przy "regulacji analogowej".

Każde złącze ma wyprowadzone zasilanie 3,3 V przeznaczone do zasilania zewnętrznych interfejsów GPIO. Dla rozproszenia traconej mocy procesor DSP jest wyposażony w niewielki radiator BGA.

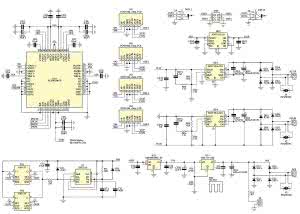

Zamianą sygnału audio z cyfrowego na analogowy zajmuje się przetwornik PCM4104. W jego strukturze zaimplementowano 4 kanały przetwornika C/A (216 kHz/24 bity) oraz elastyczny interfejs szeregowy audio. W aplikacji MegaDSP+ układ PCM4104 jest konfigurowany sprzętowo za pomocą wejść FSx i FMTx.

Sygnał audio nie jest przesyłany w standardzie I²S dopuszczającym transmisję tylko dwóch kanałów, ale w trybie TDM (Time Data Multiplexed), który upraszcza budowę interfejsu wielokanałowego przetwornika C/A, ponieważ sygnały wszystkich kanałów są multipleksowane czasowo i przesyłane tylko jedną linią danych. Przykładowe przebiegi pokazano na rysunku 4.

Schemat bloku przetwornika C/A pokazano na rysunku 5. Wejściowy sygnał TDM (DMCLK, DBCLK, DLRCK, DTDM) z portu szeregowego ADAU1442, przez rezystor RP1 jest doprowadzony do układu UD1. Wspomniana wcześniej możliwość wyciszania kanałów wyjściowych jest aktywowana sygnałem DMUTE z wyprowadzenia MP4 procesora DSP.

Przetwornik C/A wymaga sygnału zerującego po włączeniu zasilania i dlatego do wejścia 9 układu UD1 jest doprowadzony sygnał RES z bloku DSP. Analogowe sygnały VPx, VNx po konwersji są doprowadzane do modułów filtrów dolnoprzepustowych M1...M4.

Filtry wykonano na osobnych płytkach ze względu założenie jak najmniejszych wymiarów modułu MegaDSP+. Schemat ideowy filtru zamieszczono na rysunku 6. Układ filtru jest typowy i nie wymaga szerszego opisu. Zastosowany wzmacniacz operacyjny to NE5534, który w zupełności spełnia wymagania tej aplikacji.

Można oczywiście poeksperymentować z nowszymi wzmacniaczami, o lepszych parametrach. Sygnał wyjściowy z par kanałów przetwornika C/A jest doprowadzony do gniazd OUT12 i OUT34 typu Jack 3,5 mm oraz do gniazda szpilkowego OUT, do którego są dołączone wszystkie 4 kanały.

Wykaz elementówPłytka procesora Rezystory; (SMD 0805, 1%) Kondensatory: Półprzewodniki: Inne: Płytka filtru (×4 szt.) Rezystory: (SMD 0805, 1%) Kondensatory: Półprzewodniki Inne: |

Aby MegaDSP+ był rzeczywiście modułem kompletnym, uzupełniono go o drugi obwód wyciszania widoczny na schemacie bloku przetwornika na rys. 5. Składa się on z ICM555 oraz przekaźników RY1 i RY2. Jego zadaniem jest eliminowanie zakłóceń podczas załączania i wyłączania MegaDSP+.

Układ opóźnienia wykonano w oparciu o ICM555, który po upływie kilku sekund od załączenia zasilania zasila przekaźniki rozwierając wyjścia analogowe. Po zaniku zasilania wyjścia są zwierane bezzwłocznie chroniąc tor audio przed niepożądanymi zakłóceniami.

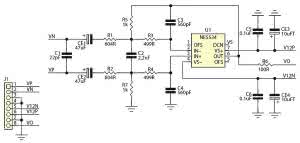

Zasilacz części cyfrowej zbudowano w oparciu o typowe układy połączone szeregowo LM1117 (US1) stabilizujący wstępnie napięcie 3,8 V oraz niskoszumny stabilizator ADP3339 (US2) dostarczający napiecie 3,3 V dla częsci cyfrowej.

Układ jest zasilany z transformatora siecioweego o napieciu wyjściowym 6 V AC i prądzie 1 A, które po wyprostowaniu w mostku Graetza złożonym z szybkich diod SK13 i filtrowaniu zasila stabilizator US1 i blok wyciszania. Transil V3 zabezpiecza układ przed szpilkami napięcia mogącymi uszkodzić US1. Ze względu na traconą moc US1 wymaga zastosowania niewielkiego radiatora.

Złacze LP służy do dołaczenia diody LED sygnalizującej załączenie zasilania. Zasilacz bloków analogowych dostarcza napięć V12N/V12P do zasilania filtrów LPF oraz V5A do zasilania części analogowej PCM4104. Zasilacz jest oparty o niskoszumne stabilizatory typu ADP-7104-ADJ (dla V12N/V12P, ±12 V) w wersji o regulowanym napięciu wyjściowym, Napięcie jest ustalane za pomocą dzielników rezystorowych RD1...RD6.

Zasilacz napięcia V5A (+5 V) wykonano na bazie układu ADP7102-5 o ustalonym na stałe 5-woltowym napięciu wyjściowym. Układ jest zasilany z transformatora 2×12 V AC/0,5 A. Jego napięcie po wyprostowaniu w mostkach Graetza złożonych z szybkich diod RS1D i filtrowaniu zasila stabilizatory UD3, UD4. Transile V1 i V2 zabezpieczają układ przed szpilkami napięcia. Stabilizator UD2 jest zasilany z napięcia V12P.

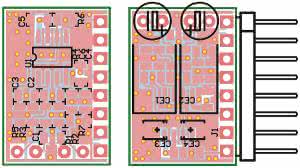

Urządzenie zmontowano na dwustronnej płytce drukowanej, której schemat montażowy pokazano na rysunku 7 (moduł procesora) i rysunku 8 (moduł filtru). Sposób montażu jest typowy i nie wymaga opisu - jedynie należy sprawdzić jego poprawność.

Szczególną uwagę należy zwrócić na prawidłowe przylutowanie padów termicznych stabilizatorów i procesora DSP. Układ nie wymaga uruchamiania, zlutowany prawidłowo ze sprawnych elementów jest gotowy do oprogramowania.

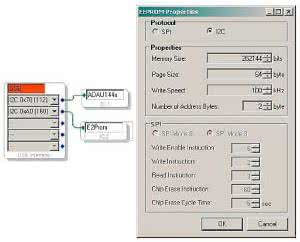

Konfiguracja i programowanie odbywa się za pomocą środowiska graficznego Sigma Studio i programatora USBi. Konfiguracja sprzętowa modułu jest stała i może być wykorzystana jako szablon we własnych aplikacjach.

Na rysunku 9 pokazano konfigurację programatora USBi, procesora DSP i pamięci EEPROM. Konfigurację sprzętową portów szeregowych DSP przedstawia rysunek 10. Porty Serial Input2 (I²S), Serial Input7 (SPDIF) są ustawione standardowo jako slave I²S (są odbiornikami, nie generują sygnałów I²S).

Port wyjściowy Serial8 pracuje jako Master (generuje sygnały BCLK/LRCK/SDO). Domeną zegarową jest sygnał zegara głównego DSP 192 kHz. Port pracuje w trybie multipleksowanym TDM4, zgodnie z konfiguracją sprzętową przetwornika PCM4104.

Ze względu na asynchroniczną pracę wejść szeregowych, przed obróbką audio jest konieczne sprowadzenie sygnałów do wspólnej domeny zegarowej. Do tego celu służy wbudowany w ADAU1442 blok 8 stereofonicznych konwerterów ASRC (1445 ma tylko dwa).

Sygnały portów szeregowych doprowadzone są do ASRC z dowolnymi częstotliwościami próbkowania. Po konwersji do częstotliwości DSP dostępne są do obróbki. Konfigurację bloków ASRC pokazano na rysunku 11. W zakładce konfigurowany jest też port wyjściowy, który z racji trybu TDM zajmuje dwa kanały portów szeregowych (#8, #9).

Kolejną konieczną do wykonania konfiguracją jest ustawienie zegara DSP i określenie funkcji wyprowadzeń GPIO (rysunek 12). Układ ADAU1442 pracuje z częstotliwością próbkowania 192 kHz.

Wejścia GPIO są używane do wyciszania WMUTE, IMUTE, do wyboru wejść szeregowych SEL i dlatego pracują w trybie wejść cyfrowych, z parametrem debounce=20 ms.

Wejście sygnału wyciszania DMUTE pracuje w trybie wyjścia cyfrowego z podwieszeniem. Sygnał regulacji głośności jest podawany na GPIO pracujące w trybie analogowym. Pozostałe dostępne na złączach MP/ADC należy skonfigurować zależnie od potrzeb danej aplikacji.

Następnie należy uaktywnić wszystkie potrzebne sygnały zegarowe (MCLK: Adc, DSP Core, ASRC1, Serial In, OUT) zgodnie z rysunkiem 13 oraz określić domeny In/Out sygnałow zegarowych dla portów szeregowych, jak na rysunku 14.

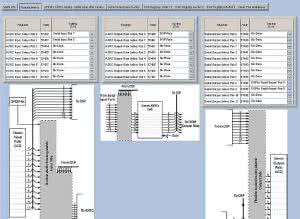

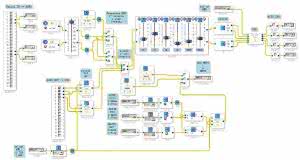

Po określeniu konfiguracji sprzętowej, można zabrać się za wykonanie programu dla DSP. Jako projekt przykładowy zrealizowano dwuwejściowy, cyfrowy przedwzmacniacz z korektorem i zwrotnicą dla dwudrożnego stereofonicznego aktywnego systemu audio.

Schemat aplikacji zamieszczono na rysunku 15. Sygnały wejściowe z portów I²S i SPDIF są doprowadzone do ASRC. Po konwersji częstotliwości próbkowania (odobnej dla każdego sygnału) doprowadzone są do multipleksera wejść sterowanego z wyprowadznia MP11.

Stąd - poprzez multiplekser źródeł Gen/Serial, korektor graficzny, zwrotnicę dwudrożną, blok wspólnej regulacji głośności (potencjometr VOL pin MP0) - do wyjść sterujących przetwornik C/A.

Schemat zawiera sporo elementów nadmiarowych, ale bardzo przydatnych podczas uruchamiania. Każdy sygnał kanału C/A może być wyciszony blokiem MUTEx. Dostępny jest generator testowy wybierany multiplekserem Source=Gen.

Generator ma regulowany poziom oraz dwie częstotliwości + wyciszenie. (Uwaga na odpowiedni poziom sygnału podczas testów!). Za wyciszanie C/A odpowiada blok logiki przełączający odpowiednie sygnały na wyście DMUTE MP4. Wbudowany multiplekser pozwala na sterowanie ręczne wyciszaniem.

Podczas testów jest możliwe jest natychmiastowe sprawdzenie działania układu za pomocą programatora USBi. Przed zaprogramowaniem pamięci EEPROM należy tylko usunąć lub ustawić odpowiednio testowe bloki aplikacji i układ po restarcie będzie już samodzielnie realizował "narysowane" zadanie.

Pozostaje życzyć powodzenia w tworzeniu własnych projektów. W przypadku problemów pomocne może być forum ez.analog. com (dział Sigma DSP).

Adam Tatuś, EP

Zaloguj

Zaloguj