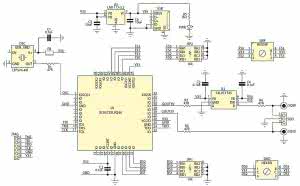

Schemat ideowy generatora pokazano na rysunku 1. Zastosowanie układu programowalnego idealnie wpisuje się w realizowaną przez generator funkcję znacznie upraszczając jego budowę. Generator jest taktowany oscylatorem OSC o częstotliwości 4 MHz.

W strukturze U1 zdefiniowano dwa programowane dzielniki częstotliwości. Pierwszy, określający podział dziesiętny 1:1, aż do 1:10M. Drugi, określający częstotliwość w sekwencji: 125-166-200-250-333-400-500-666—800-1000. Dzięki możliwej kombinacji podziału i częstotliwości generator pokrywa szeroki zakres 0,0125 Hz...1 MHz.

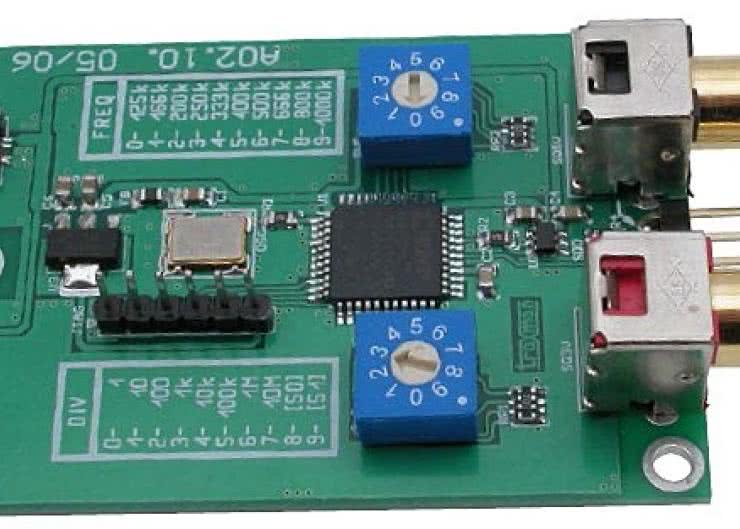

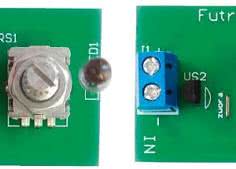

Wypełnienie przebiegu równe jest 50% niezależnie od generowanej częstotliwości. Żądaną częstotliwość i podział ustala się nastawnikami binarnymi SWF/SWD.

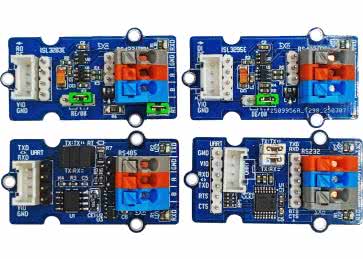

Dwie ostatnie pozycje przełącznika SWD (8/9) umożliwiają zadanie poziomu logicznego (0 lub 1) na wyjściu generatora. Sygnał wyjściowy jest doprowadzony do gniazd RCA: SQ3V (logika 3,3 V) oraz po konwersji poziomów przez U2 do gniazda SQ5V (logika 5 V). Sygnały powielone są na złączu szpilkowym SDO.

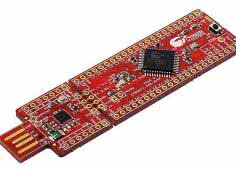

Układ zasilany jest z 5 V poprzez gniazdo USB micro, LED sygnalizuje obecność zasilania, U3 zapewnia napięcie 3,3 V dla CPLD. Za względu na niewielki pobór mocy możliwe jest zasilanie układu z portu USB, ładowarki telefonu lub Power Banku.

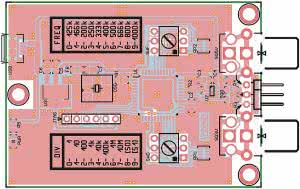

Układ zmontowany jest na niewielkiej dwustronnej płytce drukowanej. Format płytki zgodny jest z opisanymi wcześniej generatorami SPDIF_Gen i Audio_Gen tworząc niewielki uzupełniający się generator uniwersalny. Montaż nie wymaga opisu. Po zaprogramowaniu układu (SQ_gen.jed) podłączeniu zasilania należy tylko sprawdzić obecność sygnałów na gniazdach wyjściowych.

Adam Tatuś, EP

Zaloguj

Zaloguj