Mostki i interfejsy Ethernetowe cz.1. Interfejsy PHY i mikrokontrolery z MAC

01 grudnia 2009

Aplikacje wykorzystujące Ethernet podbijają rynek, co z jednej

strony wynika z rosnących potrzeb użytkowników i coraz

łatwiejszego dostępu do sieci, z drugiej - ułatwia to coraz większa

liczba coraz tańszych mikrokontrolerów wyposażonych w interfejsy

sieciowe oraz coraz częściej bezpłatne oprogramowanie realizujące

m.in. funkcje stosów protokołów sieciowych.

Przegląd dostępnych konstruktorom rozwiązań sprzętowych

przedstawiamy w artykule.

66 ELEKTRONIKA PRAKTYCZNA 12/2009

Wybór konstruktoraWybór konstruktora

(MAC), która odpowiada m.in. za selekcję

i adresowanie danych przesyłanych pomię-

dzy urządzeniami dołączonymi do sieci.

Ponieważ w artykule zajmiemy się przede

wszystkim interfejsami sieci kablowych,

bezprzewodowe rozszerzenia standardu

IEEE802 zostawimy do omówienia w kolej-

nych wydaniach EP.

Na rys. 1 pokazano warstwowy model

sieci OSI ISO z zaznaczonymi warstwa-

mi obsługiwanymi przez scalone interfejsy

sieciowe PHY i MAC. Jak widać dostępne

współcześnie układy scalone realizują funk-

Mostki i interfejsy

Ethernetowe (1)

Interfejsy PHY

i mikrokontrolery z MAC

Aplikacje wykorzystujące Ethernet podbijają rynek, co z jednej

strony wynika z rosnących potrzeb użytkowników i coraz

łatwiejszego dostępu do sieci, z drugiej ? ułatwia to coraz większa

liczba coraz tańszych mikrokontrolerów wyposażonych w interfejsy

sieciowe oraz coraz częściej bezpłatne oprogramowanie realizujące

m.in. funkcje stosów protokołów sieciowych.

Przegląd dostępnych konstruktorom rozwiązań sprzętowych

przedstawiamy w artykule.

Jedynym liczącym się obecnie w świe-

cie standardem lokalnych sieci do przesyłu

danych jest Ethernet. Historia tego standar-

du sięga początku lat ?70 (jest to opracowa-

nie firmy Xerox), znany nam współcześnie

10BASE-T wprowadzono na rynek na po-

czątku lat ?90.

Kablowy Ethernet jest utożsamiany ze

standardem IEEE802.3, który składa się z ze-

stawu definicji określających budowę i dzia-

łanie fizycznej warstwy interfejsu wymiany

danych (PHYsical layer), funkcję i sposób

działania warstwy łącza (Data Link lay-

er) oraz podwarstwy Media Access Control

Dodatkowe materiały na CD i FtP:

host: ep.com.pl, user: 12235, pass: 60u61csy

Dodatkowe materiały

na CD i FTP

67ELEKTRONIKA PRAKTYCZNA 12/2009

Mostki i interfejsy Ethernetowe

Rolą układów MAC jest wysokopozio-

mowa obróbka danych odbieranych z PHY

i wysyłanych przez PHY (w tym tworzenie,

dekompozycja i synchronizacja ramek,

sterowanie przepływem danych, wykrywanie

i obsługa błędów).

Rolą PHY jest formowanie i transfer (w oby-

dwu kierunkach) jednostek danych w spo-

sób dostosowany do możliwości wykorzysty-

wanego medium transmisyjnego.

cje dwóch dolnych warstw modelu ISO,

pozostałe warstwy muszą być realizowane

programowo.

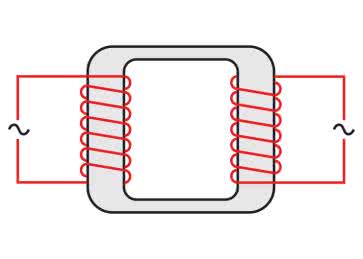

Warto pamiętać, że istotnymi elemen-

tami warstwy fizycznej są jeszcze transfor-

matory separujące interfejsy sieciowe, za-

pewniające przy tym transfer danych z od-

powiednią prędkością oraz gniazda ? dość

często gniazda są integrowane z transforma-

torami w jednej obudowie. Na rys. 2 poka-

zano typowy (choć nie jedyny stosowany

w praktyce) sposób włączenia transforma-

torów separujących w obwody wejściowe

układu PHY.

Interfejsy komunikacyjne układów

MAC i PHY

Zapewnienie współpracy pomiędzy

poszczególnymi warstwami stosu wymaga

opracowania przez programistę odpowied-

nich interfejsów lub (np. w przypadku komu-

nikacji pomiędzy warstwami IP i DataLink)

programowej obsługi zestawu rejestrów,

w jakie jest wyposażony MAC. Także ukła-

dy ulokowane w najniższej warstwie stosu

? MAC i PHY ? muszą się ze sobą komuni-

rys. 1. Warstwowy model sieci osI Iso z zaznaczonymi warstwami obsługiwanymi

przez scalone interfejsy sieciowe PHy i MaC

rys. 2. Jeden ze sposobów włączenia transformatorów separujących w obwody

wejściowe układu PHy

rys. 3. Dzięki interfejsowi komunikacyjnemu MII blok MaC może komunikować się

z praktycznie dowolnym PHy

68 ELEKTRONIKA PRAKTYCZNA 12/2009

Wybór konstruktora

Tab. 1. Zestawienie prędkości transferu

danych za pomocą wybranych inter-

fejsów zapewniających komunikację

pomiędzy PHY i MAC

Interfejs

Liczba

bitów

prze-

syłana

w jednym

takcie

Prędkość

transmisji

[Mb/s]

Prędkość

transmisji

[MB/s]

MII 4 100 12,5

RMII 2 100 12,5

SMII 1 100 12,5

GMII 8 1000 12,5

RGMII 4 1000 125

SGMII 2 1000 125

XGMII 32 10000 1250

XAUI 4 10000 1250

rys. 6. typowe połączenie pomiędzy MaC i PHy z wykorzystaniem interfejsu sMII

rys. 4. typowe połączenie pomiędzy MaC i PHy z wykorzysta-

niem interfejsu MII

rys. 5. typowe połączenie pomiędzy MaC i PHy z wykorzysta-

niem interfejsu rMII

kować, do czego służą specjalne interfejsy

oparte na Media Independent Interface zna-

nym także pod akronimem MII. Idea tego in-

terfejsu polega na uniezależnieniu warstwy

obsługującej medium przesyłowe od prze-

syłanych danych, dzięki czemu zastąpienie

miedzianych kabli interfejsem radiowym

lub światłowodem nie wymaga praktycznie

żadnej ingerencji w interfejs komunikacyjny,

poza ? co oczywiste ? wymianą układu PHY,

który musi być dopasowany do charakteru

medium (rys. 3).

Na rys. 4 pokazano typowe połączenie

pomiędzy MAC i PHY z wykorzystaniem

interfejsu MII, który w jednym takcie zega-

ra synchronizującego transmisję przesyła 4

bity danych. Taki sposób transferu wymusza

częstotliwość taktowania interfejsu 25 MHz,

co pozwala uzyskać wypadkową prędkość

transmisji 100 Mb/s (tab. 1).

Ponieważ liczba linii niezbędnych do

transferu danych z wykorzystaniem inter-

fejsu MII jest duża (łącznie 16), a linie GPIO

mikrokontrolerów były do niedawna bardzo

kosztowne, opracowano nieco zmodyfikowa-

ny standard RMII (Reduced MII), w którym

zmniejszono liczbę linii sterujących, a dane

są przesyłane paczkami po 2 bity (rys. 5).

Wymusiło to zwiększenie częstotliwości

taktowania transferu danych z 25 MHz do

50 MHz.

Dalszą redukcję liczby niezbędnych wy-

prowadzeń zaproponowali twórcy interfejsu

SMII (Serial MII ? rys. 6), który jest stosowa-

ny jako opcjonalny w niektórych układach

PHY i mikrokontrolerach z wbudowanym

MAC.

Na rys. 4...6 zaznaczono na czerwono

dwie linie interfejsu MDIO (Management

Data Input/Output), który służy do konfigu-

racji i diagnostyki układów PHY. Zazwyczaj

jest on obsługiwany bezpośrednio przez

MAC i nie wymaga interwencji ze strony

aplikacji użytkownika (poza obsługą stosu

komunikacyjnego).

Pozostałe interfejsy wymienione w tab. 1

są rzadko wykorzystywane w aplikacjach

mikrokontrolerowych, przede wszystkim ze

względu na brak realnej możliwości obsłuże-

nia dużej liczby danych przesyłanych przez

tak szybkie interfejsy sieciowe.

Mostki PHY do sieci

10/100/1000 Mb/s

Ponieważ coraz większa liczba tanich

mikrokontrolerów i mikroprocesorów jest

wyposażana w bloki MAC (tab. 2), do budo-

wy systemów sieciowych wystarczy zasto-

sowanie interfejsu PHY. Układy tego typu

oferuje wiele firm (tab. 3), a ich możliwości

funkcjonalne umożliwiają realizację także

bardzo zaawansowanych, także wielokanało-

wych aplikacji sieciowych.

69ELEKTRONIKA PRAKTYCZNA 12/2009

Mostki i interfejsy Ethernetowe

Tab. 2. Wybrane mikrokontrolery wyposażone w bloki MAC lub MAC i PHY

Typ Rdzeń Kategoria Producent Wyposażenie

AX11001 8051 mC Asix MAC, PHY

AX11005 8051 mC Asix MAC, PHY

AX11015 8051 mC Asix MAC, PHY

AX11025 8051 mC Asix MAC, PHY

AT32AP7000 AVR32 mP Atmel 2×MAC, MII, RMII

AT32UC3A0128 AVR32 mC Atmel MAC, MII, RMII

AT32UC3A0256 AVR32 mC Atmel MAC, MII, RMII

AT32UC3A0512 AVR32 mC Atmel MAC, MII, RMII

AT32UC3A1128 AVR32 mC Atmel MAC, MII, RMII

AT32UC3A1256 AVR32 mC Atmel MAC, MII, RMII

AT32UC3A1512 AVR32 mC Atmel MAC, MII, RMII

AT91RM9200 ARM920T mP Atmel MAC, MII, RMII

AT91SAM9260 ARM926EJ-S mP Atmel MAC, MII, RMII

AT91SAM9261 ARM926EJ-S mP Atmel MAC, MII, RMII

AT91SAM9263 ARM926EJ-S mP Atmel MAC, MII, RMII

AT91SAM9G20 ARM926EJ-S mP Atmel MAC, MII, RMII

AT91SAM9G45 ARM926EJ-S mP Atmel MAC, MII, RMII

AT91SAM9XE128 ARM926EJ-S mC Atmel MAC, MII, RMII

AT91SAM9XE256 ARM926EJ-S mC Atmel MAC, MII, RMII

AT91SAM9XE512 ARM926EJ-S mC Atmel MAC, MII, RMII

AT91SAM7X128 ARM7TDMI mP Atmel MAC, MII, RMII

AT91SAM7X256 ARM7TDMI mP Atmel MAC, MII, RMII

AT91SAM7X512 ARM7TDMI mP Atmel MAC, MII, RMII

AT91SAM7XC128 ARM7TDMI mP Atmel MAC, MII, RMII

AT91SAM7XC256 ARM7TDMI mP Atmel MAC, MII, RMII

AT91SAM7XC512 ARM7TDMI mP Atmel MAC, MII, RMII

EP9301 ARM920T mP Cirrus Logic MAC, MII

EP9302 ARM920T mP Cirrus Logic MAC, MII

EP9307 ARM920T mP Cirrus Logic MAC, MII

EP9312 ARM920T mP Cirrus Logic MAC, MII

EP9315 ARM920T mP Cirrus Logic MAC, MII

eCOG1X8A5 eCOG1 mC Cyan MAC, MII

eCOG1X9A5 eCOG1 mC Cyan MAC, MII

eCOG1X10B5 eCOG1 mC Cyan MAC, MII

eCOG1X14B5 eCOG1 mC Cyan MAC, MII

eCOG1X10Z5 eCOG1 mC Cyan MAC, MII

eCOG1X14Z5 eCOG1 mC Cyan MAC, MII

MC9S12NE64 HCS12 mC Freescale MAC+PHY

MCF51CN128 ColdFire V1 mC Freescale MAC, MII

MCF520X ColdFire V2 mP Freescale MAC, MII

MCF523x ColdFire V2 mP Freescale MAC, MII

MCF527X ColdFire V2 mP Freescale 2×MAC, MII

MCF528X ColdFire V2 mC Freescale MAC, MII

MCF532X ColdFire V3 mP Freescale MAC, MII

MCF537X ColdFire V3 mP Freescale MAC, MII

MCF547X ColdFire V4e mP Freescale 2×MAC, MII

MCF548X ColdFire V4e mP Freescale 2×MAC, MII

MCF5223X ColdFire V2 mC Freescale MAC, PHY

MCF5225X ColdFire V2 mC Freescale MAC, MII

MCF5445X ColdFire V4 mP Freescale 2×MAC, MII

i.MX27 ARM926EJ-S mP Freescale MAC, MII

i.MX27L ARM926EJ-S mP Freescale MAC, MII

i.MX35x ARM1136JF-S mP Freescale MAC, MII

i.MX37 ARM1176JZF-S mP Freescale MAC, MII

i.MX512 Cortex-A8 mP Freescale MAC, MII

i.MX51x Cortex-A8 mP Freescale MAC, MII

DS80C400 8051 mC Maxim MAC, MII

DS80C410 8051 mC Maxim MAC, MII

DS80C411 8051 mC Maxim MAC, MII

PIC18F66 PIC18 mC Microchip MAC, PHY

PIC18F67 PIC18 mC Microchip MAC, PHY

70 ELEKTRONIKA PRAKTYCZNA 12/2009

Wybór konstruktora

Współczesne układy PHY są przystoso-

wane do pracy niskonapięciowej (nawet od

1,5 V), zapewniają maksymalne zautomaty-

zowanie transakcji sieciowych, automatycz-

nie wykrywają rodzaj dołączonego do gniaz-

da kabla (i potrafią samoczynnie przełączyć

pary kanałów), zachowują przy tym zgod-

ność z funkcjonalnymi standardami IEEE,

dzięki czemu ich protokołowa kompatybil-

ność jest dość wysoka.

W zestawieniu pokazanym w tab. 3 znaj-

duje się spora liczba układów PHY przysto-

sowanych do pracy w sieciach Ethernet 10,

100 lub 1000 Mb/s, przy czym warto zwrócić

uwagę na fakt, że żaden z mikrokontrolerów

i niewiele mikroprocesorów jest w stanie

w pełni wykorzystać tak (potencjalnie) szyb-

kie transfery danych, nawet z wykorzysta-

niem DMA. Dobierając układ PHY do wła-

snej aplikacji lepiej jest kierować się łatwą

dostępnością transformatorów separujących

prawidłowo współpracujących z dostępny-

mi układami zamiast polegać na fascyna-

cjach dużymi liczbami.

Podsumowanie

Przedstawione w artykule układy: mi-

krokontrolery wyposażone w bloki MAC

lub MAC+PHY oraz układy PHY realizują

funkcje 2 z 7 warstw niezbędnych do ob-

sługi sieci. Wyższe warstwy są obsługiwane

programowo i w większości przypadków

producenci mikrokontrolerów dostarczają

niezbędne oprogramowanie bezpłatnie, choć

czasami w nieco okrojonych wersjach. Warto

na bieżąco śledzić strony producentów mi-

krokontrolerów, bo w dość szybkim tempie

zwiększa się liczba dostępnych bezpłatnie

stosów sieciowych.

Za miesiąc...

...przedstawimy kolejne grupy układów

i modułów przeznaczonych do stosowania

w interfejsach sieciowych: kompletne in-

terfejsy sieciowe MAC+PHY, zasilacze PoE

oraz zintegrowane moduły interfejsów sie-

ciowych oraz narzędzia do ich aplikowania.

Andrzej Gawryluk

Tab. 2. c.d.

Typ Rdzeń Kategoria Producent Wyposażenie

PIC18F86 PIC18 mC Microchip MAC, PHY

PIC18F87 PIC18 mC Microchip MAC, PHY

PIC18F96 PIC18 mC Microchip MAC, PHY

PIC18F97 PIC18 mC Microchip MAC, PHY

LPC1758 Cortex-M3 mC NXP MAC, RMII

LPC1764 Cortex-M3 mC NXP MAC, RMII

LPC1766 Cortex-M3 mC NXP MAC, RMII

LPC1768 Cortex-M3 mC NXP MAC, RMII

LH79524N ARM720T mP NXP MAC, MII

LH79525N ARM720T mP NXP MAC, MII

LPC236x ARM7TDMI mC NXP MAC, RMII

LPC237x ARM7TDMI mC NXP MAC, RMII

LPC2388 ARM7TDMI mC NXP MAC, RMII

LPC2458 ARM7TDMI mC NXP MAC, MII, RMII

LPC246x ARM7TDMI mC NXP MAC, MII, RMII

LPC247x ARM7TDMI mC NXP MAC, MII, RMII

LPC3240 ARM926E-J mC NXP MAC, MII, RMII

LPC3240 ARM926E-J mC NXP MAC, MII, RMII

NUC710 ARM7TDMI mP Nuvoton MAC, RMII

NUC740 ARM7TDMI mP Nuvoton 2×MAC, RMII

NUC745 ARM7TDMI mP Nuvoton MAC, RMII

NUC910 ARM926E-J mP Nuvoton MAC, RMII

NUC920 ARM926E-J mP Nuvoton MAC, RMII

NUC945 ARM926E-J mP Nuvoton MAC, RMII

NUC950 ARM926E-J mP Nuvoton MAC, RMII

NUC960 ARM926E-J mP Nuvoton MAC, RMII

Rabbit 5000 BD mP Rabbit MAC, MII

Rabbit 4000 BD mP Rabbit MAC, PHY

Rabbit 3000 BD mC Rabbit MAC, MII

STM32F107 Cortex-M3 mC ST MAC, MII, IEEE1588

STR912 ARM966E-S mC ST MAC, MII

AM3505 Cortex-A8 mP TI MAC, RMII

AM3517 Cortex-A8 mP TI MAC, RMII

LM3S61xx Cortex-M3 mC TI MAC, PHY

LM3S64xx Cortex-M3 mC TI MAC, PHY

LM3S6537 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S66xx Cortex-M3 mC TI MAC, PHY

LM3S6730 Cortex-M3 mC TI MAC, PHY

LM3S6753 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S69xx Cortex-M3 mC TI MAC, PHY

LM3S6950 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S8530 Cortex-M3 mC TI MAC, PHY

LM3S8538 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S8630 Cortex-M3 mC TI MAC, PHY

LM3S8730 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S873x Cortex-M3 mC TI MAC, PHY

LM3S8930 Cortex-M3 mC TI MAC, PHY

LM3S8933 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S8938 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S8962 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S8970 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S8971 Cortex-M3 mC TI MAC, PHY

LM3S979x Cortex-M3 mC TI MAC, PHY

LM3S9997 Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S9B9x Cortex-M3 mC TI MAC, PHY, IEEE1588

LM3S9L97 Cortex-M3 mC TI MAC, PHY, IEEE1588

EZ80F91NAA eZ80 mP Zilog MAC, MII

EZ80F916 eZ80 mP Zilog MAC, MII

BD ? brak danych

71ELEKTRONIKA PRAKTYCZNA 12/2009

Mostki i interfejsy Ethernetowe

Tab. 3. Zestawienie PHY wybranych z ofert największych producentów

Typ Producent Liczba portów MII RMII SMII Prędkość transmisji [Mb/s] AutoMDIX Inne

BCM5221 Broadcom 1 ? + ? 10/100 +

BCM5222 Broadcom 2 + ? ? 10/100 +

BCM5241 Broadcom 1 + ? ? 10/100 +

BCM5208R Broadcom 4 + ? ? 10/100 +

BCM5228 Broadcom 8 ? + + 10/100 +

BCM5238 Broadcom 8 ? ? + 10/100 + SSMII

BCM5248 Broadcom 8 ? ? + 10/100 + SSMII

CS8900 Cirrus 1 ? ? ? 10 ?

CS8952 Cirrus 1 + ? ? 10/100 ?

DM9161B Davicom 1 + + ? 10/100 + GPSI

DM9161BI Davicom 1 + + ? 10/100 + GPSI

DM9161A Davicom 1 + + ? 10/100 + GPSI

DM9161 Davicom 1 + + ? 10/100 + GPSI

DM9801 Davicom 1 + ? ? 1 ? Home Phoneline Network

ICS1893 IDT 1 + ? ? 10/100 +

DP83848C NS 1 + + ? 10/100 + SNI

DP83848H NS 1 + + ? 10/100 +

DP83848I NS 1 + + ? 10/100 + SNI

DP83848J NS 1 + + ? 10/100 +

DP83848K NS 1 + + ? 10/100 +

DP83848M NS 1 + + ? 10/100 +

DP83848T NS 1 + + ? 10/100 +

DP83640 NS 1 + + ? 10/100 + IEEE1588, FX

DP83849C NS 2 + + ? 10/100 +

DP83849D NS 2 + + ? 10/100 + FX

DP83849I NS 2 + + ? 10/100 +

DP83865 NS 1 + 10/100/1000 + GMII, RGMII

KSZ9021GQ Micrel 1 + 10/100/1000 + GMII

KSZ9021RL Micrel 1 ? ? ? 10/100/1000 + RGMII

KSZ9021GN Micrel 1 + ? ? 10/100/1000 + GMII

KSZ8041NL Micrel 1 + + ? 10/100 +

KSZ8041TL Micrel 1 + + + 10/100 +

KSZ8001L Micrel 1 + + + 10/100 +

KSZ8001SL Micrel 1 + + + 10/100 +

KSZ8721 Micrel 1 + + ? 10/100 +

78Q2120C Teridian 1 + ? ? 10/100 ?

78Q2123 Teridian 1 + ? ? 10/100 +

78Q2133 Teridian 1 + ? ? 10/100 +

PHY11G Infineon 1 BD BD BD 10/100/1000 BD

PHY22F Infineon 2 BD BD BD 10/100/1000 BD

88E3015 Marvell 1 + ? ? 10/100 + RGMII

88E3016 Marvell 1 ? ? ? 10/100 + RGMII

88E3018 Marvell 1 + ? ? 10/100 + RGMII

88E3082 Marvell 8 ? + + 10/100 + SSSMII

88E3083 Marvell 8 ? ? + 10/100 + SSSMII

88E1111 Marvell 1 ? ? ? 10/100/1000 + GMII

88E1121 Marvell 2 ? ? ? 10/100/1000 + RGMII

88E1141 Marvell 4 ? ? ? 10/100/1000 + GMII, RGMII

RTL8201BL Realtek 1 + ? ? 10/100 ? SNI

RTL8201CL Realtek 1 + ? ? 10/100 ? SNI

RTL8201CP Realtek 1 + ? ? 10/100 ? SNI

RTL8201N Realtek 1 + + ? 10/100 + SNI

RTL8201DL Realtek 1 + + ? 10/100 + SNI

RTL8208C Realtek 8 ? + + 10/100 + SSSMII

RTL8211BN Realtek 1 + ? ? 10/100/1000 + RGMII/GMII

RTL8212F Realtek 2 + ? ? 10/100/1000 + SGMII/RGMII/GMII

RTL8214 Realtek 4 ? ? ? 10/100/1000 + RSGMII

SiS196 SiS 1 ? ? ? 10/100/1000 + GMII. RGMII

LAN8710 SMSC 1 + + ? 10/100 +

LAN8720 SMSC 1 ? + ? 10/100 +

LAN8187 SMSC 1 + + ? 10/100 +

LAN88710 SMSC 1 + + ? 10/100 +

STE100P ST 1 + ? ? 10/100 ?

TLK100 TI 1 + ? ? 10/100 +

BD ? brak danych

Zobacz więcej w kategorii Wybór konstruktora

Zaloguj

Zaloguj