SPI

Nieskomplikowanym, a jednocześnie bardzo szybkim interfejsem szeregowym, działającym w sposób synchroniczny, jest SPI (ang. Serial Peripheral Interface). Interfejs ten jest przeznaczony do przesyłania danych na krótkie odległości, zwykle pomiędzy mikrokontrolerami a układami peryferyjnymi, w obrębie jednego systemu wbudowanego. SPI korzysta z architektury master-slave, w której urządzenie nadrzędne (master) koordynuje komunikację z jednym lub większą liczbą urządzeń podrzędnych (slave), sterując sygnałami zegara i wyboru układu. W zależności od konfiguracji SPI może działać w trybie full-duplex lub half-duplex.

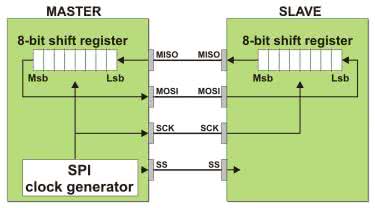

Interfejs SPI zawiera cztery charakterystyczne linie sygnałowe:

- MOSI (Master Out Slave In) – linia umożliwiająca urządzeniu master wysyłanie danych do slave’a, czasami oznaczana jako SDI w urządzeniu slave,

- MISO (Master In Slave Out) – linia umożliwiająca urządzeniom podrzędnym wysyłanie danych do urządzenia nadrzędnego, czasami oznaczana jako SDO w urządzeniu slave,

- SCLK (Serial Clock) – sygnał zegara taktującego transmisję, czasami oznaczany jako SCK,

- SS (Slave Select) – linia umożliwiająca urządzeniu nadrzędnemu wybranie urządzenia podrzędnego, do którego mają zostać wysłane dane. Czasami oznaczana jako CS w urządzeniu slave.

Podstawowa implementacja interfejsu SPI została pokazana na rysunku 1.

Zalety

• Duża szybkość transmisji, znacznie szybsza niż w I²C czy UART.

• Nieskomplikowana budowa i działanie.

• Jednoczesna komunikacja w obu kierunkach (full-duplex).

• Elastyczność konfiguracji (tryb pracy, rozmiar słowa danych, prędkość komunikacji).

• Możliwość podłączenia wielu urządzeń slave przez niezależne linie SS.

Wady

• Komunikacja tylko na niewielkie odległości – w obrębie jednego urządzenia.

• Układ slave nie może zainicjować transmisji, układ master zawsze decyduje o rozpoczęciu/zakończeniu komunikacji.

• Brak standaryzacji elektrycznej – napięcia, poziomy logiczne czy tryby pracy mogą się różnić pomiędzy układami różnych producentów.

• Każdy układ slave wymaga osobnej linii SS – przy dużej liczbie układów może to komplikować konstrukcję urządzenia.

Wiele urządzeń z interfejsem SPI

Interfejs SPI może komunikować się z wieloma urządzeniami podrzędnymi w konfiguracji standardowej (multidrop) lub szeregowej/łańcuchowej (daisy chain).

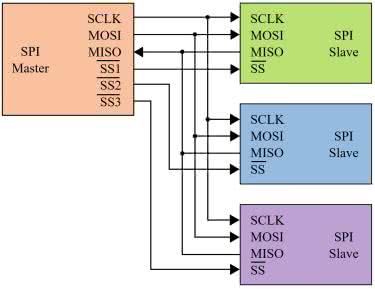

W konfiguracji multidrop do każdego układu slave doprowadzony jest niezależny sygnał aktywujący SS, a układ master wybiera tylko jeden z układów podrzędnych w danej chwili. Pozostałe linie – MOSI, MISO i SCLK – są współdzielone przez wszystkie dołączone układy. Ponieważ wyprowadzenia MISO urządzeń podrzędnych są ze sobą połączone, muszą być wyjściami trójstanowymi, czyli normalnie działają w trybie wysokiej impedancji i nie oddziałują na magistralę, a gdy urządzenie zostanie wybrane, przełączają się w tryb wyjścia cyfrowego (push-pull). Schemat połączenia w konfiguracji multidrop został pokazany na rysunku 2.

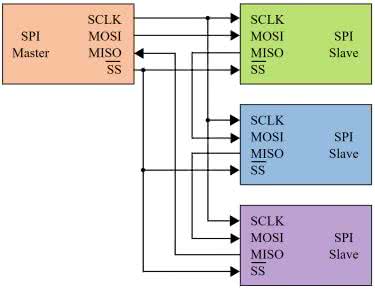

Niektóre układy slave wyposażone w interfejs SPI mogą być połączone w konfiguracji szeregowej, w której wyjście pierwszego układu slave (MISO) jest połączone z wejściem kolejnego układu slave (MOSI) i analogicznie wygląda połączenie kolejnych układów podrzędnych. Wyjście danych (MISO) ostatniego układu slave trafia do wejścia urządzenia master. Taki układ pracy można porównać do połączenia rejestrów szeregowych w jeden dłuższy łańcuch. Dane z wejścia łańcucha przemierzają cyklicznie każde jego ogniwo, zatem odbiorca danych musi być zdefiniowany w treści ramki. W konfiguracji szeregowej wymagana jest tylko jedna linia SS, która aktywuje cały łańcuch urządzeń – rysunek 3.

Transmisja danych

Komunikacja poprzez SPI rozpoczyna się, gdy urządzenie master ustawi stan aktywny na wybranym wyjściu SS – zwykle jest to logiczne 0. Następnie w kolejnych okresach sygnału zegarowego wystawiane są kolejne bity danych na wyjście MOSI. Interfejs SPI może działać w trybie full-duplex, zatem zarówno urządzenie master, jak i slave mogą wysyłać dane w tym samym czasie za pośrednictwem linii MOSI i MISO.

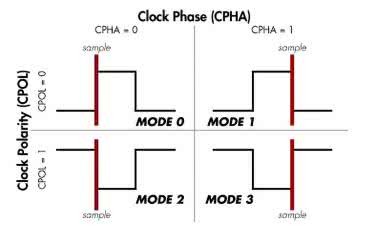

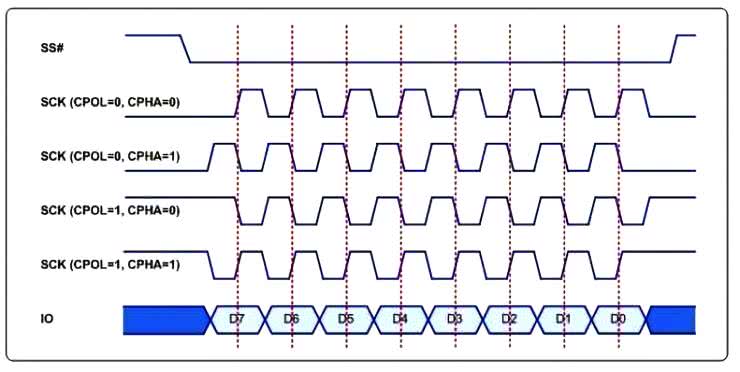

Sygnał zegarowy na linii SCLK synchronizuje przesuwanie i próbkowanie danych, więc prędkość przesyłania informacji jest określana przez częstotliwość sygnału zegarowego. Interfejs SPI pozwala na skonfigurowanie polaryzacji sygnału zegarowego (CPOL), czyli poziomu logicznego w stanie bezczynności oraz jego fazy (CPHA), czyli zbocza, na którym będzie wykonywane próbkowanie. Kombinacje polaryzacji i fazy zegara określają tzw. tryb SPI (SPI Mode). Możliwe kombinacje oraz ich oznaczenia pokazano na rysunku 4, zaś przebiegi sygnału zegarowego w różnych trybach pracy SPI widać na rysunku 5.

MicroWire

Interfejs MicroWire został opracowany przez firmę National Semiconductor i jest bardzo podobny do SPI – również służy do asynchronicznego, dwukierunkowego przesyłania danych między urządzeniami master i slave, z tą różnicą, że transmisja jest realizowana w trybie half-duplex. Linie sygnałowe MicroWire to:

- SI/DI (Serial Input) – wejście linii danych z urządzenia nadrzędnego do podrzędnego,

- SO/DO (Serial Output) wyjście linii danych z urządzenia podrzędnego do nadrzędnego, nie zawsze występuje,

- SK/CLK (Serial Clock) – sygnał zegarowy generowany przez urządzenie nadrzędne,

- CS (Chip Select) – sygnał wyboru urządzenia podrzędnego, zwykle aktywny w stanie niskim.

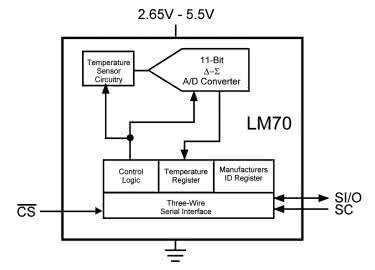

Interfejs MicroWire jest stosowany w szeregowych pamięciach EEPROM (np. 93C46), przetwornikach ADC (np. ADC0831), czujnikach temperatury (np. LM70 – rysunek 6).

SPI 3-przewodowe

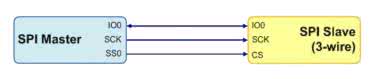

Interfejs SPI może być skonfigurowany do pracy z trzema liniami sygnałowymi. Wtedy linie MISO i MOSI są połączone w jedną, dwukierunkową linię danych (rysunek 7), a interfejs działa w trybie half-duplex. Takie połączenie wymaga możliwości uruchomienia trybu wysokiej impedancji niezależnie w każdej z linii. Zmniejszenie liczby wyprowadzeń może być korzystne w niektórych aplikacjach, ale ogranicza przepustowość połączenia.

Quad SPI

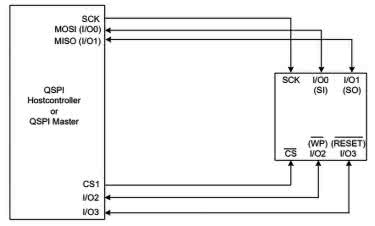

Interfejs SPI znajduje wiele zastosowań, gdy wymagana jest duża szybkość transmisji, np. w układach pamięci Flash lub PSRAM. Specjalnie do takich aplikacji opracowano nowy wariant interfejsu SPI – Quad SPI (QSPI), który zawiera dodatkowe linie danych, zwiększające efektywną przepustowość. Schemat połączenia układów z użyciem QSPI pokazano na rysunku 8. Całkowita liczba wyprowadzeń zwiększyła się o linie I/O2 i I/O3, jednak dodatkowo linie MOSI i MISO, w określonych sytuacjach, zmieniają swoją funkcję i stają się liniami I/O0 i I/O1.

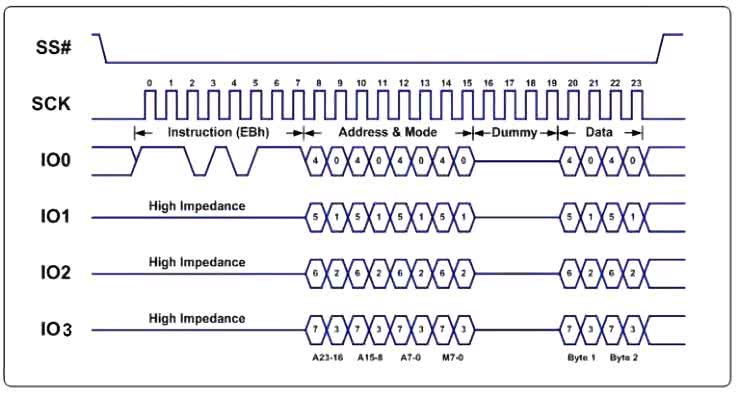

Uruchomienie i zmiana funkcji wyprowadzeń wymaga specjalnych poleceń wysyłanych w normalnym trybie. Po uruchomieniu trybu Quad przepustowość interfejsu wzrasta czterokrotnie. Na rysunku 9 została pokazana przykładowa sekwencja odczytu pamięci z użyciem trybu QSPI. Przesyłanie 1 bajtu danych zajmuje 2 cykle zegarowe zamiast 8 cykli – w pierwszym cyklu linie I/O0…3 przekazują starsze bity (4…7), w drugim cyklu zegara przesyłane są bity młodsze (0…3).

Interfejs I²C

Nazwa I²C (I²C, IIC) oznacza Inter-Integrated Circuit i odnosi się do synchronicznej, szeregowej magistrali komunikacyjnej, opracowanej w 1982 r. przez Philips Semiconductor. Jest szeroko stosowana w dołączaniu peryferyjnych układów scalonych do mikrokontrolerów w aplikacjach, które nie wymagają dużej prędkości komunikacji i akceptują niewielkie długości połączeń.

Interfejs I²C zawiera dwie dwukierunkowe linie:

- SDA – linia danych (Serial Data Line),

- SCL – linia zegara (Serial Clock Line).

Zalety

• Tylko dwie linie sygnałowe SDA (dane) i SCL (zegar), nawet przy wielu urządzeniach.

• Adresowanie układów – każdy układ ma unikalny adres 7- lub 10-bitowy, co pozwala podłączyć wiele układów do jednej magistrali.

• Możliwe wsparcie dla konfiguracji z kilkoma urządzeniami master.

• Wbudowany mechanizm potwierdzeń (ACK/NACK), który umożliwia wykrywanie krytycznych błędów.

• Clock stretching, czyli możliwość wstrzymania transmisji przez układ slave, co zwiększa elastyczność w komunikacji z wolniejszymi układami.

• Jest to jednoznaczny, szeroko wspierany standard, co ułatwia implementację.

Wady

• Relatywnie mała prędkość transmisji – typowe wartości to: 100 kbps, 400 kbps, 1 Mbps oraz 3,4 Mbps (maks.).

• Half-duplex – dane przesyłane są tylko w jednym kierunku naraz.

• Złożoność protokołu.

• Większa liczba urządzeń oznacza wyższą pojemność pasożytniczą, co może ograniczyć długość magistrali i prędkość transmisji.

• Wrażliwość na zakłócenia – jest to magistrala ze sterowaniem typu otwarty dren, zatem zakłócenia mogą powodować błędy transmisji, szczególnie przy długich przewodach.

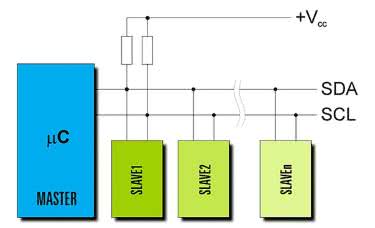

Obydwie linie są podciągnięte do źródła zasilania poprzez rezystory podciągające (pull-up), natomiast wszystkie dołączone do magistrali mają linie SDA/SCL typu otwarty kolektor (otwarty dren). Na liniach I²C logiczna „1” jest zatem stanem recesywnym, a logiczne „0” – dominującym. Taki sposób sterowania magistralą pozwala na wykrywanie kolizji. Standard zakłada połączenie urządzeń w topologii magistrali, a jej długość jest ograniczona maksymalną pojemnością, która nie może przekraczać 400 pF, co w praktyce ogranicza długość do kilku metrów. Na rysunku 10 pokazano schemat typowej magistrali I²C.

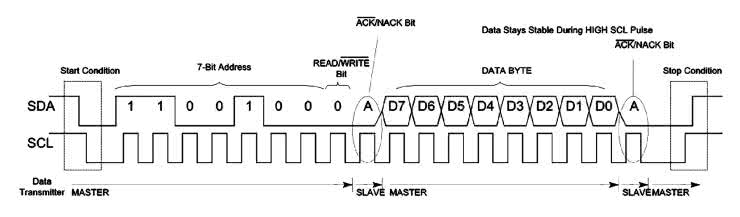

Transmisje są zawsze inicjowane przez układ master, który generuje specjalną sekwencję startu (S), w której sygnał SDA zmienia stan z wysokiego na niski, podczas gdy linia SCL jest utrzymywana w stanie wysokim. Urządzenia slave są adresowane na podstawie pierwszego bajtu wysyłanego po sekwencji startowej – każde urządzenie ma swój unikatowy w danym systemie, 7- lub 10-bitowy adres. Bezpośrednio za adresem przesyłany jest bit R/W (Read/Write) decydujący o kierunku transmitowanych danych. Dane są zawsze 8-bitowe, ale ramka jest jednak rozszerzona o dziewiąty impuls zegarowy, który służy do przesyłania bitu potwierdzającego odebranie informacji – ACK. Przykładowa ramka transmisji I²C została pokazana na rysunku 11. Ze względu na rozwiązania sprzętowe przyjęte w interfejsie I²C zastosowany w nim protokół jest dużo bardziej złożony, niż w SPI. Dokładny opis można znaleźć w: [1], [2].

Podstawowa wersja I²C zakłada istnienie tylko jednego urządzenia, które może inicjować transmisję (master), ale dzięki istnieniu mechanizmu detekcji kolizji możliwa jest praca w trybie multi-master. Występuje również system arbitrażu ze stałym przydziałem priorytetów, określonym przez adres urządzenia typu slave. Urządzenia o niższych adresach mają wyższy priorytet od urządzeń o adresach wyższych.

Standard I²C obsługuje określa 4 podstawowe prędkości transmisji:

- 100 kbps – tryb standardowy,

- 400 kbps – tryb szybki (Fast Mode),

- 1 Mbps – Fast Mode Plus,

- High Speed Mode – prędkość transmisji dochodzi do nawet 3,4 Mbps.

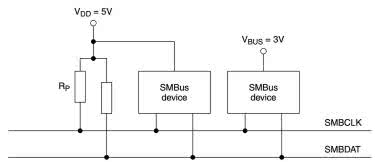

SMBus

Interfejs SMBus (System Management Bus) to dwuprzewodowa magistrala, bazująca na standardzie I²C i służąca do komunikacji między różnymi układami scalonymi w obrębie jednego systemu (rysunek 12). Jest to łatwa w implementacji i wydajna metoda komunikacji, często stosowana w komputerach osobistych do monitorowania temperatury, kontroli prędkości wentylatorów, sterowania oświetleniem RGB czy obsługi kontrolerów baterii. Linie komunikacyjne są oznaczone jako SMBDAT – odpowiednik SDA, SMBCLK – odpowiednik SCL.

SMBus jest kompatybilny z interfejsem I²C, choć nieco bardziej restrykcyjny niż I²C. Poniżej zebraliśmy kilka różnic między obydwoma standardami.

- SMBus ma określone ograniczenia dotyczące parametrów czasowych transmisji, w tym prędkości transmisji (częstotliwość sygnału taktującego powinna zawierać się w przedziale 10…100 kHz) oraz tzw. timeoutu – maksymalnego czasu stanu niskiego, który wynosi zwykle 35 ms.

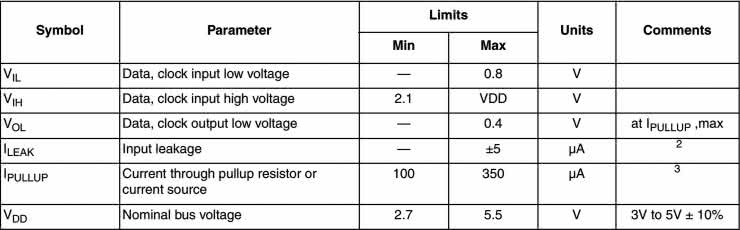

- Ściśle określone są poziomy napięć i wartości prądów płynących przez rezystory pull-up (rysunek 13), w tym minimalny (100 μA) i maksymalny (350 μA), co z kolei określa dopuszczalne wartości rezystorów.

- Układy odłączone od zasilania nie mogą obciążać linii magistrali SMBus.

- SMBus ma określoną liczbą układów, które można podłączyć do magistrali – jest to 127.

Pomimo tych wymagań możliwe jest stosowanie układów I²C w magistrali SMBus.

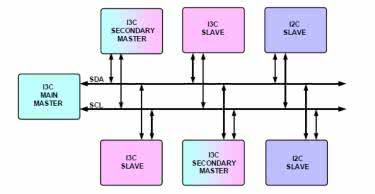

I³C

Interfejs I³C (Improved Inter-Integrated Circuit) to ulepszony interfejs komunikacyjny, który ma zastąpić I²C i oferuje przede wszystkim większe szybkości transmisji, większą elastyczność i mniejsze zużycie energii. Na rysunku 14 pokazano strukturę magistrali I³C.

Standard I³C oferuje szybki transfer danych – do 12,5 Mbit/s (przy częstotliwości taktowania 12,5 MHz) w trybie pojedynczej szybkości transmisji danych (SDR). Dodatkowo dostępnych jest kilka trybów HDR (High Data Rate), które pozwalają na osiągnięcie prędkości bliskich 40 Mbps. Wspomniane tryby HDR działają z tą samą częstotliwością zegara, ale przesyłają dane z większą gęstością. Pierwszym z trybów wysokiej szybkości przesyłu danych jest tryb podwójnej szybkości (HDR-DDR), w którym dane są taktowane na obu zboczach sygnału zegara, co zapewnia prawie dwukrotny wzrost wydajności. Przy zegarze 12,5 MHz tryb DDR osiąga efektywną szybkość transmisji danych do 20 Mbit/s.

Magistrala I³C pozwala na łączenie wielu urządzeń nadrzędnych, wprowadzanych do magistrali jako urządzenia podrzędne. W interfejsie I³C można mieć wiele urządzeń nadrzędnych, ale tylko jedno z nich może być kontrolerem. Po zarejestrowaniu, dodatkowe urządzenie główne może zażądać statusu aktualnego urządzenia głównego, a jeśli urządzenie nadrzędne wyrazi zgodę, sterowanie zostanie przekazane dodatkowemu urządzeniu głównemu.

Zalety

• Wysoka prędkość transmisji danych – I³C obsługuje standardową szybkość transmisji danych (SDR) wynoszącą 10 Mb/s oraz kilka trybów HDR (High Data Rate) z prędkością do niemal 40 Mb/s.

• I³C obsługuje magistralę z wieloma układami slave i wieloma układami master.

• Kompatybilność wsteczna – interfejs I³C może być kompatybilny wstecznie z I²C.

• Nowoczesne funkcje takie, jak: Common Command Codes (CCCs) i In-Band Interrupts (IBI).

• Tylko dwie linie sygnałowe: SDA (dane) oraz SCL (zegar), nie są konieczne dodatkowe linie przerwań czy wyboru układu.

• Dynamiczne adresowanie – układy slave mogą otrzymywać adresy dynamicznie od mastera, co pozwala na bardziej elastyczne zarządzanie magistralą.

Wady

• Złożoność implementacji – I³C ma bardziej rozbudowany protokół niż I²C, który jest trudniejszy w implementacji programowej i sprzętowej.

• Brak powszechnego wsparcia – mimo rosnącej popularności, nadal stosunkowo mało mikrokontrolerów i urządzeń obsługuje natywnie I³C.

• Zależność od MIPI Alliance – I³C to zastrzeżony standard, co utrudnia dostęp do pełnych specyfikacji dla hobbystów i projektantów systemów open source.

Interfejs I³C używa tych samych dwóch sygnałów co I²C, nazywanych SCL i SDA. Główną różnicą jest to, że I²C obsługuje je zawsze jako wyjścia typu open-drain, więc jego prędkość jest ograniczona przez powolny czas narastania sygnału. I³C używa trybu open-drain dla zachowania kompatybilności, ale przełącza się na wyjścia push-pull, gdy jest to możliwe i wtedy zmienia protokoły transmisji, aby zwiększyć szybkość transmisji.

Nowatorskim rozwiązaniem są przerwania wewnątrzpasmowe – IBI (Input/Output Block Interrupts). Zarówno interfejs SPI, jak i I²C wymagają dodatkowych linii do obsługi przerwań i innych funkcji sterujących, takich jak wybór układu. W interfejsie I³C do realizacji tych wszystkich zadań wystarczą tylko 2 przewody. Linie przerwań i inne linie sterujące są zastępowane przez przerwania wewnątrzpasmowe. W tej metodzie układ zgłaszający wprowadza swój adres do nagłówka adresowego magistrali I³C, aby powiadomić procesor o przerwaniu.

Kolejnym istotnym rozwiązaniem są wspólne kody poleceń – CCC (Common Command Code). Są to znormalizowane polecenia, które kontroler może rozgłaszać do wszystkich urządzeń I³C jednocześnie lub do określonego urządzenia docelowego. Polecenia te dotyczą elementów związanych z zarządzaniem magistralą. Istnieje ponad czterdzieści poleceń CCC, w tym:

- wprowadź dynamiczne przypisanie adresu (ENTDAA),

- ustaw nowe dynamiczne przypisanie adresu (SETNEWDA),

- włącz zdarzenia (ENEC) i wyłącz zdarzenia (DISEC),

- resetuj dynamiczne przypisanie adresu (RSTDAA),

- wejdź w tryb wysokiej szybkości transmisji danych (ENTHDRx),

- pobierz rejestr charakterystyki urządzenia (GETDCR).

Ponadto producenci układów mają do dyspozycji pewien zakres identyfikatorów CCC do wdrażania własnych poleceń.

Podsumowanie

W artykule zostały opisane tylko wybrane synchroniczne interfejsy szeregowe – te, które są bardzo często stosowane w praktyce, od projektów hobbystycznych, aż po przemysłowe systemy wbudowane. Warto jednak pamiętać, że interfejsy szeregowe to ogromna dziedzina elektroniki i temat na wiele artykułów. Zaliczamy do tego grona interfejsy stosowane w motoryzacji, które zostały opisane w EP 04/22 [3], interfejsy LVDS, którym poświęciliśmy serię artykułów zaczynając od EP 07/15 [4] oraz wiele innych standardów, z USB 3.x i PCIExpress na czele.

Damian Sosnowski, EP

Linki:

- https://t.ly/2basJ

- https://t.ly/eyVL9

- https://t.ly/khcyZ

- https://t.ly/rocw3

- https://t.ly/sOQ18

- https://t.ly/WxugQ

- https://t.ly/KoxS6

- https://t.ly/ZR9ru

Bibliografia:

- SPI

- I²C

- SMBus

- I³C

Zaloguj

Zaloguj