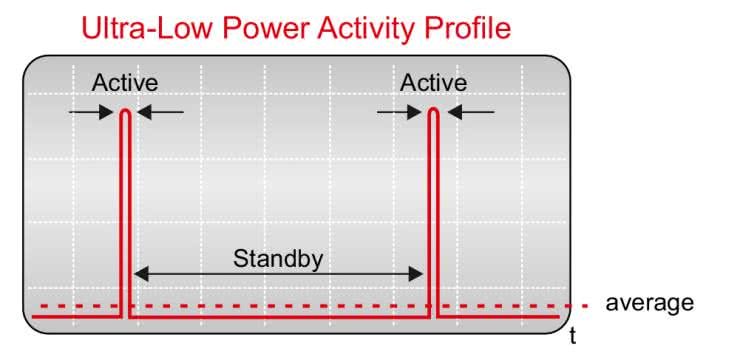

Pierwszym krokiem do zrozumienia prawdziwego znaczenia ULP jest przeanalizowanie różnorodności zastosowań tej technologii. W niektórych projektach wymagany jest najniższy prąd podczas normalnej pracy urządzenia, ponieważ parametry zasilania są mocno ograniczone – na przykład energia elektryczna jest odzyskiwana ze źródeł niestandardowych metodą określaną mianem energy harvesting. Jednak częściej spotykany schemat działania jest taki, że przez większość czasu urządzenie pozostaje w trybie czuwania i dopiero jakieś zdarzenie powoduje wybudzenie systemu w celu wykonania określonych zadań (rysunek 1). W takim przypadku wymagany jest jak najniższy prąd w trybie uśpienia oraz jak najszybsze wybudzanie układu do stanu pełnej funkcjonalności oraz wykonanie zadania. Z tego wynika, że ULP nie koncentruje się tylko na bezpośrednim zmniejszeniu poboru energii, ale także na różnych mechanizmach optymalizacji, które umożliwiają realizację zadań w jak najkrótszym czasie i przy minimalnym użyciu zasobów danego systemu.

Straty energii w układach cyfrowych

Dzisiejsze systemy elektroniczne to przede wszystkim układy cyfrowe oparte na mikrokontrolerach. Całkowita moc pobierana przez układy cyfrowe to suma dwóch czynników:

- mocy statycznej, czyli traconej na skutek prądów upływu struktur półprzewodnikowych. Występuje nawet przy braku sygnału taktującego, w czasie stanu ustalonego i zwiększa się wraz ze wzrostem temperatury;

- mocy dynamicznej spowodowanej przełączaniem stanów logicznych. Wynika ona z ładowania i rozładowywania pojemności pasożytniczych oraz tzw. prądu zwarciowego występującego w chwili przełączania stanu tranzystorów na wyjściach cyfrowych, a uwarunkowanego przede wszystkim czasami narastania i opadania sygnałów.

Moc dynamiczną redukuje się zmniejszając rozmiary tranzystorów, dlatego tak ważna jest generacja technologii litograficznej stosowanej przy produkcji półprzewodników. Moc dynamiczną można również zmniejszyć obniżając częstotliwość taktowania, co niestety obniża również moc obliczeniową układu i wydłuża czas wykonywania zadań. Innym sposobem jest obniżenie wartości napięcia zasilającego, co z kolei generuje kilka innych problemów, m.in. wydłuża czasy propagacji, zmniejsza margines szumów prądu statycznego, a dodatkowo podwyższa statyczny pobór mocy, co wymusza stosowanie skomplikowanych struktur półprzewodnikowych.

Moc statyczną redukuje się poprzez zaawansowane technologie wytwarzania półprzewodników oraz takie techniki jak VTCMOS (variable threshold CMOS). Wymaga to dodatkowych obwodów sterujących i zasilających, które wytwarzają napięcia wyższe od napięcia zasilającego oraz ujemne względem potencjału masy. Wbrew pozorom, moc statyczna jest istotnym składnikiem całkowitego poboru energii. W stosowanych obecnie niskonapięciowych półprzewodnikach jej udział wynosi ok. 10%, a w najbardziej zaawansowanych układach staje się porównywalna ze stratami dynamicznymi. Więcej informacji na temat mocy dynamicznej i statycznej oraz metod ich redukowania można znaleźć tu: [1].

Nowoczesne metody zarządzania poborem energii

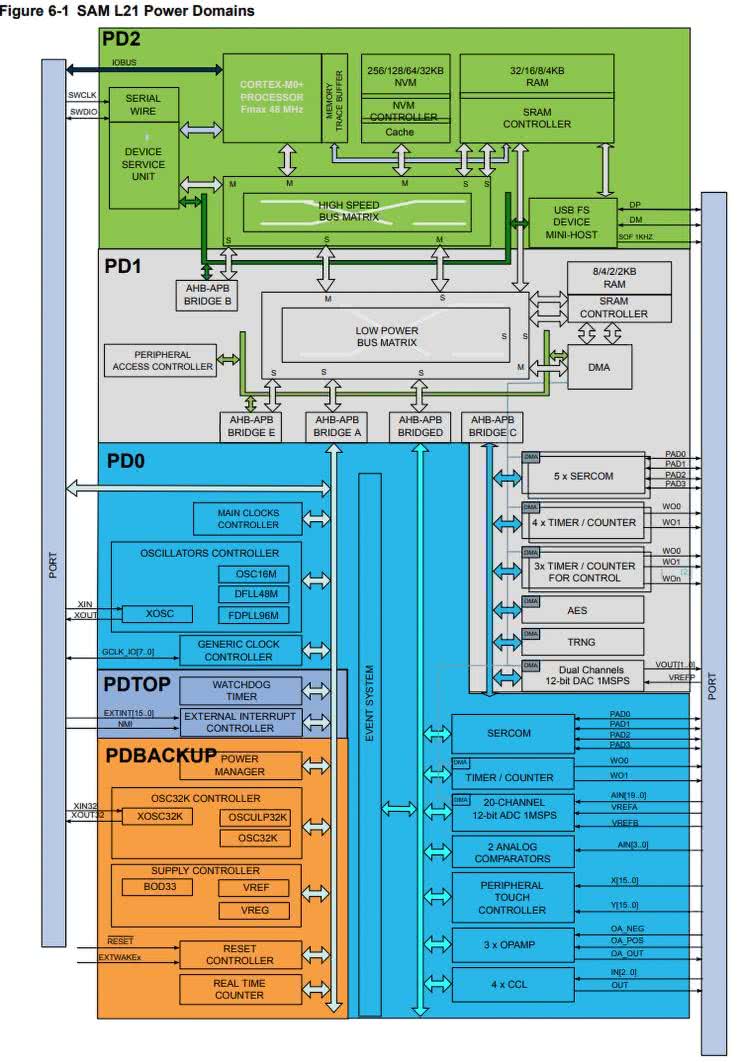

Biorąc pod uwagę wcześniejsze informacje wnioskujemy, że cyfrowy układ scalony powinien być taktowany możliwie niską częstotliwością i dostosowany do zasilania możliwie niskim napięciem, aby był odpowiedni do zastosowań ULP. Nie jest to łatwe do zrealizowania, ponieważ pozostaje sprzeczne z wymaganiami niezbędnymi do osiągnięcia wysokiej wydajności obliczeniowej. Bardziej elastycznym rozwiązaniem jest wydzielenie w strukturze mikrokontrolera bloków funkcyjnych i niezależne aktywowanie tylko tych, które są w danym momencie używane. Wymaga to rozbudowanych obwodów zasilania, takich jak PMD (Peripheral Module Disable) lub PMU (Power Management Unit), ale daje świetne rezultaty. Na rysunku 2 pokazano strukturę blokową mikrokontrolera SAM L21 z rodziny układów Low-Power, gdzie zaznaczono 5 wydzielonych domen zasilania.

Mikrokontrolery oferują zwykle kilka podstawowych trybów oszczędzania energii. Każdy kolejny tryb wyłącza więcej wewnętrznych bloków funkcjonalnych i obniża zużycie prądu kosztem ograniczonej funkcjonalności lub wydajności. Najczęściej stosowane tryby obniżonego poboru prądu to:

- Tryb czuwania (Idle Mode, Low Power Mode) – jest kompromisem między szybką reakcją a oszczędnością energii. Rdzeń zostaje zatrzymany, ale podstawowe peryferia, zegar systemowy i pamięć RAM pozostają aktywne i zasilane. Mikrokontroler może być natychmiast wybudzony w odpowiedzi na przerwanie, np. z timera, UART czy SPI. Pobór prądu jest znacznie niższy niż w trybie aktywnym, ale w dalszym ciągu relatywnie wysoki.

- Tryb uśpienia (Sleep Mode, Power-Down Mode) – to podstawowy tryb oszczędzania energii. Większość funkcji mikrokontrolera jest wyłączona, zatrzymywane są główne oscylatory i sygnały taktujące, a działają tylko niezbędne bloki: pamięć RAM (w celu zachowania danych), zegar czasu rzeczywistego (RTC) czy kontrolery przerwań zewnętrznych. Pobór prądu w tym trybie spada do poziomu mikroamperów, ale wybudzenie może trwać nieco dłużej niż w przypadku trybu Idle.

- Tryb głębokiego uśpienia (Deep Sleep Mode, Standby Mode, Hibernate) oferuje maksymalną redukcję zużycia energii. Niemal wszystkie bloki funkcjonalne i zasilanie są odcięte. Często tracona jest zawartość pamięci RAM, a podtrzymywane są jedynie podstawowe rejestry, stany pinów I/O i moduł RTC – w efekcie pobór prądu spada często poniżej 1 μA. Wybudzenie z tego trybu trwa najdłużej i zazwyczaj następuje tylko poprzez zewnętrzne zdarzenie (np. wynikające ze zmiany stanu logicznego na odpowiednim pinie) lub po upływie zadanego czasu ustawionego w RTC.

W zaawansowanych układach o ultra niskim poborze mocy może być dużo więcej trybów niskiego poboru mocy – np. 7. Wybór odpowiedniego zależy od wymagań aplikacji – głównie od tego, czy konieczna jest natychmiastowa reakcja, czy jednak dopuszczalne jest niewielkie opóźnienie w zamian za możliwość uzyskania wielu lat pracy na jednej baterii.

Niektóre bloki funkcyjne, które mają zatrzymane taktowanie oraz odłączone zasilanie wymagają złożonej procedury wybudzenia – dotyczy to np. przetworników ADC (Analog Digital Converter). Użycie takiego bloku wymaga odblokowania zasilania, podania sygnału taktującego i czasami uruchomienia prostej procedury kalibracji. Cały ten proces może trwać relatywnie długo i pochłonąć znacznie więcej energii, niż w trakcie normalnej pracy danego bloku. Dlatego jest to kolejne pole optymalizacji w zakresie techniki ULP (pod względem szybkości wybudzania lub czasu potrzebnego do osiągnięcia pełnej funkcjonalności, czyli tzw. wake-up time). Układy lub bloki funkcyjne, w których zoptymalizowano ten proces, są oznaczane jako fast wake-up time.

Nie wszystkie obwody mikrokontrolera mogą być wyłączone lub zatrzymane. Są to przeważnie liczniki/zegary czasu rzeczywistego (RTC – Real-Time Clock) niezbędne do odmierzania czasu, układy nadzorujące napięcie zasilania (BOD/BOR – Brown-Out Detection/Brown-Out Reset, VLM – Voltage Level Monitor) czy liczniki typu watchdog (WDT – Watchdog Timer). Dlatego są one zaprojektowane w taki sposób, aby pobierały wyjątkowo mały prąd w stanie aktywnym – maksymalnie 0,2…0,5 μA.

Duże znaczenie ma precyzyjna kontrola nad częstotliwością taktowania. Nowoczesne układy mają zintegrowane różne źródła sygnałów zegarowych, m.in.:

- Oscylatory RC o wysokiej częstotliwości (np. HSI RC – High Speed Internal RC, lub FRO – Free Running Oscillator) – generują sygnały taktujące o częstotliwościach od pojedynczych MHz do setek MHz. Nie są zbyt precyzyjne, zwykle mają dokładność rzędu ±2%, ale pobierają dużo mniej energii niż oscylatory kwarcowe. Są używane tylko wtedy, gdy wymagana jest duża moc obliczeniowa, a precyzja odmierzania czasu/częstotliwości jest mniej istotna.

- Precyzyjne oscylatory kwarcowe (np. HSE – High Speed External, lub EXTOSC – External Oscillator) – są źródłem stabilnych i dokładnych sygnałów taktujących, ale wymagają zewnętrznego rezonatora kwarcowego i pobierają więcej energii, niż generatory RC. Sygnał taktujący zwykle jest przetwarzany w blokach PLL i można bardzo elastyczne ustalać częstotliwość wyjściową.

- Oscylatory o niskiej częstotliwości i niskim poborze energii (np. LSI – Low Speed Internal, LSE – Low Speed External, LPOSC – Low Power Oscillator) – dostarczają sygnałów taktujących o bardzo niskich częstotliwościach rzędu kiloherców i służą do taktowania mikrokontrolera w trybach obniżonego poboru energii.

- Oscylatory RTC (Real Time Clock) – źródło taktowania dla układu zegara czasu rzeczywistego. Zwykle wymaga zewnętrznego rezonatora kwarcowego 32,768 kHz i ma wejście zasilania do podłączenia baterii podtrzymującej, dzięki czemu działa nawet po zaniku zasilania głównego. Oscylatory RTC pobierają bardzo mało prądu, zwykle poniżej 1 μA.

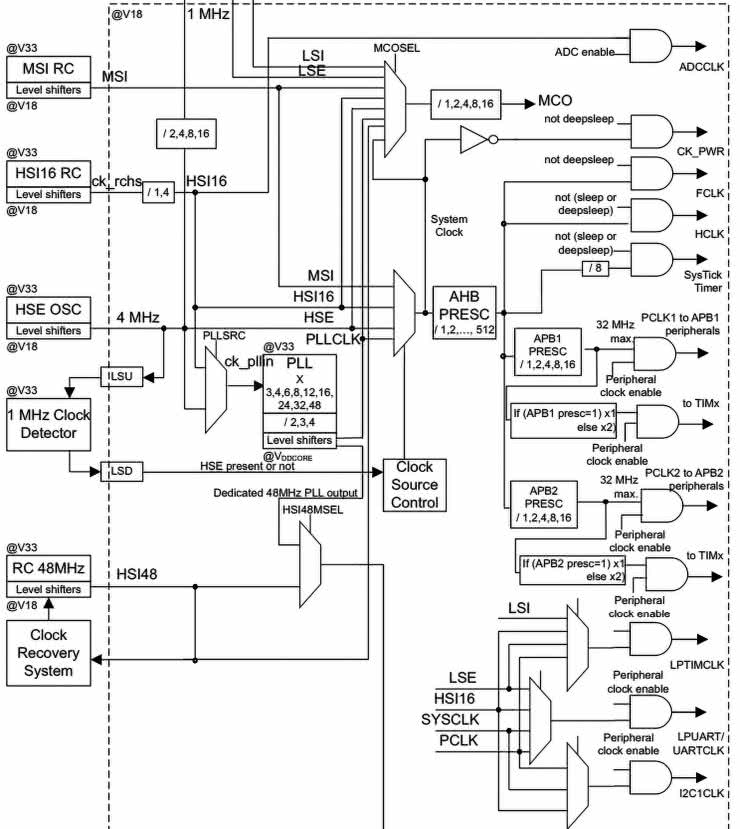

Fundamentalną funkcją dla optymalizacji poboru energii jest możliwość szybkiego przełączania się między sygnałami traktującymi o różnych częstotliwościach, w zależności od aktualnych wymagań aplikacji. Dlatego moduły zarządzania sygnałem zegarowym (CMU – Clock Management Unit, RCC – Reset and Clock Configuration) pozwalają nie tylko wybrać źródło taktowania CPU, ale również niezależne źródła taktowania dla większości układów peryferyjnych. W efekcie są to bardzo złożone struktury – na rysunku 3 pokazano uproszczony schemat blokowy modułu RCC w niewielkim mikrokontrolerze STM32L0xx. Najbardziej zaawansowane układy są wyposażone w moduły DVFS (Dynamic Voltage and Frequency Scaling) odpowiedzialne za dynamiczne skalowanie napięcia i częstotliwości oraz AVFS (Adaptive Voltage and Frequency Scaling) realizujące to zadanie w sposób adaptacyjny.

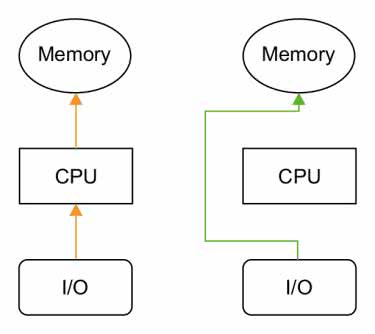

Szczególnym rozwiązaniem jest system DMA (Direct Memory Access), który został zaprojektowany z myślą o zwiększeniu wydajności operacyjnej mikrokontrolerów, ale jednocześnie umożliwia bardziej optymalne zarządzanie poborem energii. Bez jego użycia procesor musi aktywnie sterować transferem danych, na przykład odbierając pojedyncze bajty z urządzenia peryferyjnego (UART, SPI, ADC itp.) i zapisując je do pamięci RAM. Wymaga to ciągłego działania CPU, który zazwyczaj jest najbardziej energochłonnym elementem mikrokontrolera. Dzięki DMA specjalny kontroler przejmuje zadanie przenoszenia bloków danych między peryferiami a pamięcią, bez konieczności udziału CPU (rysunek 4). W tym czasie procesor może zostać przełączony w tryb uśpienia, niskiego poboru mocy lub może wykonywać inne zadania.

Dodatkowo użycie DMA eliminuje również tzw. narzut związany z przerwaniami (tzw. Interrupt Overhead). Tradycyjne metody przesyłania danych często bazują na przerwaniach, które wybudzają rdzeń za każdym razem, gdy wymagana jest operacja odczytu lub zapisu, np. po odebraniu pojedynczego bajtu. Generowanie przerwań i przełączanie kontekstu, czyli zapisywanie i przywracanie stanu procesora, wiąże się z dodatkowym zapotrzebowaniem energetycznym. DMA pozwala na transfer całego bufora danych, generując na przykład tylko jedno przerwanie po zakończeniu całej transakcji, co znacznie redukuje liczbę wybudzeń i narzut energetyczny. Wszystkie korzyści, jakie niesie DMA powodują, że jest to konieczne rozwiązanie w nowoczesnych systemach wbudowanych, gdzie wymagany jest niski pobór energii.

Istnieje też wiele innych wyspecjalizowanych rozwiązań w obszarze bloków peryferyjnych. Dlatego w kolejnej części tego artykułu prześledzimy dokładnie oferty kluczowych producentów i opiszemy najciekawsze rozwiązania.

Układy PIC oraz SAM L od Microchip

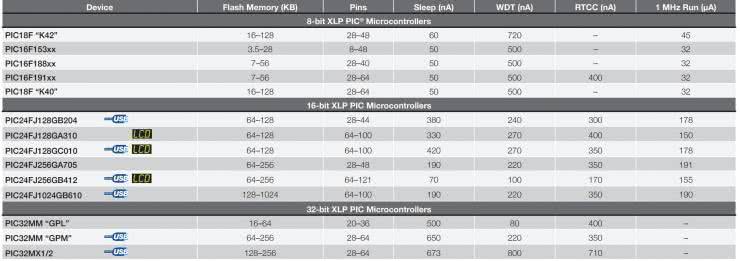

Firma Microchip oferuje układy z technologią nanoWatt XLP (eXtreme Low Power), które – jak sama nazwa wskazuje – odznaczają się ekstremalnie niskim poborem mocy. Podstawowe parametry układów nanoWatt XLP to:

- pobór prądu w stanie uśpienia: już od 9 nA,

- pobór prądu modułu BOD: do 45 nA,

- pobór prądu licznika watchdog: do 200 nA,

- pobór prądu licznika RTC (zegar + kalendarz): do 300 nA,

- pobór prądu w stanie aktywnym: do 30 μA/MHz,

- pełna funkcjonalność bloków analogowych i możliwość zapisu danych przy napięciu zasilania od 1,8 V.

Układy Microchip oferują również zaawansowane bloki peryferyjne o obniżonym poborze mocy, takie jak interfejs USB, kontrolery wyświetlacza LCD i klawiatury pojemnościowej (mTouch) oraz rozbudowane bloki analogowe: ADC i komparatory. Zintegrowane układy peryferyjne, przystosowane do pracy w trybie niezależnym od rdzenia, są określane mianem CIP (Core Independent Peripheral) – dzięki nim procesor może być wprowadzony w tryb niskiego poboru mocy, podczas gdy urządzenia peryferyjne będą wykonywały niezbędne funkcje.

Układy XLP od Microchip to mikrokontrolery PIC z serii PIC16F, PIC18F (8-bitowe), PIC24FJ (16-bitowe) i PIC32MM/MX (32-bitowe). Porównanie parametrów wybranych modeli zostało pokazane na rysunku 5.

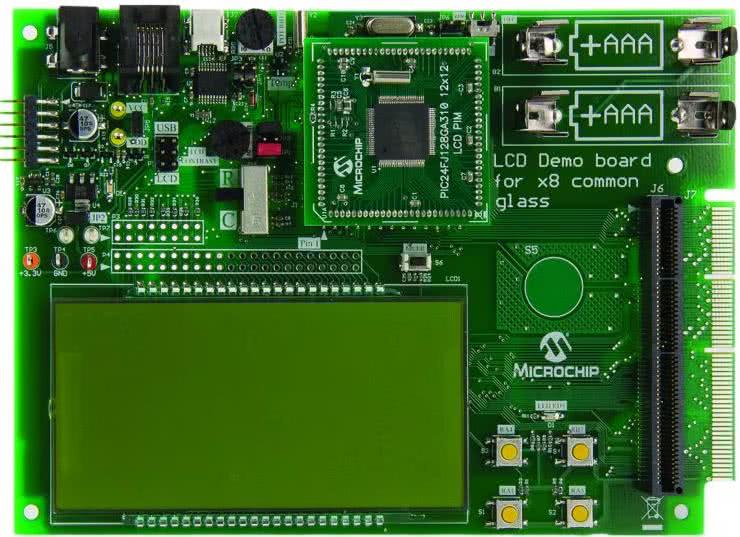

Ogromną zaletą tych układów jest rozbudowane środowisko programistyczne MPLAB X IDE oraz szeroka oferta płytek ewaluacyjnych (fotografia 1).

Kolejną grupą bardziej zaawansowanych układów Microchip o niskim poborze mocy są mikrokontrolery SAM L1x/L2x. Bazują na 32-bitowej architekturze ARM Cortex-M23 (SAM L1x) oraz ARM Cortex-M0+ (SAM L2x) i dzięki zastosowaniu innowacyjnej technologii picoPower zapewniają bardzo niskie zużycie energii, co najlepiej obrazują następujące parametry:

- 25 μA/MHz w trybie aktywnym,

- poniżej 100 nA w trybie uśpienia,

- krótki czas wybudzania wynoszący 1,2 μs,

- pełna funkcjonalność przy napięciu zasilania od 1,62 V.

Układy SAM L1x uzyskały certyfikowany przez EEMBC wynik ULPMark [2] na poziomie 410 dla Core Profile, co jest najwyższą oceną dla rdzeni Cortex-M23 lub Cortex-M0+. Oprócz ultra niskiego poboru mocy, układy te zawierają ulepszony kontroler dotykowy PTC (Peripheral Touch Controller), technologię ARM TrustZone, szyfrowanie AES (Advanced Encryption Standard), kontroler USB Full-Speed Host/Device, 12-bitowy przetwornik ADC, wbudowane wzmacniacze operacyjne oraz kontroler zdarzeń (Event System). Implementują ponadto technologię SleepWalking, która umożliwia urządzeniom peryferyjnym wykonywanie zadań i komunikację bez wybudzania głównego procesora.

MSP430 od Texas Instruments

Texas Instruments (TI) jest liderem w dziedzinie mikrokontrolerów o bardzo niskim poborze mocy, a główną linią produktów są układy MSP430. Te 16-bitowe mikrokontrolery bazują na zaprojektowanej od podstaw, energooszczędnej architekturze RISC, oferującej nawet 7 zoptymalizowanych trybów niskiego poboru mocy. Ponadto zawierają zintegrowane precyzyjne układy analogowe, m.in. 12-bitowe przetworniki ADC i DAC, konfigurowalne komparatory, wzmacniacze operacyjne i PGA, a niektóre modele zostały wyposażone w pamięć ferromagnetyczną Low Power FRAM (seria MSP430FR). Pamięć FRAM łączy szybkość i elastyczność klasycznej technologii statycznego RAMu (SRAM) ze stabilnością i niezawodnością pamięci Flash, zużywając przy tym znacznie mniej energii podczas zapisu (rysunek 6). Szybki zapis do FRAM umożliwia skrócenie czasu przejścia do trybu uśpienia.

Podstawowe parametry wybranego mikrokontrolera typu MSP430FR235x, są następujące:

- pobór prądu w stanie shutdown: 42 nA,

- pobór prądu w stanie LPM3: 1,43 μA oraz LPM3.5: 0,62 μA,

- pobór prądu w stanie aktywnym: do 143 μA/MHz,

- pełna funkcjonalność przy napięciu zasilania od 1,8 V.

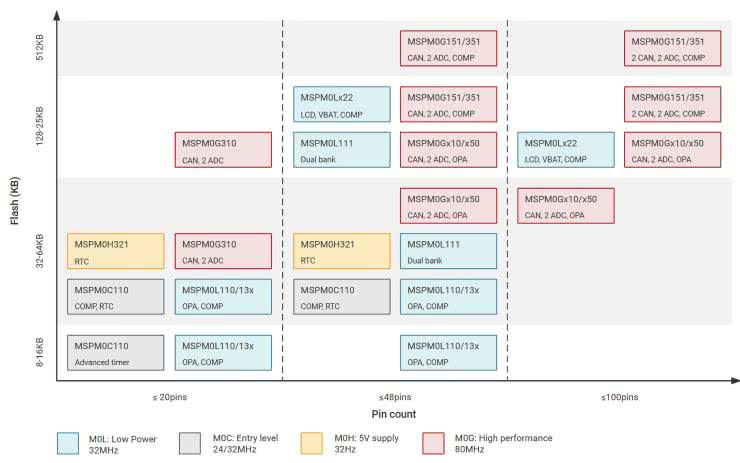

Firma TI opracowała również bardzo wydajne, 32-bitowe mikrokontrolery ULP z rodziny MSP432, bazujące na architekturze Arm Cortex-M (M4F), jednak w 2021 roku ogłoszono wycofanie tej serii układów. Z kolei najnowsza rodzina MSPM0 rozszerza portfolio ULP o 32-bitowe, ekonomiczne i łatwe w użyciu mikrokontrolery bazujące na rdzeniu ARM Cortex-M0+. Układy są dostępne w szerokim zakresie opcji (rysunek 7), od niewielkich układów z podstawowym wyposażeniem typu MSPM0C, po najbardziej złożone MSPM0G z zaawansowaną komunikacją i lepszymi peryferiami analogowymi.

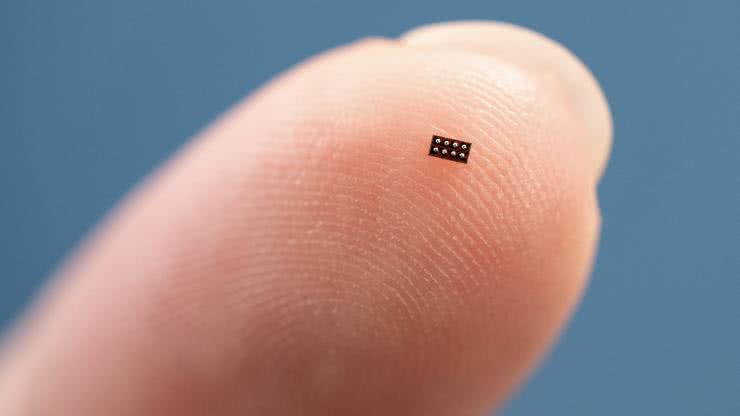

Mikrokontrolery Texas Instruments, oprócz tego, że są jednymi z najbardziej energooszczędnych układów, to od niedawna zyskały również miano najmniejszych. MSPM0C1104 to najmniejszy na świecie mikrokontroler z rdzeniem Cortex-M0+ (MSPM0) – jego powierzchnia to zaledwie 1,38 mm² (fotografia 2). Oferuje 16 kB pamięci, 12-bitowy przetwornik analogowo-cyfrowy z trzema kanałami, sześć uniwersalnych pinów wejścia/wyjścia oraz interfejsy UART, SPI, I²C. Jest przeznaczony do urządzeń medycznych i elektroniki ubieranej.

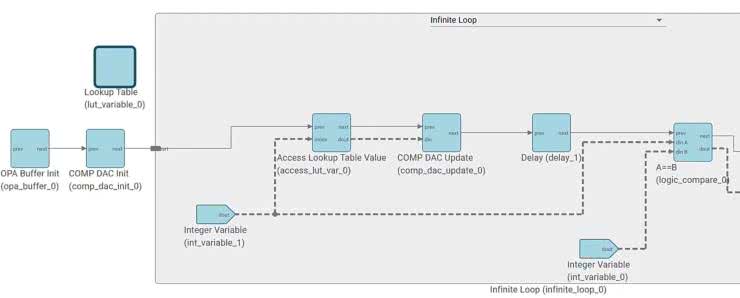

Texas Instruments wspiera deweloperów narzędziami do optymalizacji ULP, takimi jak ULPADVISOR (analizuje kod źródłowy pod kątem optymalizacji energetycznej) oraz EnergyTrace (monitoruje zużycie energii w czasie rzeczywistym podczas debugowania), co ułatwia projektowanie energooszczędnych aplikacji. Natomiast oprogramowanie Zero Code Studio umożliwia tworzenie i uruchamianie aplikacji bez konieczności pisania kodu programu (rysunek 8).

Układy ULP od STM32

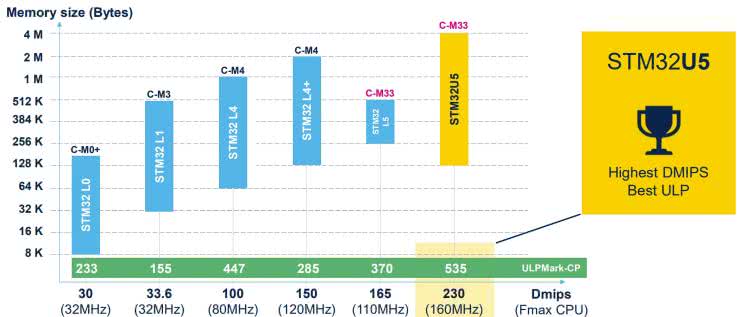

STMicroelectronics (ST) oferuje wiele typów mikrokontrolerów ULP. Ich najnowsze i najbardziej zaawansowane układy z tej kategorii to przede wszystkim seria STM32U5 oraz nowsza, ale nieco uproszczona – seria STM32U0.

Układy STM32U5 łączą ekstremalnie niski pobór mocy z wysoką wydajnością i zaawansowanymi funkcjami bezpieczeństwa (rysunek 9).

Bazują na rdzeniu ARM Cortex-M33 160 MHz z technologią ARM TrustZone oraz blokami MPU, DSP i FPU. Ich kluczowe parametry są następujące:

- pobór prądu w różnych trybach standby: od ok. 200 nA do 4,6 μA,

- pobór prądu w stanie aktywnym: do 16 μA/MHz,

- czas wybudzania wynoszący ok. 8 μs dla trybu Sleep oraz ok. 700 μs dla trybu Shutdown,

- pełna funkcjonalność przy napięciu zasilania od 1,71 V.

W mikrokontrolerach STM32U5 zastosowano innowacyjny tryb LPBAM (Low-Power Background Autonomous Mode), który umożliwia układom peryferyjnym, w tym kontrolerowi DMA, autonomiczną pracę (zbieranie i przesyłanie danych), podczas gdy rdzeń CPU jest uśpiony. Ponadto dysponują one wieloma trybami niskiego poboru energii, w tym trybem Stop 3, w którym pobór prądu, przy zachowaniu pełnej retencji pamięci SRAM i rejestrów, maleje nawet do 2,2 μA, co jest jednym z najlepszych wyników na rynku wysokowydajnych mikrokontrolerów ULP. Wiele wariantów STM32U5 zawiera stabilizator LDO i przetwornicę SMPS, które umożliwiają dynamiczne skalowanie napięcia i w efekcie optymalizację zużycia energii w trybie aktywnym.

Układy STM32U5 są przeznaczone do najbardziej zaawansowanych urządzeń IoT, liczników energii i urządzeń medycznych, także z rozbudowanymi interfejsami graficznymi (dzięki zintegrowanemu GPU NeoChrom).

Seria STM32U0 to najnowsza (wprowadzona w 2024 roku) generacja mikrokontrolerów ULP, pozycjonowana jako układy ULP klasy podstawowej. Bazują na energooszczędnym rdzeniu Cortex-M0+ taktowanym do 56 MHz i oferują bardzo niski pobór prądu w trybach uśpienia oraz konkurencyjną cenę. Ponadto ST nadal oferuje i rozwija układy STM32L4/L4+ bazujące na rdzeniu Cortex-M4 oraz STM32L5 z rdzeniem Cortex-M33 – te ostatnie są zatem podobne do modeli z serii STM32U5, ale bez niektórych najbardziej zaawansowanych funkcji oszczędzania energii. Zamiast ich implementacji inżynierowie ST skupili się bowiem na funkcjach bezpieczeństwa (TrustZone).

EFM32 i Silicon Labs

Mikrokontrolery EFM32 firmy Silicon Labs są jednymi z najbardziej energooszczędnych mikrokontrolerów na świecie, szczególnie polecanymi do zastosowań wymagających niskiego poboru mocy, takich jak mierniki zużycia energii, wody i gazu, systemy alarmowe i systemy bezpieczeństwa, układy do pomiaru parametrów opon TPMS (Tire Pressure Monitoring System) oraz przenośny sprzęt medyczny/fitness. Najnowsze układy ULP od Silicon Labs należą do rodziny Gecko Series 2 i bazują na rdzeniu Cortex-M33. Są to mikrokontrolery oznaczone jako EFM32PG22, EFM32PG23, EFM32PG26 i EFM32PG28, przy czym wraz z oznaczeniem numerycznym zwiększają się znacząco zintegrowane zasoby sprzętowe. Podstawowa wersja PG22 może pracować z taktowaniem do 76 MHz, ma do dyspozycji FPU oraz instrukcje DSP. Podstawowe parametry są następujące:

- pobór prądu w trybie głębokiego uśpienia (deep sleep): ok. 1 μA (przy zachowaniu 8 kB pamięci RAM i działającym RTC),

- pobór prądu w trybie hibernacji EM4: 170 nA,

- pobór prądu w stanie aktywnym: do 26 μA/MHz,

- pełna funkcjonalność przy napięciu zasilania od 1,71 V.

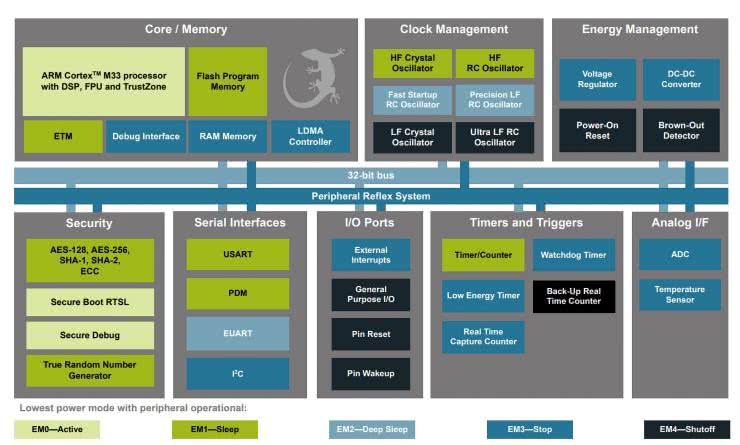

Układ EFM32PG22 oferuje bogaty zestaw peryferiów (rysunek 10), w tym 16-bitowy przetwornik ADC, 8-kanałowy kontroler DMA, liczne timery oraz interfejsy komunikacyjne, w tym cyfrowy interfejs mikrofonowy zgodny z PDM. Zaawansowane funkcje bezpieczeństwa obejmują sprzętową akcelerację kryptograficzną (AES, SHA, ECC), generator liczb losowych (TRNG) oraz mechanizm bezpiecznego rozruchu Secure Boot z obsługą RTSL (Root of Trust and Secure Loader).

Silicon Labs stosuje w swoich układach bloki PRS (Peripheral Reflex System), umożliwiające wbudowanym peryferiom komunikację i interakcję bez użycia rdzenia.

Układy PG23, PG26 i PG28 stanowią rozwinięcie serii PG22: ich parametry są sukcesywnie poprawiane, a wyposażenie sprzętowe – poszerzane. W najwyższej konfiguracji dostępne są m.in. 20-bitowe przetworniki ADC, 1 MB pamięci Flash, kontroler wyświetlacza LCD i sprzętowy akcelerator AI/ML. Warto dodać, że zapotrzebowanie na energię w stanie aktywnym i w różnych trybach uśpienia pozostaje niezmienione.

Podsumowanie

Rynek mikrokontrolerów ULP odnotował w ostatnich latach znaczny wzrost, napędzany rosnącym popytem na energooszczędne urządzenia w branżach takich jak IoT, elektronika użytkowa i automatyka przemysłowa. Ponad 18 miliardów działających urządzeń IoT na całym świecie przyczyniło się do tego, że wartość rynku mikrokontrolerów ULP jest szacowana na ponad 5 mld USD. Te ogromne liczby to również efekt trudu i zaangażowania konstruktorów, którzy musieli sprostać przeciwstawnym wymaganiom bardzo charakterystycznym dla aplikacji o niskim poborze energii. Mamy nadzieję, że zaprezentowane w artykule informacje w jakiś stopniu ułatwią naszym Czytelnikom projektowanie kolejnych urządzeń wpisujących się w klasę ULP.

Damian Sosnowski, EP

Odnośniki:

[1] Redukcja mocy pobieranej przez układy CMOS, https://elektronikab2b.pl/technika/1872-redukcja-mocy-pobieranej-przez-uklady-cmos

[2] ULPMark-CoreProfile, https://www.eembc.org/ulpmark/ulp-cp/scores.php

Bibliografia:

- https://www.ti.com/lit/wp/slay015a/slay015a.pdf

- https://ww1.microchip.com/downloads/en/devicedoc/39941d.pdf

- https://ww1.microchip.com/downloads/aemDocuments/documents/OTH/ProductDocuments/Brochures/30009941J.pdf

- https://www.microchip.com/en-us/products/microcontrollers/32-bit-mcus/pic32-sam/sam-l

- https://www.ti.com/product-category/microcontrollers-processors/msp430-mcus/overview.html

- https://www.ti.com/product-category/microcontrollers-processors/arm-based-mcus/arm-cortex-m0/overview.html

- https://www.analog.com/en/resources/analog-dialogue/articles/strategies-for-choosing-the-appropriate-microcontroller-when-developing-ultra-low-power-systems.html

- https://www.st.com/en/microcontrollers-microprocessors/stm32u5-series.html

- https://www.st.com/content/ccc/resource/training/technical/product_training/group1/cd/14/c3/be/5e/dc/4f/25/STM32U5-series-introduction/files/stm32u5-introduction-marketing-presentation.pdf/_jcr_content/translations/en.stm32u5-introduction-marketing-presentation.pdf

- https://www.silabs.com/mcu/32-bit-microcontrollers

Zaloguj

Zaloguj