Ze wszystkimi zaletami elastycznej implementacji układów FPGA wiąże się jedno rosnące wyzwanie: zasilanie FPGA zapewniające bezproblemowe działanie. Poniższy artykuł ma na celu zidentyfikowanie źródeł złożoności w projektowaniu systemu zasilania układu programowalnego. Wskazuje, jakie kompromisy przy projektowaniu drzewa mocy dla tego rodzaju systemu, należy wziąć pod uwagę oraz dlaczego zasilanie układów FPGA jest prawdziwym problemem systemowym i jak zmienia to paradygmaty projektowania zasilaczy.

Układy programowalne pojawiły się już w latach '80 XX wieku, ewoluując z programowalnych urządzeń logicznych (PLD). Od tego czasu oferta FPGA na rynku rośnie, a wraz z nią ich szybkość i wydajność, czyniąc FPGA rozwiązaniem dla szerokiej gamy zastosowań obliczeniowych, zwłaszcza, gdy wielkość produkcji nie uzasadnia kosztów rozwoju układów scalonych specyficznych dla aplikacji (ASIC).

Układy FPGA rozwinęły się do tego stopnia, że znalazły zastosowanie w dużych wdrożeniach. Na przykład, po pomyślnym przyspieszeniu wyszukiwarki Bing za pomocą układów FPGA w ramach programu pilotażowego z 2013 r., Microsoft rozszerzył stosowanie serwerów wyposażonych w FPGA w swoich chmurowych centrach danych. Podobne kroki od lat czyni również Amazon, udostępniający usługę FPGA as a Service, dając dostęp programistom do opracowywania dedykowanych rozwiązań obliczeniowych pracujących w chmurze. Nic nie wskazuje na to, aby w najbliższym czasie trend ten miał się zmienić, a analitycy wróżą sektorowi układów FPGA wzrost na poziomie 8,6% w czasie najbliższych pięciu lat.

Kluczem do niezawodnie działającej aplikacji z układami programowalnymi jest ich poprawne zasilanie. Układy FPGA wymagają szeregu różnych szyn zasilających niskiego napięcia, z których każda ma własną specyfikację dotyczącą poziomu napięcia, jego dokładności i dostarczanego prądu. Poszczególne domeny zasilania stosowane są po to, aby zasilać wewnętrzną logikę rdzenia, obwody wejścia i wyjścia, logikę pomocniczą, transceivery oraz pamięć. Szyny te mogą wymagać włączania i wyłączania w określonej kolejności, aby zagwarantować poprawne uruchomienie układu czy też, aby uniknąć uszkodzenia FPGA.

Definicja wymagań zasilania FPGA

Wymagania dotyczące zasilania w układzie FPGA są określane przez sumę stałych i zmiennych warunków: statyczny pobór mocy, wynika z technologii procesu produkcji konkretnego układu i jego konstrukcji w krzemie. Dynamiczny pobór mocy wynika z unikalnych warunków pracy FPGA, innych dla każdego projektu.

Moc dynamiczna jest iloczynem ilości i specyfiki wykorzystania każdego z zasobów układu FPGA. Jest to funkcja dodatkowego poboru mocy spowodowanego przez przełączanie sygnałów w układzie oraz ładowanie i rozładowywanie obciążeń pojemnościowych w systemie i poza nim. W rezultacie bardziej obciążone konstrukcje FPGA, a także projekty z wyższymi częstotliwościami taktowania będą zużywać więcej energii przy użyciu dokładnie tych samych komponentów. Na przykład, ilość potrzebnych pinów GPIO i szybkich szeregowych transceiverów wpływa na całkowite zapotrzebowanie na moc układu, ponieważ kwestie takie, jak zastosowane standardy wyjścia oraz oczekiwane szybkości transmisji danych określają, jak szybko przełączać muszą się tranzystory w portach, a co za tym idzie jak szybko musi być taktowana logika układu. Zgodnie z oczekiwaniami, im szybciej przesyłane są dane oraz im wyższa jest częstotliwość zegara, tym więcej prądu potrzebuje układ. Wynika to z faktu, że im wyższa częstotliwość, tym częściej sygnały muszą ładować i rozładowywać bramki poszczególnych tranzystorów w układzie.

Biorąc pod uwagę to, jak wiele jest czynników determinujących wymagania dotyczące zasilania FPGA, można spodziewać się, że wymagania dotyczące sekcji zasilania będą się znacznie różnić, zarówno w różnych rodzinach FPGA, jak i w różnych przypadkach użycia tego samego FPGA. Jednak koniecznie trzeba poznać pewne ogólne założenia dotyczące zasilania tych układów scalonych, aby łatwiej projektować systemy zasilania układów programowalnych, dopasowane do wymagań konkretnej aplikacji.

Uproszczona budowa systemu zasilania FPGA

Stabilizatory tzw. punktu obciążenia (POL), czyli znajdujące się tuż przy odbiorniku mocy, to układy, które obniżają wyższe napięcie do wymagań poszczególnych domen zasilania, wymaganych przez układ, np. FPGA. Jako stabilizatory POL używane są tak przetwornice impulsowe, jak i układy liniowe. Te pierwsze stosuje się, gdy istotna jest wysoka sprawność energetyczna systemu, a te drugie, gdy kluczowe są parametry napięcia zasilania, takie jak poziom szumu i zakłóceń, np. do zasilania czułych obwodów PLL lub transceiverów.

Typowe napięcia wejściowe dla całego urządzenia to 5 V, 12 V, 24 V lub 48 V, podczas gdy napięcia szyn zasilania FPGA mieszczą się w zakresie od poniżej 1 V do około 3 V. Dla wysokich napięć wejściowych (12 V, 24 V, 48 V) może być potrzebny dodatkowy stopień przetwarzania, do wygenerowania linii napięcia pośredniego, która zasila stabilizatory POL (rysunek 1). Spośród szyn układu FPGA to zasilanie rdzenia wymaga najniższego napięcia (około 1 V lub poniżej) i najwyższej dokładności (±3% lub lepiej), przy poziomach prądu rzędu nawet dziesiątek amperów. Aby zapobiec błędom logicznym, wahania linii zasilania muszą być ograniczone do nie więcej niż kilkudziesięciu miliwoltów, zgodnie ze specyfikacją FPGA. Ważne jest, aby wahania te były tak małe, nie tylko w warunkach statycznych, ale także w czasie dynamicznych zmian prądów FPGA.

Im gorsza dokładność napięcia, tym większa pojemność filtrująca potrzebna jest do utrzymania akceptowalnego napięcia zasilania w warunkach przejściowych. Dokładniej parametry te i sposoby radzenia sobie z nimi dla różnych domen zasilania opisano w dalszej części artykułu.

Sekwencjonowanie napięć zasilania

Wiele układów FPGA wymaga załączania poszczególnych szyn zasilania w określonej kolejności. Często napięcie rdzenia musi być doprowadzone zanim pojawią się napięcia modułów wejścia/wyjścia. W przeciwnym razie układ FPGA może zostać uszkodzony. Aby tego uniknąć, należy skonfigurować odpowiednią sekwencję załączania domen zasilania.

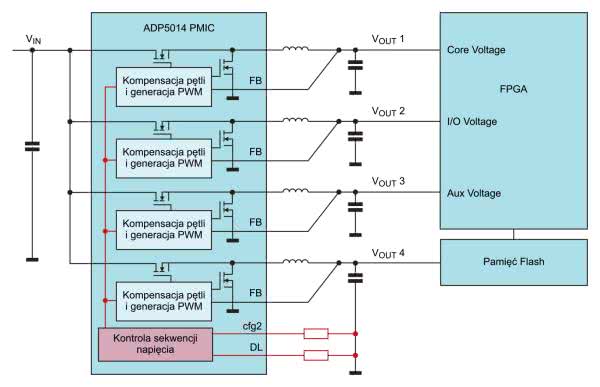

Najprostszy system sekwencjonowania załączania napięć można łatwo wykonać za pomocą pinów włączających (enable) w standardowych przetwornicach DC/DC. Jednak zwykle wymagane jest również kontrolowane sekwencjonowanie w czasie wyłączania urządzenia. Trudno jest osiągnąć dobry wynik w takiej aplikacji z użyciem tylko pinów kontrolujących pracę układów. Lepszym rozwiązaniem jest użycie układu typu PMIC z zaawansowanymi zintegrowanymi funkcjami sekwencjonowania, takiego jak na przykład ADP5014. Specjalny blok obwodu, który umożliwia regulację kolejności sekwencji podczas załączania i wyłączania napięć, jest zaznaczony na czerwono na rysunku 2.

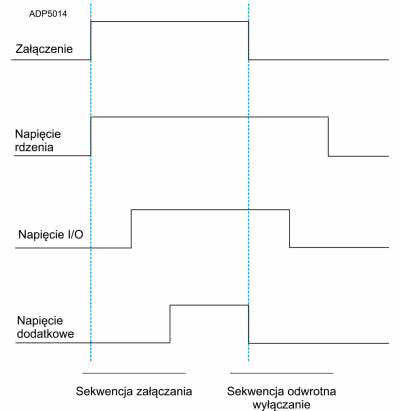

Na rysunku 3 zostały pokazane przebiegi napięć podczas sekwencjonowania za pomocą tego układu. Opóźnienie czasowe dla sekwencjonowania podczas załączania i wyłączania systemu można łatwo regulować za pomocą pinów opóźnienia (DL) układu ADP5014.

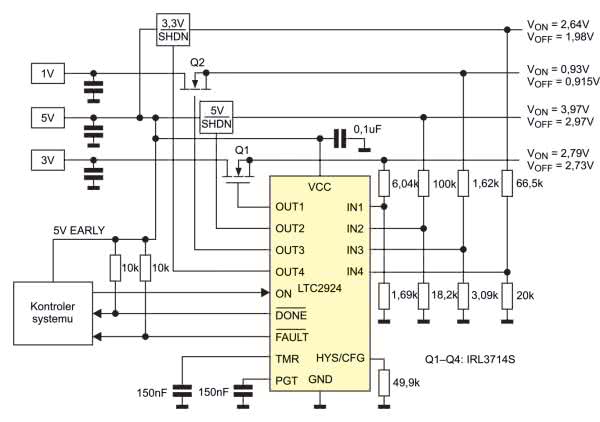

Jeśli używane są niezależne zasilacze, dodatkowy układ sekwencjonowania może zająć się kontrolowanym włączaniem i wyłączaniem poszczególnych stabilizatorów podczas sekwencjonowania domen zasilania. Jednym z przykładów takich elementów jest LTC2924, który może sterować pinami włączającymi np. przetwornice DC/DC do włączania i wyłączania zasilaczy lub sterować tranzystorami (kluczami) MOSFET z kanałem typu N po wysokiej stronie zasilania, aby podłączać i odłączać FPGA do określonej szyny zasilania.

Na rysunku 4 pokazano przykładową aplikację układu LTC2924 w systemie sekwencjonującym zasilanie.

Oprócz sekwencjonowania napięcia, konieczne może być również zagwarantowanie monotonicznego ich wzrostu podczas rozruchu układu. Wymóg ten oznacza to, że napięcie, podczas uruchamiania danej domeny zasilania, musi cały czas rosnąć od zera do wartości nominalnej w jednorodny (najlepiej liniowy) sposób. Jak pokazano na wykresie na rysunku 5, napięcie A rośnie w sposób monotoniczny od zera, a z kolei napięcie B rośnie w sposób niemonotoniczny – po drodze widać lokalny spadek. Może się to zdarzyć, gdy obciążenie danej linii zacznie pobierać duże prądy przy określonym poziomie napięcia podczas uruchamiania. Jednym ze sposobów, aby temu zapobiec, jest umożliwienie dłuższego łagodniejszego rozruchu zasilacza i wybranie przetwornic mocy, które mogą szybko reagować na zmiany impedancji obciążenia i dostarczać duże ilości prądu.

Zasilanie rdzenia

Na ogół, najbardziej energochłonnym elementem układu FPGA będzie główna szyna zasilająca, często oznaczana, jako VCC. Jest to w pełni zrozumiałe, ponieważ podstawowa szyna zasilająca jest połączona z wewnętrzną logiką układu, której praca jest kluczowa dla każdego projektu FPGA. Ponieważ układy FPGA podnoszą poziom skomplikowania tego bloku do naprawdę niezwykłych poziomów, rośnie również wymagana moc do zasilenia tej sekcji.

Na przykład, układy FPGA i SoC 10-tej generacji firmy Intel, układy Intel Arria 10 i Intel Stratix 10 oferują bardzo wysoką gęstość układów logicznych w systemie, związaną z coraz mniejszymi geometriami procesów produkcyjnych, oferują urządzenia z ponad 1 milionem elementów logicznych (LE) w jednym chipie. I chociaż pobór mocy każdego elementu logicznego jest niższy niż w poprzednich generacjach, projekty, które potrzebują dużą część z tych elementów, pracujących przy dużej częstotliwości, mogą wymagać prądów zasilających rdzeń układu przekraczających 100 A.

Oprócz tego, że muszą sprostać wysokim wymaganiom w zakresie dostarczanej mocy, zasilacze sekcji rdzenia muszą również spełniać rygorystyczne wymagania w zakresie dokładności napięcia tak w stanie ustalonym, jak i przejściowym. Wymaganiem w stanie ustalonym jest zdolność do utrzymania stałego napięcia na wejściu rdzenia, niezależnie od tego, w jaki sposób logika rdzenia jest wykorzystywana, czyli, mówiąc prościej, muszą zapewnić wysoką precyzję napięcia, niezależnie od dynamicznie zmieniającego się obciążenia. Na przykład dla napięcia zasilania 0,9 V maksymalna odchyłka napięcia nie może przekroczyć ±30 mV, czyli ±3%.

Wraz z rozwojem technologii FPGA w kierunku coraz mniejszych węzłów procesowych zmniejszać będzie się również dopuszczalna tolerancja napięć zasilających, co oznacza, że zasilacze rdzenia układu programowalnego będą musiały spełniać coraz bardziej rygorystyczne wymagania.

Na wypadkową precyzję stabilizacji napięcia zasilacza wpływają przede wszystkim dwa elementy: dokładność stabilizacji napięcia i tętnienie wyjściowe. Dokładność stabilizacji napięcia jest prostym parametrem i można ją odnaleźć w karcie katalogowej danego elementu (stabilizatora impulsowego lub LDO). Z reguły typowa lub dobra dokładność przetwornicy będzie wynosić nie gorzej niż ±2%.

Tętnienie napięcia to mała, niepożądana zmiana napięcia wyjściowego stabilizatora, która występuje w wyniku przenoszenia energii podczas cykli włączania i wyłączania przetwornicy impulsowej z stabilizatora do obciążenia. Oznacza to, że na tętnienia napięcia ma wpływ nie tylko układ przetwornika, ale także sam zasilany system, w tym układ programowalny i jego komponenty zewnętrzne, które wprowadzają pasożytnicze pojemności i indukcyjności do linii zasilania.

Całkowita odchyłka napięcia, wynikająca z dokładności działania stabilizatora i tętnienia napięcia (w przypadku stabilizatorów impulsowych) musi mieścić się w wymaganej tolerancji napięcia dla sekcji rdzenia, jak i analogicznie, dla innych sekcji zasilanego układu.

Wejścia wrażliwe na szum

Chociaż logika jest podstawowym elementem składowym struktury FPGA, układy programowalne implementują również szereg dodatkowych bloków, takich jak pętle z synchronizacją fazową (PLL), które są używane wewnątrz układu w celu np. wyrównania narastającego zbocza zegara odniesienia z zegarem sprzężenia zwrotnego, oraz szybkie urządzenia nadawczo-odbiorcze (transceivery), które są integralną częścią wielu systemów sieciowych, komunikacyjnych i innych. Te bloki obwodów są wrażliwe na zakłócenia pochodzące z zasilania, ponieważ może to prowadzić do generowania jitteru, co z kolei może powodować niedopuszczalnie wysoki współczynnik błędów bitowych (BER).

Wyzwanie związane z utrzymaniem integralności sygnału jest trudniejsze, ponieważ układy FPGA i aplikacje końcowe, do których są używane, osiągają coraz szybsze prędkości transmisji. W rezultacie wejścia zasilania tych bloków w układzie FPGA wymagają szczególnej uwagi, aby zminimalizować szumy szyny zasilającej. Czasami, jeśli wrażliwa domena zasilania ma takie same wymagania dotyczące napięcia, jak inna domena, można zastosować mały, tani filtr, taki jak np. koralik ferrytowy czy układy RLC. Jednak w wielu przypadkach wymagany jest stabilizator zasilania o dostatecznie niskim poziomie szumów wyjściowych, aby dostarczyć określone, stabilizowane napięcie.

W systemach z układami FPGA używa się najczęściej stabilizatorów liniowych o niskim spadku napięcia (LDO), które na ogół mają wysoki współczynnik odrzucenia wpływu zasilania (PSRR) i z definicji nie generują szumów przełączania. Jednak regulatory liniowe charakteryzują się niską sprawnością, a ponieważ zapotrzebowanie na moc tych bloków cały czas rośnie, a całkowity budżet mocy systemu jest coraz bardziej ograniczony, marnotrawstwo mocy i wytwarzane nadmiernego ciepła może powodować jeszcze gorsze wyzwania w projektowaniu systemu. Dlatego też w tych aplikacjach coraz częściej sięga się po przetwornice impulsowe.

Realizacja układu zasilania

Poprawianie lub regulowanie poziomu napięcia zasilania FPGA wokół domyślnej, zadanej wartości nominalnej jest wymagane w celu np. wprowadzania zmian projektowych w ostatniej chwili, ponownego wykorzystania projektu w innej aplikacji, testowania marginesów płytki czy dynamicznej optymalizacji zużycia energii systemu. Kroki te realizuje się często już na ostatnim etapie projektowania systemu lub nawet podczas pracy prototypu. Lutowanie różnych rezystorów w sieci sprzężenia zwrotnego stabilizatora nie jest ani najszybszym ani też najprostszym rozwiązaniem w takich sytuacjach.

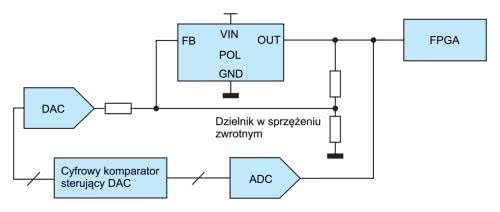

Jedną z metod dostrajania napięcia jest użycie przetwornika cyfrowo-analogowego (DAC) sterującego siecią sprzężenia zwrotnego stabilizatora napięcia (rysunek 6). Aby uzyskać dane pomiarowe na temat napięcia zasilania wychodzącego z stabilizatora skorzystać można dodatkowo przetwornika analogowo-cyfrowego (ADC). Należy oczywiście napisać oprogramowanie i zastosować dodatkowy mały mikrokontroler, aby uzyskać dane pomiarowe i możliwość sterowania napięciem. Oprogramowanie to musi obliczyć prawidłowy kod przetwornika cyfrowo-analogowego, a następnie powoli dostosować wyjście przetwornika cyfrowo-analogowego w celu płynnego regulowania napięcia zasilania, bez zakłóceń i przeregulowania. Tę procedurę poprawiania napięcia należy powtarzać z biegiem czasu, aby zapewnić, że zasilanie nie będzie różniło się od założonego napięcia z powodu np. Dryfowania parametrów komponentów w czasie lub pod wpływem temperatury.

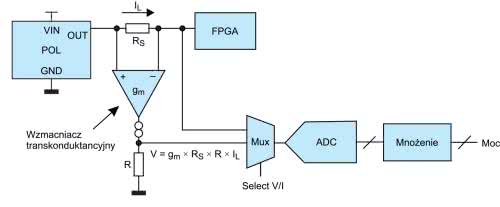

Monitorowanie napięć zasilania, prądów i ewentualne wykrywanie usterek czy anomalii w zachowaniu FPGA ma zasadnicze znaczenie dla zrozumienia stanu systemu i zużycia energii w różnych scenariuszach, ponieważ FPGA jest mózgiem systemu elektronicznego. Takie zrozumienie, w połączeniu z możliwością zmiany napięcia podczas pracy, pozwala uniknąć wielokrotnego poprawiania projektu, oszczędzając koszty i energię. Co więcej, awaria systemu może objawiać się, jako nienormalny trend w zużyciu energii FPGA, ostrzegając kontroler hosta lub personel serwisowy przed awarią płyty lub systemu. Monitorowanie napięcia wymaga przetworników ADC, podczas gdy monitorowanie prądu wymaga również dodatkowych obwodów pomiarowych w postaci wzmacniacza pomiarowego, do pomiaru spadku napięcia na oporniku pomiarowym po wysokiej stronie linii zasilania. Można zastosować np. op-amp w konfiguracji wzmacniacza transkonduktancyjnego, jak pokazano na rysunku 7.

Jest to kompletny system monitorowania linii zasilania układu programowalnego – przetwornik posiada dodatkowo multiplekser, który pozwala na przełączanie pomiędzy pomiarem prądu a pomiarem napięcia zasilania.

Po przeczytaniu powyższej, dosyć złożonej listy wymagań dotyczących sterowania liniami zasilania FPGA wydawać może się, że układy te są bardzo skomplikowane. A nie uwzględniono jeszcze aspektu algorytmicznego – co powinno się stać, gdy na wyjściu POL pojawi się za niskie lub za wysokie napięcie (poza ustalonym przedziałem)? czy należy wyłączać tylko wadliwe zasilanie, czy też inne domeny zasilania? Jak można usunąć błąd, który spowodował awarię modułu?

Jak widać, zarządzanie systemem zasilania FPGA może bardzo szybko się skomplikować, odwracając uwagę od podstawowego elementu w systemie – FPGA. Należy pamiętać, że drzewo mocy dla układu FPGA to tylko część całego systemu zasilania na płycie z duża ilością układów cyfrowych. Większość powyższych wymagań dotyczy również innych urządzeń cyfrowych, takich jak układy ASIC, procesory DSP, układy graficzne, SoC i mikroprocesory. Potrzebne jest rozwiązanie do zarządzania systemem zasilania, które jest proste, skalowalne i elastyczne.

Zakłócenia przejściowe w zasilaniu

Inną cechą charakterystyczną FPGA jest to, że układy te bardzo dynamicznie pobierają prąd, co powoduje powstawanie częstych stanów nieustalonych czy przejściowych na wejściach zasilania. Z tego powodu wiele układów FPGA wymaga bardzo dokładnego filtrowania (odsprzęgania) linii zasilających. Kondensatory ceramiczne są stosowane bardzo blisko między pinami VCORE i GND urządzenia. Wartości do 1 mF są dość powszechne. Tak wysoka pojemność pomaga zmniejszyć wymagania, co do dynamicznej pracy zasilacza, aby zapewnić bardzo wysokie prądy szczytowe.

Jednak wiele stabilizatorów impulsowych i LDO ma określoną maksymalną pojemność wyjściową, z jaką może pracować. Wymagana pojemność wejściowa systemu z FPGA może przekroczyć maksymalną dopuszczalną pojemność wyjściową zasilacza. Zasilacze nie akceptują dużych kondensatorów wyjściowych, ponieważ cała ta bateria elementów podczas rozruchu wygląda dla stabilizatora napięcia jak zwarcie na wyjściu. Istnieje oczywiście rozwiązanie tego problemu. Wystarczy wydłużyć czas łagodnego rozruchu (soft-start), co może pozwolić na niezawodny wzrost napięcia na dużej pojemności, bez przejścia zasilacza w tryb ograniczenia prądu zwarciowego.

Innym powodem, dla którego niektóre przetwornice mocy nie lubią nadmiernej pojemności wyjściowej, jest to, że staje się ona częścią pętli regulacyjnej. Przetwornice ze zintegrowaną kompensacją pętli nie pozwalają na nadmierną pojemność wyjściową, aby zapobiec niestabilności pętli stabilizatora. Często istnieją sposoby wpływania na pętlę sterowania poprzez zastosowanie pojemności sprzężenia zwrotnego np. na rezystorze sprzężenia zwrotnego strony wysokiej, jak pokazano na rysunku 9.

W przypadku przejściowo zmieniającego się obciążenia i niepoprawnego zachowania podczas rozruchu zasilacza, bardzo pomocny w debugowaniu jest łańcuch narzędzi programistycznych, w tym LTpowerCAD oraz LTspice. Jednym z efektów, który dobrze nadaje się do modelowania i symulacji, jest oddzielenie dużych kondensatorów wejściowych układu FPGA od kondensatorów wyjściowych zasilacza.

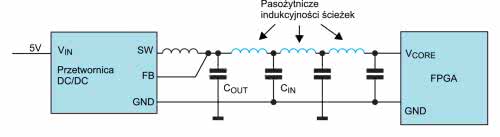

Na rysunku 10 została pokazana ta koncepcja. Chociaż stabilizator POL zwykle znajduje się blisko obciążenia, często między stabilizatorem, a kondensatorem wejściowym FPGA znajduje się ścieżka na płytce drukowanej. Gdy na płycie znajduje się kilka kondensatorów wejściowych FPGA obok siebie, te najbardziej oddalone od zasilacza będą miały mniejszy wpływ na funkcję przejścia pętli stabilizatora, ponieważ występuje między nimi pewna rezystancja, ale także pasożytnicza indukcyjność ścieżki. Te pasożytnicze indukcyjności PCB mogą pozwolić na to, aby pojemność wejściowa FPGA była większa niż maksymalny limit pojemności wyjściowej dla danego zasilacza, nawet, jeśli wszystkie kondensatory są podłączone do tego samego węzła na płycie. W programie LTspice do schematu można dodać pasożytnicze indukcyjności ścieżek i takie efekty również można symulować. Wyniki symulacji są zbliżone do rzeczywistości, gdy w modelowaniu obwodu uwzględnione zostaną komponenty pasożytnicze.

Zasilenie jest problemem systemowym

W przypadku szyn zasilających, które często mają specjalne wymagania dotyczące napięć czy maksymalnego prądu i współdziałania z innymi podsystemami zasilania, ważne jest, aby rozważyć zarządzanie zasilaniem FPGA na jak najwcześniejszym etapie procesu projektowania. Decyzje na poziomie systemu, w tym grupowanie i sekwencjonowanie zasilaczy, sterowanie cyfrowe i projektowanie sprzętu, mają wpływ na sprawność systemu i jego parametry, a także koszty i czas projektowania urządzenia, co wiąże się oczywiście z pewnym ryzykiem projektowym, które można złagodzić przy odpowiednim planowaniu systemu zasilania na poziomie systemowym.

Grupowanie szyn zasilania

Układ FPGA ma pewną liczbę pinów wejściowych, które wymagają odpowiedniego zasilania, ale nie jest konieczne, aby każda szyna zasilania układu programowalnego była wyposażona w dedykowane źródło prądu. Dla każdego układu FPGA jego producent dostarcza dokument, zawierający wytyczne dotyczące każdego z pinów. W dokumencie tym, oprócz podstawowych informacji o każdym pinie znaleźć można również zalecane drzewka zasilania, które grupują różne domeny zasilania, które np. można zasilać z pojedynczego źródła. Przykładowe zalecane drzewko zasilania zaprezentowano na rysunku 11 dla układu Intel Arria 10 GX.

Wszystkie zasilacze i stabilizatory, potrzebne do zasilania układu FPGA, tworzą razem tzw. drzewo zasilania FPGA, które zawiera również specjalne wymagania mające wpływ na wybór i zastosowanie przetwornic mocy i stabilizatorów w systemie. Na przykład wiele zaawansowanych układów FPGA wymaga sekwencjonowania, które opisaliśmy powyżej. Pozwala to na sekwencyjne załączanie poszczególnych zasobów w układzie programowalnym. Zasadniczo wymaga to, aby każdy zasilacz wyposażony był w pin włączający i możliwość komunikowania swojego stanu.

Układy firmy Enpirion, takie jak EN6360QI, oferują możliwość komunikowania się zasilaczy za pomocą pinów Power OK lub Power Good, które można użyć do zasygnalizowania kontrolerowi systemu lub urządzeniu sekwencyjnemu, że zasilacz włączył określone zasoby FPGA i można rozpocząć następny krok sekwencji. Całą sztuką podczas projektowania systemu zasilania i uwspólniania domen zasilania, tj. zasilania ich z pojedynczego stabilizatora, jest zadbanie o to, by wszystkie zasoby, które zasilane są z jednego źródła, mogły być wspólnie załączane. Dodatkowe wymagania, jakie zapisane są w drzewku zasilania, jakie widać na rysunku 11, mogą być spełniane z wykorzystaniem na przykład dodatkowych filtrów dla poszczególnych linii. W zaprezentowanym przykładzie tak uzyskiwane jest napięcie dla pętli PLL (VCCA_PLL) – jest ona zasilana napięciem 1,8 V, stabilizowanym także dla m.in. bloków I/O, które zostało dodatkowo odizolowane filtrem analogowym, gwarantującym niski poziom zakłóceń, docierających do tej linii. Jako filtr linii zasilania wykorzystuje się koraliki ferrytowe, filtry RC, indukcyjności itp.

Sterowanie cyfrowe

Innym powszechnym problemem jest konieczność realizowania tzw. telemetrii. Jest to ogólna nazwa na proces zdalnego pomiaru parametrów pracy systemu i przesyłania ich do podukładów monitorowania. Parametry takie jak napięcie wejściowe, napięcie wyjściowe, prąd wyjściowy, prąd obciążenia i temperatura są cennymi informacjami umożliwiającymi bardziej inteligentne monitorowanie i optymalizację systemu zasilania. Na przykład projektant systemu może wymagać monitorowania prądu obciążenia i temperatury poszczególnych elementów, aby upewnić się, że FPGA działa zgodnie z oczekiwaniami. Innym przykładem jest rejestrowanie zużycia energii przez układ FPGA w różnych konfiguracjach. Pozwala to na dynamiczne ograniczanie wydajności określonego układu FPGA lub części systemu, które mogą nie być potrzebne w celu zmniejszenia poboru prądu przez system, oferując bardziej ekologiczne urządzenie. Ten rodzaj monitorowania stanu systemu można zrealizować na kilka sposobów, ale najłatwiejszym, najtańszym i najbardziej kompaktowym sposobem jest zastosowanie stabilizatora ze zintegrowaną telemetrią i odpowiednią magistralą komunikacyjną.

Układy FPGA, takie jak Intel Arria 10 posiadają specjalne funkcje do redukcji poboru mocy, które zapewniają najniższe zużycie energii, przy zastosowaniu zaawansowanych przetwornic mocy. Podstawowym przykładem jest Smart Voltage ID (SmartVID), funkcja, dzięki której FPGA komunikuje się z kompatybilnym zasilaczem, aby dynamicznie dostosowywać napięcie rdzenia do najniższego możliwego poziomu bez poświęcania wydajności systemu. Kompatybilny zasilacz obsługuje ten system poprzez standardowe interfejsy komunikacyjne, takie jak interfejs VID czy PMBus. Na rysunku 12 został pokazany przykład implementacji SmartVID w systemie z układem programowalnym.

Przykładowym rozwiązaniem zasilania, implementującym tego rodzaju funkcje, jest jednofazowy cyfrowy kontroler Intel ED8101P0xQI z obsługą PMBus, który w połączeniu z wysokoprądowym układem sterownika ET4040QI umożliwia użytkownikom FPGA wdrażanie szerokiej gamy funkcji telemetrii i redukcji mocy. Pozwala on między innymi na:

- Monitorowanie parametrów wejściowych i wyjściowych systemu, takich jak napięcie, prąd i temperatura;

- Monitorowanie usterek systemu, takich jak przepięcia czy zapady napięcia oraz nadmierną temperaturę poszczególnych jego elementów;

- Dynamiczną regulację napięcia wyjściowego w celu obsługi SmartVID.

Aby zaimplementować SmartVID, układ FPGA określa żądane napięcie VCC i komunikuje się z układem stabilizatora napięcia za pomocą interfejsu PMBus, który dostosowuje napięcie wyjściowe do aktualnych wymagań. Korzystając z rozwiązań Enpirion, kontroler zarządzania energią można zaimplementować za pomocą ED8101P0xQI, a stabilizator(y) napięcia można zaimplementować za pomocą układów ET4040QI tej firmy.

Hardware

Wczesne planowanie drzewa mocy dla projektu FPGA ma kluczowe znaczenie, ponieważ istnieje wiele implikacji projektowych sprzętu systemowego, które mogą wpływać na złożoność projektu, czas cyklu projektowego i jego koszty. Chociaż dokładne wymagania dotyczące zasilania są niemożliwe do określenia na początku projektowania urządzenia, dokładne przemyślenie szacunków zużycia energii przez FPGA umożliwia użytkownikowi stworzenie drzewa mocy, które jest bliskie ostatecznemu, optymalnemu projektowi.

Pierwszą korzyścią z takiego podejścia jest to, że projektant sprzętu będzie w stanie prawidłowo umieścić wymagane elementy mocy nawet na początkowych projektach płytek. Jest to ważne, ponieważ systemy FPGA stają w obliczu coraz większych wyzwań związanych z gęstością elementów na PCB, ponieważ użytkownicy dodają coraz więcej funkcji, a tym samym coraz więcej komponentów, jednocześnie zmniejszając rozmiary samego urządzenia. Jeśli drzewo mocy nie zostanie odpowiednio zaplanowane podczas projektowania PCB, użytkownicy stają przed ryzykiem konieczności umieszczenia przetwornic mocy w nieidealnych lokalizacjach na PCB, na przykład z dala od FPGA, co ma poważne wady. Stabilizatory zasilania, umieszczane w ograniczonej przestrzeni PCB w niewłaściwym obszarze płytki, gdzie np. chłodzenie czy odległość od FPGA stanowią trudne wyzwania sprzętowe, przekładają się m.in. na konieczność stosowania większych, droższych kondensatorów filtrujących czy niższą sprawność energetyczną systemu. Co gorsza, projektant może w ogóle nie mieć wystarczającej ilości miejsca na większe przetwornice czy stabilizatory zasilania.

Drugą korzyścią wczesnego planowania drzewa mocy jest osiągnięcie wystarczającej elastyczności projektowej, aby spełnić wymagania dotyczące zużycia energii końcowego projektu FPGA bez konieczności znacznego przeprojektowania. Podstawową kompetencją FPGA jest możliwość integracji funkcji i możliwości, nawet w ramach cyklu projektowania, a większa integracja prowadzi do większego zużycia energii. Skalowanie i optymalizacja początkowego drzewa mocy, które jest bliskie ostatecznemu projektowi, jest znacznie łatwiejsze i szybsze niż projektowanie nowego drzewa mocy, gdy początkowy projekt był zbyt niedokładny. W świecie, w którym firmy są pod presją, aby dostarczać produkty w możliwie najkrótszym czasie, minimalizacja ryzyka, kosztów i dodatkowego czasu potrzebnego na zmianę źle zaplanowanego drzewka mocy jest ogromną zaletą, która może umożliwić projektantom systemów uzyskanie przychodów szybciej niż konkurencja.

Podsumowanie

Na pytanie, w jaki sposób użytkownik zasila swoje FPGA, można odpowiedzieć tylko „to zależy”. Zrozumienie, w jaki sposób konstrukcja i użytkowanie systemu z układem programowalnym wpływa na zużycie energii i wymagania dotyczące zasilania, może przynieść mniej frustracji podczas projektowania urządzenia. Zużycie energii przez FPGA jest dyktowane przez statyczne i dynamiczne wymagania dotyczące zasilania, z których te drugie zależą w dużym stopniu od unikalnego projektu FPGA. Jednak, niezależnie od projektu, istnieją pewne wspólne wymagania dotyczące projektowania zasilaczy FPGA, które można wykorzystać do uproszczenia i ukierunkowania decyzji projektowych systemu. Dedykowane rozwiązania zasilania projektowane są tak, aby sprostać tym trudnym wymaganiom, dlatego dobrze jest korzystać z dedykowanych do układów FPGA kontrolerów czy układów PMIC.

Zastosowanie przetwornic mocy o niskich tętnieniach wyjściowych i szybkim czasie reakcji może zapewnić spełnienie rygorystycznych wymagań dotyczących statycznego i dynamicznego stabilizowania napięcia rdzenia, zapewniając bezproblemową pracę we wszystkich warunkach. Podobnie, zastosowanie niskoszumowych stabilizatorów LDO do czułych domen zasilania FPGA może zapewnić osiągnięcie celów związanych z integralnością sygnału, sprawnością energetyczną i odpowiednim budżetem termicznym. Wreszcie, wdrożenie zróżnicowanych funkcji systemu, takich jak telemetria i redukcja mocy, jest możliwe dzięki zastosowaniu zaawansowanych konwerterów mocy z cyfrowymi sterownikami, które pozwalają na komunikację poprzez interfejsy takie jak PMBus.

Z uwagi na elastyczność konstrukcji FPGA, zasilanie jest naprawdę problemem na poziomie całego systemu, wymagającym wysiłku, aby oszacować zużycie energii i zaprojektować drzewko mocy tak, aby jak najprościej spełnić unikalne wymagania danego projektu. Korzyścią jest bardziej optymalny projekt systemu, który można skończyć szybciej, przy mniejszych zasobach i przy odpowiedniej charakterystyce wydajności. To wszystko zapewnia silną przewagę nad konkurencyjnymi rozwiązaniami.

Nikodem Czechowski, EP

- Bibliografia:

Amanda Alfonso, „Understanding and Meeting FPGA Power Requirements”, White Paper, Intel, 2017

Frederik Dostal, „Power Management for FPGAs”, Analog Dialogue 52-03, marzec 2018

Pinkesh Sachdev, „FPGA Power System Management”, Design Notes DN21944, Analog Devices, 2020

Hichem Belhadj, Vishal Aggrawal, Ajay Pradhan, Amal Zerrouki, „Power-Aware FPGA Design”, Actel, 2009.

Zaloguj

Zaloguj