- Zasilanie: 5 V/500 mA (min.)

- Częstotliwość próbkowania: 44,1 kHz/48 kHz/88,2 kHz/96 kHz (zależnie od zastosowanego rezonatora kwarcowego)

- Wejścia analogowe: liniowe stereo (jack 3,5 mm + SIP)

- Wyjścia analogowe: 2× liniowe stereo 0,9 Vrms (Jack 3,5 mm + SIP)

- Gniazda do podłączenia zewnętrznych modułów I²S i I²C

- Wbudowane dioda LED (wskaźnik zasilania + 2× dioda sterowana z GPIO procesora)

- Dwa przyciski monostabilne oraz podwójny przełącznik DIP do obsługi przez procesor

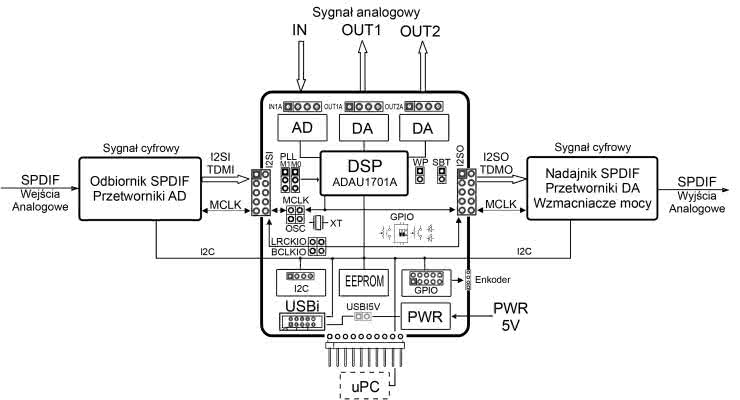

DSP1701A_DSP_MK2 jest przystępną cenowo platformą sprzętową dla procesora sygnałowego Analog Devices ADAU1701A, należącego do rodziny SigmaDSP. Zestaw wraz z programatorem USBi (EVAL-ADUSB2EBZ) i darmowym środowiskiem SigmaStudio umożliwia obróbkę sygnału audio zarówno ze źródeł analogowych, jak i cyfrowych (SPDIF/I²S). Modułowa budowa zestawu DSP1701A_DSP_MK2 umożliwia elastyczne dopasowanie zasobów sprzętowych do wymogów aplikacji, ułatwiając szybką rozbudowę funkcjonalną przy zastosowaniu modułów z przetwornikami AD/DA, odbiornikami/nadajnikami SPDIF, wielokanałowymi cyfrowymi końcówkami mocy oraz innymi modułami – opracowanymi według własnego pomysłu lub gotowymi z oferty AVT, Digilent itp. Jednocześnie szczególny nacisk położono na możliwość pracy samodzielnej przy zastosowaniu wbudowanych przetworników AD/DA zawartych w strukturze ADAU1701A i elementów manipulacyjnych zainstalowanych na płytce.

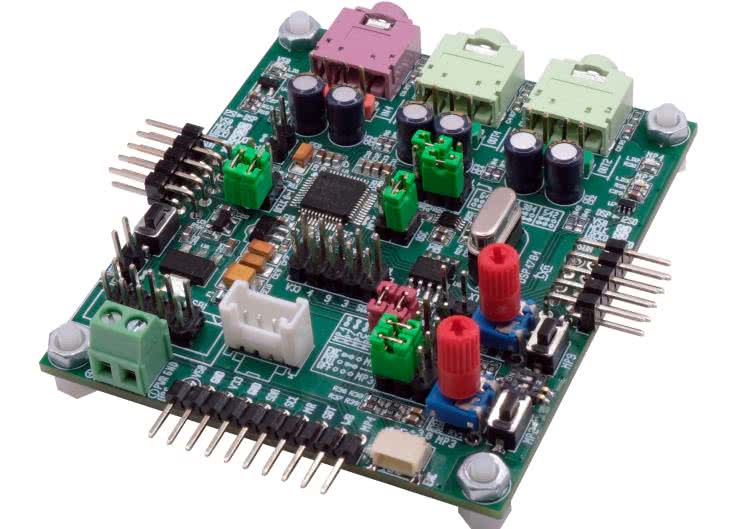

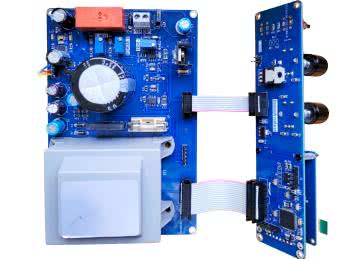

Wygląd płyty głównej zestawu zaprezentowano na fotografii 1 (otwierającej artykuł).

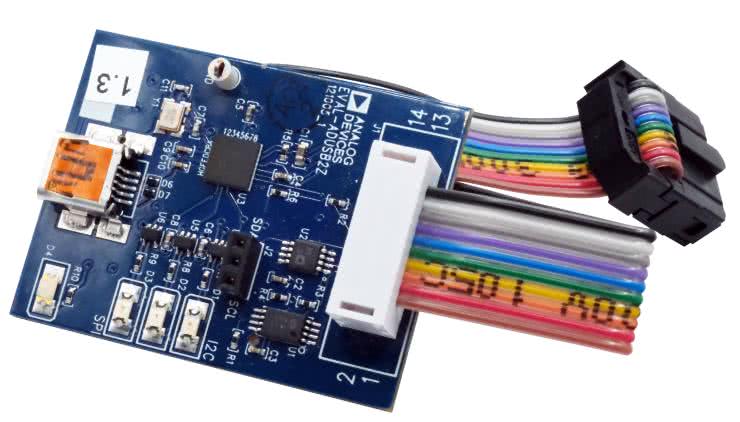

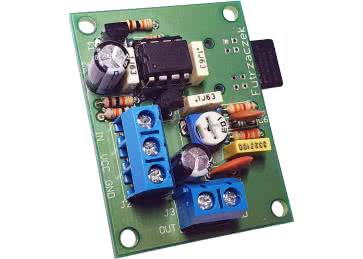

Do rozpoczęcia pracy z DSP1701A_DSP_MK2 konieczny jest jeszcze programator USBi, którego wygląd pokazano na fotografii 2. Umożliwia on pełną konfigurację sprzętową ADAU1701A, symulację w czasie rzeczywistym oraz programowanie pamięci programu (EEPROM), niezbędnej do realizacji trybu pracy samodzielnej SELFBOOT oraz dodatkowo konfigurację (poprzez magistralę I²C) układów audio produkowanych przez Analog Devices. Aktualnie dostępna jest wersja 1.5 programatora, ale wszystkie starsze także bezproblemowo współpracują z płytką DSP1701A_DSP_MK2.

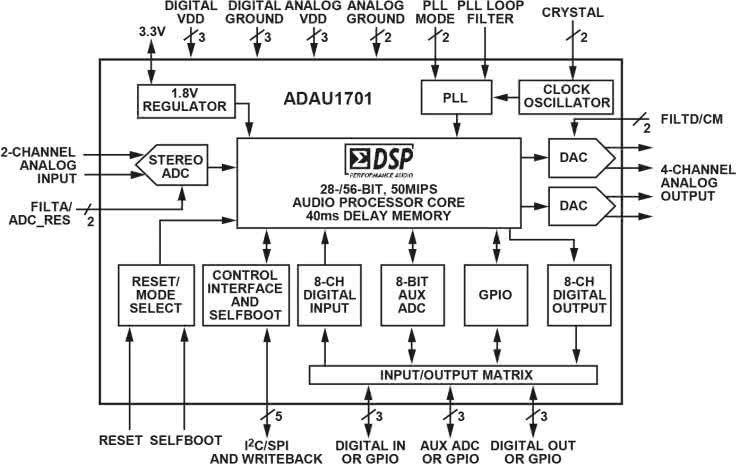

Aby w pełni wykorzystać możliwości zestawu DSP1701A_DSP_MK2, konieczne jest zapoznanie się z budową blokową jego serca, czyli procesora DSP ADAU1701A. Jest to w zasadzie nie tylko procesor DSP, ale cały zintegrowany system cyfrowej obróbki sygnału audio, wyposażony w przetworniki AD/DA, uniwersalne porty GPIO oraz cyfrowe interfejsy audio. Schemat wewnętrzny ADAU1701A zaprezentowano na rysunku 1.

Najistotniejsze cechy procesora ADAU1701A to:

- wydajność obliczeniowa 50 MIPS, 28-/56-bitowy rdzeń DSP,

- wbudowany oscylator i konfigurowalny blok PLL,

- obsługa częstotliwości próbkowania do 192 kHz,

- wbudowane dwa niezależne przetworniki AD 24 bit (SNR 100 dB),

- wbudowane cztery niezależne przetworniki DA 24 bit (SNR 104 dB),

- dwukierunkowy interfejs cyfrowy (8 kanałów) z możliwością elastycznej konfiguracji trybów I²S, LJ, RJ oraz wielokanałowego trybu multipleksowanego czasowo (TDM),

- programowalne GPIO, w tym cztery wejścia analogowe AD do realizacji interfejsów użytkownika bez konieczności zastosowania procesora zewnętrznego,

- obsługa zewnętrznej pamięci programu i konfiguracji I²C EEPROM,

- możliwa samodzielna praca DSP (tryb SELFBOOT) bez zewnętrznego procesora sterującego,

- tryb WRITEBACK umożliwiający zachowanie parametrów aplikacji DSP w pamięci EEPROM przy pracy samodzielnej (nawet po zaniku napięcia zasilania),

- zasilanie 3,3 V, wbudowany stabilizator do zasilania rdzenia DSP 1,8 V,

- konfiguracja i oprogramowanie za pomocą intuicyjnego, graficznego środowiska Sigma Studio (aktualnie V4.7).

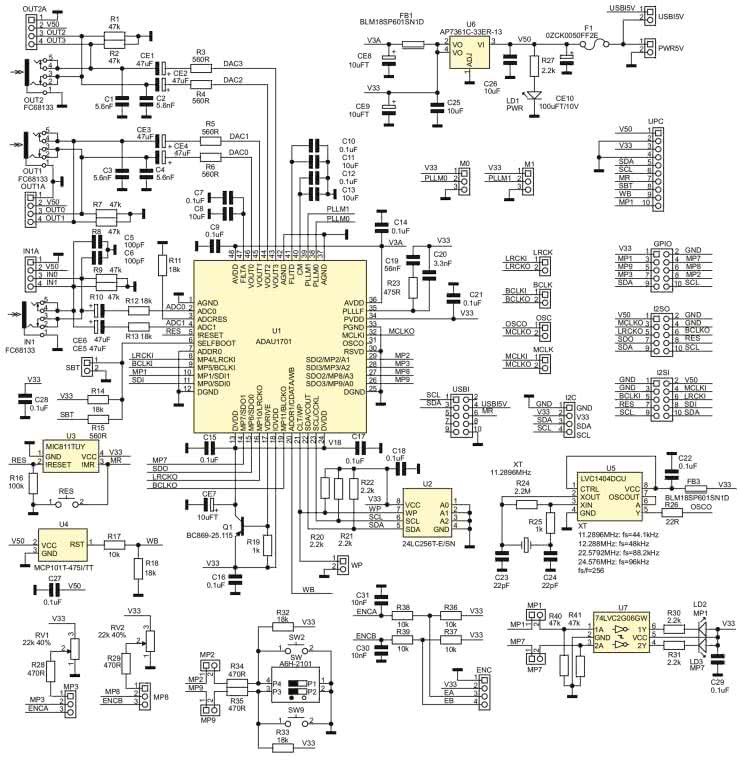

Schemat blokowy zestawu, ilustrujący przepływ sygnałów audio, sterujących oraz połączenia pomiędzy poszczególnymi modułami pokazano na rysunku 2, natomiast schemat ideowy zestawu DSP1701A_DSP_MK2 – na rysunku 3.

Płytka bazowa umożliwia bezpośrednią obróbkę analogowego sygnału audio doprowadzonego do gniazda wejściowego IN1 typu jack 3,5 mm stereo lub do złącza IN1A typu SIP4. Sygnał audio po separacji składowej stałej doprowadzony jest do wbudowanego przetwornika AD. Rezystory R11, R12, R13 i wbudowany w AD szeregowy rezystor 2 kΩ ustalają impedancję wejściową AD na ok. 20 kΩ i czułość na 2 Vrms dla częstotliwości próbkowania fs=48 kHz. Ewentualne zmiany wartości i sposób ich obliczenia dla innych częstotliwości próbkowania i czułości podany jest w karcie katalogowej ADAU1701A w rozdziale zatytułowanym „Audio ADC”. Rzeczywista wartość impedancji wejściowej dla sygnału audio będzie pomniejszona o równolegle połączone z AD rezystory R9, R10. Należy być świadomym, że ze względu na możliwość zmiany częstotliwości próbkowania AD wejścia pozbawione są filtrów antyaliasingowych. W większości aplikacji można z nich zrezygnować, jeżeli jednak w sygnale wejściowym obecne są składowe o częstotliwości większej od fs/2, należy zastosować zewnętrzny filtr dolnoprzepustowy podłączony w szereg ze źródłem sygnału audio, o częstotliwości dobranej do fs procesora DSP.

Sygnał wyjściowy z przetworników DA doprowadzony jest odpowiednio do gniazd jack 3,5 mm stereo OUT1 (DAC0/1) i OUT2 (DAC2/3) oraz – podobnie jak w przypadku wejść – dostępny jest także na złączach SIP4, OUT1A/2A. Wyprowadzenie sygnału audio wraz z zasilaniem 5 V na złącza SIP4 ułatwia użycie zewnętrznych analogowych przedwzmacniaczy (w tym mikrofonowych), miniaturowych końcówek mocy (na przykład tych opisanych w EP 5/2019) i innych miniaturowych modułów do aplikacji audio. Maksymalny poziom sygnału wyjściowego przetwornika DA to 0,9 Vrms. Elementy R3, R4 z C1, C2 oraz R5, R6 z C3, C4 stanowią podstawowy filtr dolnoprzepustowy przetwornika DA. Podobnie w tym przypadku – jeżeli zależy nam na uzyskaniu możliwie najlepszych parametrów (S/N), do wyjścia należy podłączyć zewnętrzny filtr dolnoprzepustowy, eliminujący artefakty przetwarzania DA leżące poza pasmem akustycznym.

Moduł ma wbudowany zasilacz dostarczający napięcia zasilania do wszystkich elementów płytki oraz modułów rozszerzeń podłączonych do złączy I2SI, I2SO. Płytka wymaga zasilania napięciem 5 V o minimalnej obciążalności 500 mA. Napięcie to należy doprowadzić do złącza PWR5V. Alternatywnie, podczas testów na potrzeby aplikacji o niewielkim poborze mocy, można zastosować programator USBi, pozostawiając założoną zworę USBI5V.

Napięcie 5 V z wybranego źródła doprowadzone jest przez bezpiecznik polimerowy F1 (500 mA) do stabilizatora LDO U6 typu AP7631C-33. Jeżeli mamy w planach zastosowanie nawet niewielkich wzmacniaczy mocy, należy zmienić wartość bezpiecznika F1, w zależności od wymagań na 1 A lub 2 A, stosując bezpieczniki polimerowe typu, odpowiednio: 0ZCK0100FF2E lub PTSLR08058V200 (pobieranie większych prądów nie jest zalecane). W tym przypadku należy zdjąć zworę USBI5V, aby nie dopuścić do przeciążenia i uszkodzenia programatora USBi. Układ U6 stabilizuje napięcie 3,3 V (V33) do zasilania obwodów cyfrowych płytki, a dodatkowy obwód FB1, CE8 zapewnia filtrację napięcia V33A dla obwodów analogowych DSP. Dioda LD1 sygnalizuje obecność zasilania 5 V. Pojemności na szynach zasilania V33, V33A zapewniają odpowiednie odsprzęganie współpracujących wyprowadzeń U1. ADUA1701A ma wbudowany regulator napięcia 1,8 V służący do zasilania rdzenia DSP, którego elementem wykonawczym jest tranzystor Q1 z rezystorem R19. Elementy C15, C17 i CE7 odsprzęgają napięcie V18.

Obwód zasilania uzupełniają dwa układy nadzorujące. Pierwszy – U3 typu MIC811 – monitoruje linię V33 i zapewnia poprawny reset (sygnał RES) układu ADAU1701A po włączeniu zasilania. Wejście MR układu U1, służące do manualnego generowania sygnału RES, podłączone jest do mikroprzełącznika RES oraz do wyjścia RESET programatora USBi, co umożliwia programowe restartowanie ADAU1701, np. po zaprogramowaniu. Drugim układem nadzorującym jest U4 typu MCP101T-475, odpowiedzialny za detekcję zaniku zasilania 5 V. Gdy napięcie spadnie poniżej ok. 4,63 V, U4 generuje narastające zbocze sygnału WB, służące do uruchomienia jednorazowej procedury WRITEBACK, odpowiedzialnej za zapis aktualnych parametrów DSP do nieulotnej pamięci EEPROM w trybie pracy samodzielnej SELFBOOT. Czas niezbędny na poprawny zapis gwarantują odpowiednio dobrane kondensatory filtrujące CE9, CE10.

Jak każdy procesor, także ADAU1701A wymaga do pracy sygnału zegarowego. W przypadku modułu DSP1701A_DSP_MK2 obwód taktujący został nieco rozbudowany, zrezygnowano bowiem z użycia wbudowanego układu generatora współpracującego z kwarcem podłączonym do wyprowadzeń MCLKI i OSCO procesora DSP na rzecz generatora zewnętrznego. Za wytwarzanie sygnału zegarowego MCLK, o częstotliwości zależnej od wymaganej częstotliwości próbkowania fs, odpowiada układ U5 typu LVC1404, współpracujący z kwarcem XT. U5 zawiera w swojej strukturze obwód oscylatora współpracującego z kwarcem, obwód bramkowania generatora oraz bramki buforowe. W zależności od częstotliwości próbkowania fs, należy użyć rezonatora kwarcowego o odpowiedniej częstotliwości: dla fs=44,1 kHz (zgodna ze standardem CD) jest to 11,2896 MHz, dla fs=48 kHz to 12,288 MHz oraz odpowiednio dla 88,2 kHz i 96 kHz; to 22,5792 MHz i 24,576 MHz (dla mnożnika fs=256), dlatego warto zdobyć podstawkę pod kwarc w obudowie HC49, co znacząco ułatwia szybkie zmiany podczas eksperymentów.

Układ generatora uzupełniają dwie zwory OSC i MCLK, odpowiedzialne za konfigurację i dystrybucję sygnału zegarowego. Zwarta zwora OSC łączy wejście zegarowe DSP z wyjściem generatora – jest to podstawowa konfiguracja. W tym przypadku buforowany sygnał zegarowy MCLKO doprowadzony jest także do złącza wyjściowego I2SO interfejsu cyfrowego i może służyć do taktowania przetworników DA wymagających dostarczenia sygnału MCLK. Zwarta zwora MCLK umożliwia doprowadzenie sygnału MCLKO także do złącza wejściowego interfejsu cyfrowego I2SI, co jest bardzo przydatne, gdy współpracujący przetwornik AD wymaga zewnętrznego sygnału MCLK.

Odłączenie wbudowanego generatora za pomocą zwory OSC umożliwia współpracę DSP z zewnętrznym sygnałem zegarowym, dostarczanym z interfejsu wejściowego I2SI lub wyjściowego I2SO. Dokładny opis konfiguracji zostanie zaprezentowany w części kursu opisującej korzystanie z interfejsów cyfrowych audio. Układ ADAU1701 ma wbudowany obwód PLL służący do wytwarzania wewnętrznych sygnałów taktujących na podstawie sygnału MCLK – za konfigurację mnożników PLL odpowiadają zwory M0, M1. Domyślnie wybrany powinien być mnożnik 256, co w przypadku kwarcu 12,288 MHz odpowiada częstotliwości próbkowania 48 kHz (fs*256). Elementy R23, C19, C20 tworzą filtr pętli PLL i powinny wykazywać niską tolerancję, co zapewni stabilną pracę pętli.

ADAU1701A ma wbudowane dwa interfejsy cyfrowego audio, jeden 8-kanałowy wejściowy (dostępny na wyprowadzeniach SDI0…3) i jeden 8-kanałowy wyjściowy na wyprowadzeniach SDO0…3. Wyprowadzenia SDI/O, ze względu na ograniczoną liczbę pinów obudowy LQFP48, są współdzielone z GPIO. Kanały SDI0 oraz SDO0, które mogą pracować także w trybie TDM, wyprowadzono odpowiednio na złącza I2SI, I2SO. Zapewniona jest więc spora elastyczność w zakresie doboru współpracujących zewnętrznych przetworników AD/DA i uproszczona część sprzętowa, przy zachowaniu możliwości jednoczesnego przesyłania danych w wielu kanałach w trybie TDM. Wystarczy zastosowanie zaledwie jednej linii sygnałowej i dwóch taktujących. Interfejs cyfrowy uzupełniają sygnały zegarowe LRCK, BCLK oraz – wyprowadzone na złącza I2SI, I2SO – zasilanie 5 V, sygnał RES i magistrala I²C. Należy pamiętać, że sygnały wyprowadzone na złącza interfejsów cyfrowych zgodne są z poziomami logicznymi 3,3 V i podłączenie tam napięcia wyższego zakończy się uszkodzeniem DSP. Wyprowadzenie szyny 5 V umożliwia zasilanie części analogowych współpracujących układów oraz umożliwia wykorzystanie lokalnych stabilizatorów LDO do uzyskania np. napięcia 3,3 V bez dodatkowego obciążania stabilizatora U6, zamontowanego na płytce bazowej.

ADAU1701A, w przypadku interfejsu wejściowego, dopuszcza tylko pracę w trybie slave, w którym sygnały taktujące LRCK, BCLK muszą być doprowadzone do DSP. Aby nie wymuszać dodatkowej komplikacji współpracujących układów AD oraz zachować synchroniczność sygnałów interfejsu cyfrowego, do taktowania można użyć odpowiednio skonfigurowanego w trybie master interfejsu wyjściowego – zwory LRCK, BCLK łączą w tym przypadku wejściowe i wyjściowe sygnały LRCK/BLCK. Traci się w ten sposób dwa wyprowadzenia, ale oszczędza na zewnętrznym układzie generującym sygnały taktujące interfejs. Jest to opcja bardzo przydatna, jeżeli przetwornik AD pracuje tylko w trybie slave (wymaga dostarczenia sygnałów taktujących), nie koliduje to oczywiście z możliwością pracy interfejsu wyjściowego z przetwornikiem DA w trybie master, zapewniając możliwość prostego dodania dodatkowych kanałów analogowych. Podczas normalnej eksploatacji zwory LRCK, BLCK powinny być zdjęte, aby nie dopuścić do uszkodzenia wyprowadzeń DSP w przypadku błędnej konfiguracji.

DSP ma możliwość pracy samodzielnej bez konieczności stosowania zewnętrznego procesora konfiguracyjnego. Do przechowywania konfiguracji i parametrów służy pamięć EEPROM U2 typu 24LC256. Zdjęta zwora WP blokuje możliwość zapisu do pamięci (stan wysoki wejścia WP EEPROM). Wyprowadzenie CLT/WP umożliwia ominięcie blokady zapisu parametrów wymuszonych procedurą WRITEBACK. Zwora SBT określa tryb pracy procesora: z zewnętrzną konfiguracją przez I²C (zwora SBT zwarta) lub z konfiguracją samodzielną, pobieraną z pamięci EEPROM (zwora I²C rozwarta). Stan wysoki wyprowadzenia SBT, odczytany w czasie aktywacji sygnału RESET, przełącza procesor w tryb pracy samodzielnej SELFBOOT.

ADAU1701A ma konfigurowalne wyprowadzenia GPIO pracujące z poziomami logicznymi 3,3 V, które wraz z napięciem zasilania 3,3 V dostępne są na złączu GPIO. Udostępnione zostały wyprowadzenia MP1, MP2, MP3 oraz MP7, MP8, MP9 ADAU1701A. Przypisanie sygnałów umożliwia wykorzystanie pozostałych interfejsów cyfrowych, wyprowadzeń GPIO oraz wbudowanego przetwornika AD dostępnego przez GPIO, zwiększając funkcjonalność modułu. Aby ułatwić eksperymenty z DSP, płytka uzupełniona została o elementy interfejsu użytkownika: dwie buforowane diody LED podłączone do wyprowadzeń MP1, MP7, dwa potencjometry podłączone do MP3, MP8 współdzielone z interfejsem enkodera, dwa przyciski chwilowe i przełącznik DIP podłączone wspólnie do MP2, MP8. Elementy R36...R39, C30, C31 filtrują i polaryzują styki A/B enkodera obrotowego, który może zostać podłączony do złącza ENC. Interfejs enkodera stanowi jeden ze standardowych sposobów interakcji z użytkownikiem i jest przez ADAU1701A obsługiwany przy użyciu bibliotek z SigmaStudio. Ze względu na współdzielenie wyprowadzeń MP3, MP8 z potencjometrami obrotowymi, wybór realizowanej funkcji zależny jest od położenia zwory MP3, MP8. W przypadku użycia enkodera zwory należy ustawić w położeniu oznaczonym jako ENC. Ze względu na ograniczoną liczbę wyprowadzeń MPx nie są wtedy dostępne potencjometry. Zdjęcie zworek z MP3, MP8 odłączy obwody potencjometrów oraz enkodera i umożliwi zastosowanie wyprowadzeń do innych celów.

Każde z wyprowadzeń może zostać odłączone za pomocą zwory o odpowiednim numerze, co zapewnia separację i niezakłócone funkcjonowanie wyprowadzeń MPx, gdy podłączony element interfejsu użytkownika nie jest wykorzystywany.

Płytkę uzupełniają: złącze magistrali I²C zgodnej z Grove 3,3 V oraz złącze UPC z wyprowadzonymi najważniejszymi funkcjonalnie sygnałami sterującymi DSP, przeznaczone do współpracy z zewnętrznym procesorem.

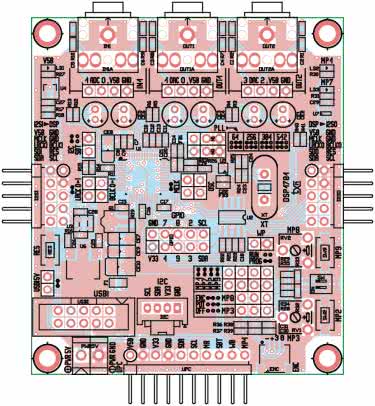

Moduł zmontowano na czterowarstwowej płytce drukowanej z wydzielonymi wewnętrznymi płaszczyznami masy i zasilania. Rozmieszczenie elementów DSP1701A_DSP_MK2 pokazano na rysunku 4.

Montaż nie wymaga opisu, polecam zgodnie z wcześniejszymi zaleceniami wlutować podstawkę pod kwarc HC49 oraz uzupełnić zestaw kwarców o częstotliwości 11,2896 MHz, 22,5792 MHz i 24,576 MHz, co umożliwi eksperymenty z różnymi częstotliwościami próbkowania.

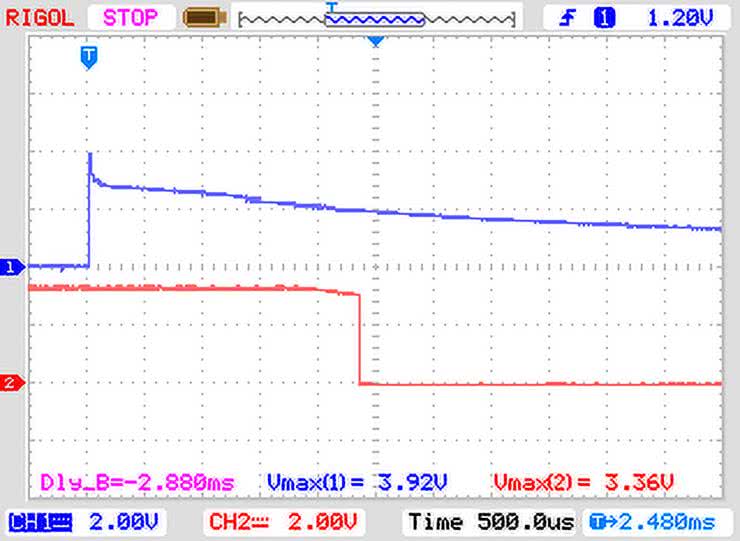

Po wlutowaniu elementów i zmyciu resztek topnika płytka nie wymaga specjalnego uruchamiania. Każdorazowo warto jednak sprawdzić obecność napięć zasilających. Po domyślnym ustawieniu zwory OSC w pozycji zwartej, wybraniu dzielnika 256 za pomocą zwory PLL (zgodnie z opisem na PCB) i usunięciu pozostałych zwór, można podłączyć do złącza PWR5V zasilacz 5 V/500 mA i sprawdzić obecność napięć 5 V, 3,3 V, 1,8 V w odpowiadających punktach układu oraz sprawdzić obecność sygnału zegarowego OSC zgodnego z użytym kwarcem (domyślnie 12,288 MHz). Warto sprawdzić poprawność działania układów: U3 generującego sygnał resetu RES oraz U4 generującego sygnał WB. Podczas zaniku zasilania 5 V powinna być możliwa do zaobserwowania sekwencja sygnałów WB (niebieski) i RES (czerwony) zgodnie z rysunkiem 5.

To wszystko co jest możliwe do sprawdzenia bez zaprogramowania układu ADAU1701A.

W przyszłym miesiącu zaprezentowany zostanie opis instalacji i użytkowania środowiska programowego Sigma DSP w wersji 4.7. Zapraszamy do lektury.

Adam Tatuś, EP

- R1, R2, R7...R10, R40, R41: 47 kΩ

- R3...R6, R15: 560 Ω

- R11...R14, R18, R32, R33: 18 kΩ

- R16: 100 kΩ

- R17, R36...R39: 10 kΩ

- R19, R25: 1 kΩ

- R20...R22, R27, R30, R31: 2,2 kΩ

- R23: 475 Ω

- R24: 2,2 MΩ

- R26: 22 Ω

- R28, R29, R34, R35: 470 Ω

- RV1, RV2: 22 kΩ (potencjometr leżący + pokrętło, CA6V)

- C1...C4: 5,6 nF (SMD 0603, NP0, 16 V)

- C5, C6: 100 pF (SMD 0603, NP0, 16 V)

- C7, C9, C10, C12, C14...C18, C21, C22, C27...C29: 100 nF (SMD 0603, X7R, 10 V)

- C8, C11, C13, C25, C26: 10 μF (SMD 0603, X7R, 10 V)

- C19: 56 nF (SMD 0603, X7R, 10 V)

- C20: 3,3 nF (SMD 0603, NP0, 16 V)

- C23, C24: 22 pF (SMD 0603, NP0, 16 V)

- C30, C31: 10 nF (SMD 0603, X7R, 10 V)

- CE1...CE6: 47 μF (elektrolityczny R=2 mm, D=5 mm)

- CE7...CE9: 10 μF/10 V (SMD A 3216, tantalowy)

- CE10: 100 μF/10 V (SMD B 3528, tantalowy)

- LD1: dioda LED zielona (SMD 0603)

- LD2, LD3: dioda LED czerwona (SMD 0603)

- U1: ADAU1701

- U2: 24LC256T-E/SN

- U3: MIC811TUY

- U4: MCP101T-475I/TT

- U5: SN74LVC1404DCUR

- U6: AP7361C-33ER-13

- U7: 74LVC2G07GW.125

- Q1: BC869-25.115 (PNP)

- BCLK, LRCK, MCLK, MP1, MP2, MP7, MP9, OSC, USBI5V, WP, SBT: złącze SIP 2 pin + jumper, proste 2,54 mm

- ENC: złącze JST 1 mm, SM04B, kątowe

- F1: bezpiecznik PTC, typ 0ZCK0050FF2E (SMD 0805) – patrz opis

- FB1, FB3: dławik ferrytowy SMD, typ BLM18SP601SN1D (SMD 0603)

- GPIO, USBI: złącze SIP 2×5 pin, proste 2,54 mm

- I2C: złącze Grove THT proste

- I2SI, I2SO: złącze SIP 2×5 pin, kątowe 2,54 mm

- IN1: złącze Jack 3,5 mm stereo (czerwone), typ FC68133

- M0, M1, MP3, MP8: złącze SIP 1×3 pin + jumper, proste 2,54 mm

- OUT1, OUT2: złącze Jack 3,5 mm stereo (zielone), typ FC68133

- IN1A, OUT1A, OUT2A: złącze SIP 1×4 pin, proste 2,54 mm

- PWR5V: złącze śrubowe DG 2 pin 3,5 mm (typ DG381-3.5-2)

- SW: przełącznik DIP 2 pozycje (A6H-2101)

- SW2, SW9, RES: TACT switch SMD (DTSM31)

- UPC: złącze kątowe SIP10 2,54 mm

- XT: kwarc HC49U niski 11,2896 MHz

Zaloguj

Zaloguj