- Podstawowe parametry:

- zastosowany układ FPGA to 0M04SAE144C8G z rodziny Intel MAX10,

- układ FPGA wyposażony w cztery tysiące elementów logicznych LE,

- pamięć RAM o rozmiarze 189 Kb pamięci (w 21 blokach po 9 Kb),

- 1248 Kb pamięci Flash dzielonej pomiędzy bitstream oraz aplikację użytkownika,

- programowanie poprzez interfejs JTAG przy użyciu, np. programatora USB Blaster,

- wbudowany konwerter USB-UART,

- zasilanie poprzez złącze miniUSB.

Układy FPGA z rodziny MAX10 mają kilka ciekawych rozwiązań, rzadko występujących w innych podzespołach tego typu, które przekonują do stosowania tych układów we własnych projektach. Pierwszą zaletą jest zintegrowana nieulotna pamięć Flash. Pozwala nie tylko na przechowywanie konfiguracji, ale może być także dostępna dla aplikacji w czasie pracy układu. Drugim elementem ułatwiającym stosowanie układów MAX10 jest możliwość zasilania za pomocą tylko jednego napięcia 3,3 V. Równie istotną cechą jest dostępność podzespołów w łatwej do montażu obudowie EQFP. Dzięki temu zaprojektowanie i wykonanie PCB jest znacznie łatwiejsze niż w przypadku podobnych układów w obudowie BGA. Układy są dostępne w wersjach zawierających od 2 do 50 tysięcy elementów logicznych (LE – logic element), zatem umożliwiają realizację dość zaawansowanych projektów.

Budowa

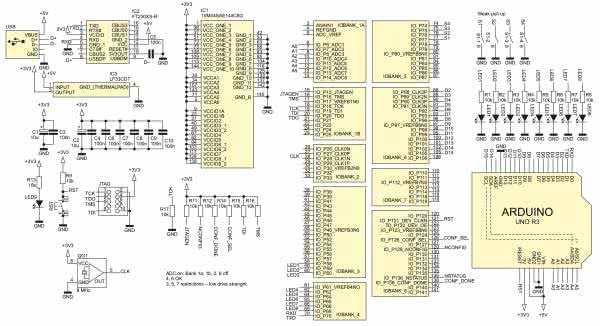

Schemat układu pokazano na rysunku 1. Zasilanie jest dostarczone przez port USB. Napięcie jest obniżane do 3,3 V za pomocą stabilizatora LF33 (IC3). Dioda LED9 sygnalizuje podłączenie zasilania, a kondensatory C1...C10 odpowiadają za jego filtrację.

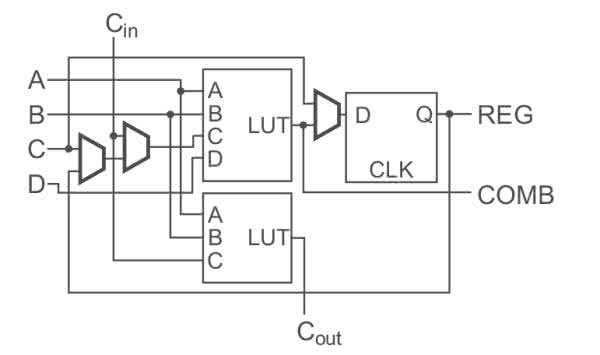

Najważniejszą częścią projektu jest 10M04SAE144C8G – tak oznaczony jest układ FPGA z rodziny Intel MAX10 (IC1). Zastosowana wersja wyposażona jest w cztery tysiące elementów logicznych. Schemat pojedynczego LE pokazano na rysunku 2. Składa się z dwóch tablic LUT oraz jednego przerzutnika D. Wartość z pierwszej, czterobitowej tablicy może być wyprowadzona na zewnątrz albo zatrzaśnięta w przerzutniku. Natomiast druga, trzybitowa pozwala na wyznaczenie przeniesienia, które za pomocą szybkiej ścieżki jest połączone z sąsiednim LE.

Wewnątrz układu zawarta jest pamięć RAM o rozmiarze 189 Kb pamięci (w 21 blokach po 9 Kb) oraz 1248 Kb pamięci Flash dzielonej pomiędzy bitstream oraz aplikacją użytkownika. Dostępnych jest także 20 bloków mnożących 18-bitowe liczby oraz jeden przetwornik analogowo-cyfrowy.

Programowanie jest możliwe poprzez interfejs JTAG wyprowadzony na złączu goldpin. Do programowania można użyć programatora USB Blaster. Rezystory R10...R12 i R14...R17 ustalają odpowiednie stany na wejściach konfiguracyjnych. Więcej na ten temat można się dowiedzieć z dokumentacji [1], natomiast pełną bazę wiedzy znajdziemy na stronie [2].

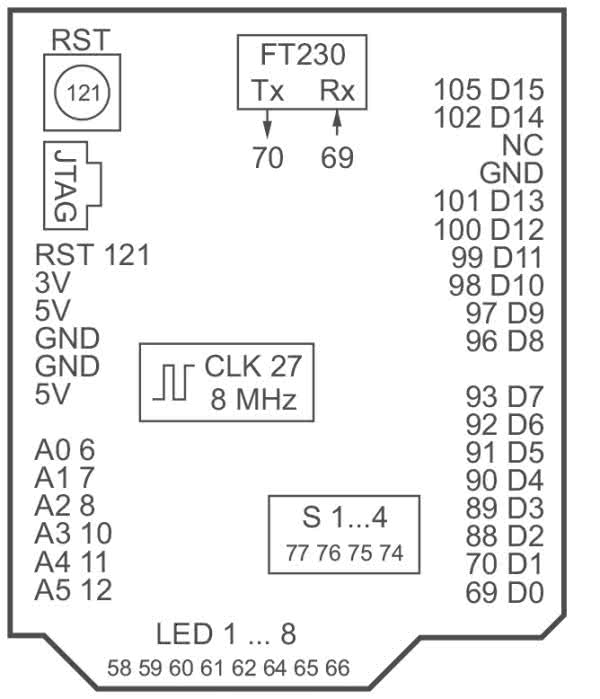

Poza układem FPGA na płytce znajduje się kilka podstawowych peryferiów ułatwiających rozpoczęcie własnych eksperymentów. Generator kwarcowy QG1 dostarcza stabilny sygnał zegarowy o częstotliwości 8 MHz, który może być użyty do taktowania układu, bądź jako referencja dla wewnętrznej pętli PLL. Diody LED1...LED8 oraz przełącznik dip switch S1 są podłączone bezpośrednio do FPGA. Piny obsługujące włączniki muszą mieć włączony wewnętrzny rezystor podciągający do plusa zasilania. Część pinów została także wyprowadzona na złącze zgodne z Arduino. Należy jednak pamiętać, że maksymalne napięcie, jakie można na nie doprowadzić, to 3,3 V.

Złącza A0...A5 mogą służyć jako wejścia dla przetwornika ADC. Jego włączenie powoduje ograniczenia przy korzystaniu z niektórych portów wejścia/wyjścia. Bloki 1a, 1b, 2 i 8 są wtedy niedostępne, natomiast liczba pinów z bloków 3, 5 i 7 jest ograniczona. Konfiguracja ADC nie ma wpływu jedynie na bloki 4 i 6.

Przycisk RST jest podłączony do wejścia DEV_CLRn. Domyślnie pracuje ono jako normalny pin, jednak ma także specjalną opcję. Jeżeli włączymy tryb device wide reset, to stan niski na nim spowoduje reset wszystkich przerzutników. Dzięki układowi FT230 (IC2) port USB nie służy tylko do zasilania, ale umożliwia także komunikację poprzez port szeregowy. Linie Tx i Rx są podłączone bezpośrednio do MAX10.

Schemat płytki jest także dostępny na licencji BSD i można go pobrać z repozytorium [3].

Montaż i uruchomienie

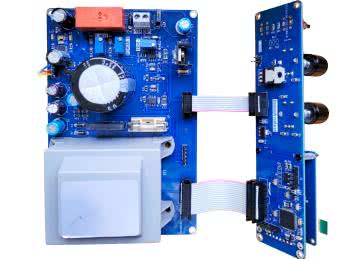

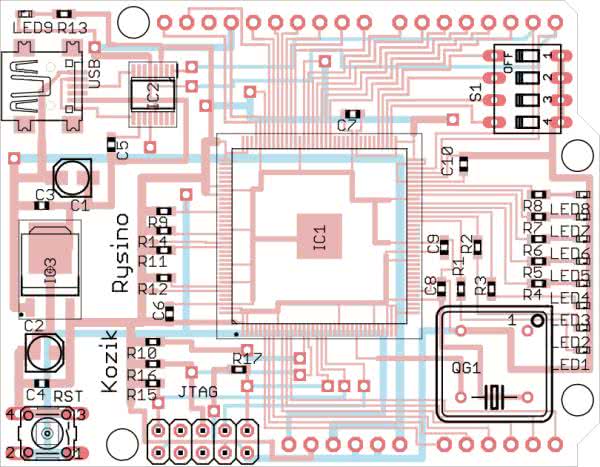

Projekt dwustronnej płytki drukowanej pokazano na rysunku 3, a zdjęcie gotowego układu prezentuje fotografia tytułowa. Montaż warto rozpocząć od fragmentu odpowiedzialnego za zasilanie. Najpierw lutujemy złącze USB, stabilizator, kondensatory C1...C4 oraz diodę LED9 i opornik R13. Po sprawdzeniu, czy nie występują zwarcia, podłączamy kabel USB. Powinna zaświecić się dioda. Woltomierzem sprawdzamy, czy napięcie na wyjściu stabilizatora jest równe 3,3 V.

Warto także sprawdzić, czy światło diod LED nie jest zbyt intensywne – w początkowej wersji układu do ograniczenia prądu zastosowałem rezystory 330 Ω, jednak emitowane światło było zbyt jasne. Dopiero po zmianie rezystorów na 10 kΩ uzyskałem odpowiedni efekt.

Następnie przechodzimy do układu IC2. Po sprawdzeniu poprawności jego montażu podłączamy układ do komputera PC. System operacyjny powinien wykryć konwerter FT230. Teraz możemy przystąpić do lutowania układu FPGA i pozostałych komponentów. Po końcowym sprawdzeniu połączeń za pomocą testera zwarć podłączamy zasilanie.

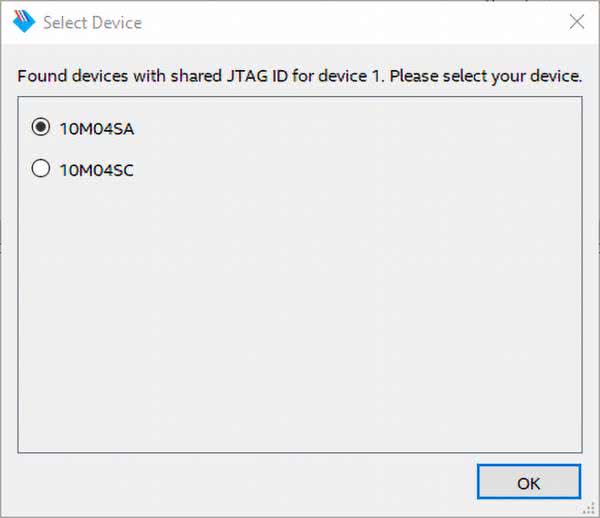

Teraz potrzebny będzie programator USB Blaster, należy dołączyć go do płytki. Można go nabyć na popularnych serwisach aukcyjnych: zarówno polskich, jak i zagranicznych. Po wybraniu opcji Auto Detect w programie Quartus Prime Programmer układ powinien zostać wykryty. W oknie dialogowym (rysunek 4) wybieramy opcję 10M04SA. Do przetestowania płytki można wykorzystać przykładowy projekt znajdujący się także w repozytorium [3]. Wygenerowany wsad znajduje się w pliku board_test/board_test.sof. W demonstracyjnym bitstreamie cztery diody są sterowane za pomocą przełączników. Pozostałe zostały podłączone do wyjść licznika binarnego. Linie Tx i Rx portu szeregowego zostały "zwarte" wewnątrz układu FPGA, powodując powstanie "echa". Oznacza to, że jeśli otworzymy port com za pomocą programu PuTTY, w konsoli powinien pojawiać się dokładnie taki sam tekst, jaki wpisujemy na klawiaturze.

Układ jest gotowy do pracy. Aby stabilniej stał na stole, do spodniej strony PCB można dokleić gumowe nóżki.

Podczas uruchamiania własnych projektów pomocna może okazać się rozpiska numerów pinów podłączonych do różnych peryferiów pokazana na rysunku 5.

Rafał Kozik

rafkozik@gmail.com

Bibliografia

[1] Intel® MAX® 10 FPGA Device Family Pin ConnectionGuidelines, https://intel.ly/2NemCeS

[2] https://intel.ly/2JoQqEw

[3] http://bit.ly/33Xec2e

Rezystory:

R1…R17: 10 kΩ SMD0603

Kondensatory:

C1, C2: 10 μF SMD0405

C3…C10: 100 nF SMD0603

Półprzewodniki:

LED1…LED9: zielona SMD0603

IC1: 10M04SAE144C8G

IC2: FT230XS

IC3: LF33CDT

QG1: generator kwarcowy 8 MHz DIL08s

Pozostałe:

USB: złącze mikroUSB SMD

RST: μSwitch

S1: dipSwitch poczwórny

JTAG: wtyk kątowy goldpin 2×5

ARDUINO: gniazda goldpin 6, 6, 8, 10

Zaloguj

Zaloguj