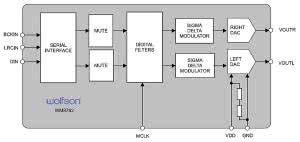

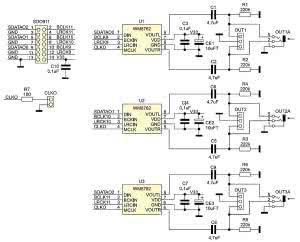

Karta oparta jest o niedrogi i łatwy w aplikacji przetwornik C/A typu WM8762 firmy Wolfson gwarantujący osiągniecie dobrych parametrów przetwarzania niewielkim nakładem środków. Schemat blokowy układu WM8762 pokazano na rysunku 1. Układ zapewnia przetwarzanie sygnału z rozdzielczością 24 bitów przy częstotliwości próbkowania 192 kHz i większym od 90 dB odstępie sygnału od zakłóceń. Schemat modułu wyjść analogowych z układem WM8762 zaprezentowano na rysunku 2.

Moduł składa się z trzech identycznych kanałów stereofonicznych. Sygnał wyjściowy z przetwornicka C/A jest doprowadzony do gniazd OUTxA lub do złącz OUTx. Ma on amplitudę 1,2 Vrms przy obciążeniu rezystancją 10 kV. Dla uproszczenia moduł pozbawiono wyjściowych filtrów dolnoprzepustowych. Sygnał jest filtrowany za pomocą filtrów cyfrowych wbudowanych w przetwornik C/A. Kondensatory C1, C2, C5, C6, C8, C9 separują składową stałą z przetwornika C/A.

Układ scalony WM8762 pracuje w trybie LJ (wyrównanie do lewej) z rozdzielczością 24 bitów. Sygnał cyfrowy z DSP jest doprowadzony poprzez złącza SDO911 do każdego z wejść przetworników U1...U3. Przebieg zegarowy niezbędny do pracy przetworników jest pobierany z płytki Mega DSP poprzez złącze CLKO. W module można zastosować bez dokonywania żadnych zmian układowych przetwornik WM8727 różniący się tylko interfejsem cyfrowym w formacie I²S - wymaga to jedynie zmiany konfiguracji DSP.

Wykaz elementówRezystory: Kondensatory: Półprzewodniki: Inne: |

Montaż, test funkcjonalny

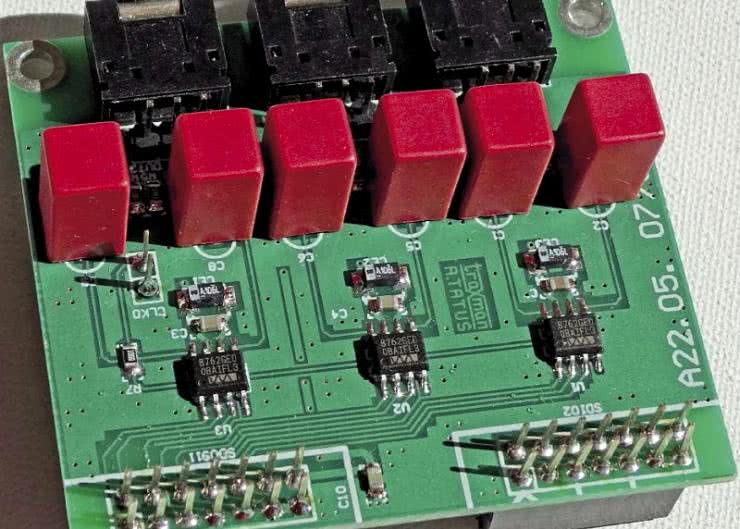

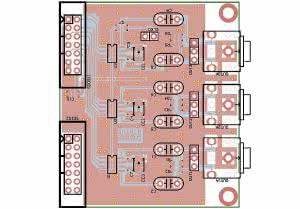

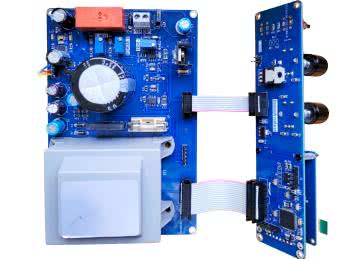

Układ zmontowano na niewielkiej płytce drukowanej, której schemat montażowy pokazano na rysunku 3. Liczba wlutowanych układów scalonych jest zależna od potrzeb - na wyjściu jednego przetwornika D/A są dostępne dwa kanały. W module prototypowym zastosowano 3 układy WM8762, więc uzyskano w ten sposób 6 kanałów.

Sposób montażu jest typowy i nie wymaga opisywania, należy tylko sprawdzić jego poprawność. W zależności od preferencji, układ może być połączony z płytką bazową za pomocą taśm IDC14 dla zasilania i sygnałów I²C oraz przewodu ekranowanego dla sygnału zegarowego (możliwie krótkiego). Ja preferuję układanie modułów w "kanapki", jednak wiąże się to z koniecznością zdobycia trudnodostępnych złącz przelotowych IDC 20 mm, takich jak są stosowane w modułach rozszerzających Raspberry PI, odpowiedniego ich przycięcia oraz zamiany złącz GPIO i USBI na kątowe w module bazowym ADAU1442. Wybór rozwiązania pozostawiam użytkownikowi. Stabilność mechaniczną przy łączeniu "kanapek" zapewniają kołki dystansowe montowane od strony złącz jack.

Po poprawnym montażu należy sprawdzić położenie zwór M0/1/2 (GND/VCC/GND) w module ADAU144x, sprawdzić obecność napięcia zasilającego 3,3 V i sygnału zegarowego na złączu CLKO. Jeżeli wszystko jest w porządku, można przejść do uruchomienia oprogramowania Sigma Studio w celu przygotowania i sprawdzenia aplikacji testowej.

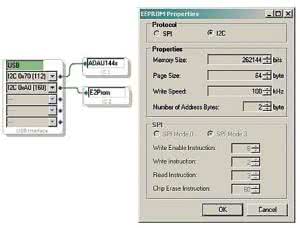

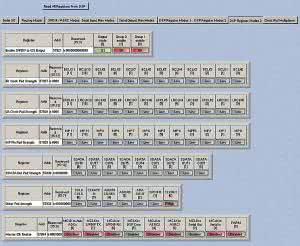

Do zaprogramowania ADAU144x jest konieczny interfejs USBi. Po uruchomieniu środowiska Sigma Studio w obszar roboczy okienka konfiguracji musimy przeciągnąć, połączyć i skonfigurować elementy USBi, ADAU144x oraz E2PROM zgodnie z rysunkiem 4. W zależności od zastosowanej pamięci EEPROM (w modelu 24FC/LC256) jest konieczne określenie wewnętrznej konfiguracji za pomocą zakładki IC2-E2Prom/Properties. Należy podać pojemność pamięci, wielkość bloku danych oraz częstotliwości magistrali I²C (dostępne od Sigma Studio ver. 3.9). W przeciwnym wypadku programowanie EEPROM może być niemożliwe lub nieprawidłowe.

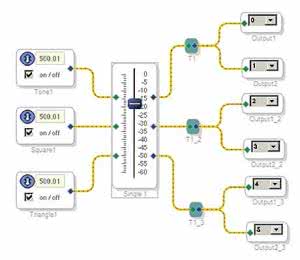

W roli aplikacji testowej wykorzystamy 3-kanałowy generator sygnału o regulowanym poziomie. Schemat blokowy aplikacji pokazano na rysunku 5. W projekcie jest konieczne ustawienie częstotliwości próbkowania na 96 kHz (kwarc 12,288 MHz). Sygnały cyfrowe z generatorów po regulacji poziomu dostępne są w kanałach 0...5 bloku wyjściowego i doprowadzone do wyjściowych kanałów DSP.

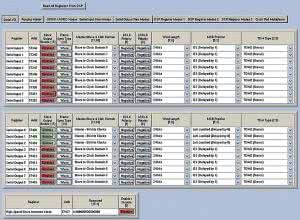

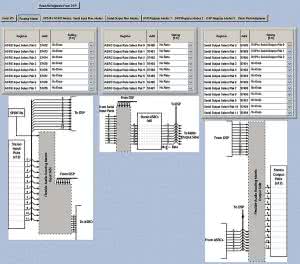

Aplikacja nie używa GPIO. Po narysowaniu projektu jest konieczna konfiguracja sprzętowa ADAU144x. W pierwszej kolejności jest wymagane skonfigurowanie wyjściowego interfejsu cyfrowego w trybie LJ (Left Justified), 24 bity, Master 96 kHz (rysunek 6) oraz matrycy przepływu sygnałów, jak na rysunku 7. Następnie jest konieczne skonfigurowanie układu zegarowego DSP, co pokazano na rysunku 8.

Po zapisaniu i skompilowaniu projekt jest gotowy do sprawdzenia w rzeczywistej aplikacji. Za pomocą USBi, warto też załadować oprogramowanie do EEPROM, aby nie tracić go po wyłączeniu zasilania. Po dołączeniu wzmacniacza do przetwornika C/A jest możliwe przetestowanie działania aplikacji. Układ nie wykorzystuje GPIO, wszystkie regulacje odbywają się za pomocą wirtualnych manipulatorów na ekranie monitora PC.

Adam Tatuś, EP

Zaloguj

Zaloguj