Dotychczas przez 60 lat od powstania pierwszych układów scalonych skala integracji, tj. liczba tranzystorów w pojedynczym czipie, podwajała się co 2 lata. Już w połowie lat sześćdziesiątych zauważył tę prawidłowość Gordon Moore, przyszły szef Intela. Prawo Moore’a sprawdza się do dziś. Jak długo jeszcze? Oto jest pytanie. Liczba tranzystorów w mikroprocesorach lub pamięciach sięga już dziesiątków miliardów. I co dalej?

Wiadomo, że zwiększanie liczby tranzystorów w układzie scalonym odbywa się dzięki miniaturyzacji tranzystorów. Zatem spytajmy, czy miniaturyzacja tranzystorów w układach scalonych zbliża się do swego kresu? Od lat zadawano sobie pytania o fizyczne i technologiczne ograniczenia miniaturyzacji tranzystorów. Wiele prognoz się nie sprawdziło. Kolejne bariery zostały sforsowane. Jednak tym razem to już koniec. Długość kanału tranzystora MOS, szerokości ścieżek i grubości warstw wynoszą już kilka nanometrów, a więc mieści się w nich kilkanaście atomów.

Kolejna redukcja wymiarów o rząd wielkości oznaczałaby, że w długości kanału, szerokości ścieżki lub grubości warstwy mieści się 1 atom, a to nie jest możliwe. Wymiar charakterystyczny w pierwszych układach scalonych MOSLSI wynosił 10 mm, by osiągnąć 7 nm w roku 2019. Mówi się, że za rok–dwa możliwa jest jeszcze jedna redukcja rozmiarów do 3 nm, co w Si lu b SiO2 odpowiada dziesięciu atomom. I na tym zapewne koniec. Czy to oznacza koniec historii rozwoju mikroelektroniki?

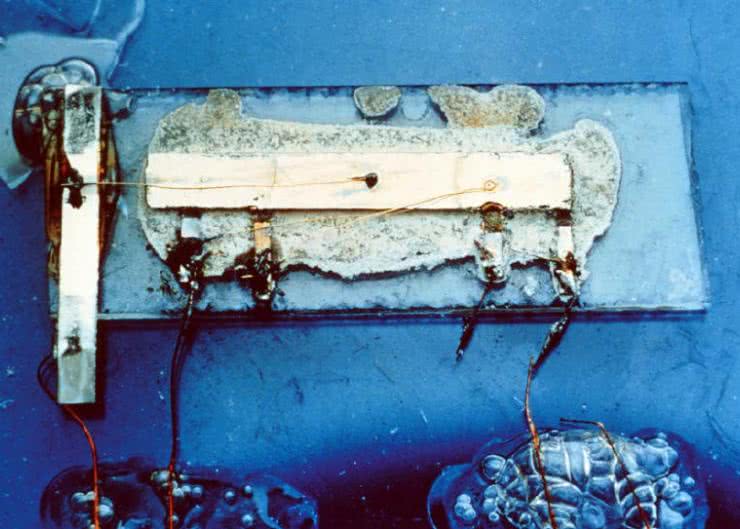

Nie sprawdziły się zapowiedzi końca historii rozwoju społeczno-politycznego (Hegel, Fukuyama) i pewnie błędne byłoby oczekiwanie, że za 2 lata mikroelektronika przestanie się rozwijać. Żeby jednak szukać odpowiedzi na pytanie o przyszłość, trzeba dobrze rozumieć przeszłość. Poświęćmy jej trochę miejsca. Zacznijmy od pytania, dlaczego miniaturyzacja jest utożsamiana z postępem. Po co jest miniaturyzacja? Początek tej historii sięga lat pięćdziesiątych, gdy zaczęły powstawać komputery montowane najpierw z lamp, a potem z tranzystorów. Wtedy pojawiło się pojęcie tyrania liczb. Montaż tysięcy tranzystorów był niezwykle pracochłonny i wystarczyło, by jeden z tranzystorów okazał się wadliwy, aby cała praca poszła na marne. Stąd zrodziła się idea, by wytwarzać układ złożony z wielu elementów w jednym procesie technologicznym. W roku 1958 Jack Kilby z Texas Instruments pokazał, że jest to możliwe, demonstrując pierwszy układ scalony wykonany w germanie (był to oscylator składający się z jednego tranzystora ze sprzężeniem zwrotnym RC). Technologia Jacka Kilby'ego nie odegrała żadnej istotnej roli, bo łączył on złotym drutem poszczególne elementy ulokowane na oddzielnych wyspach, co niewiele różniło się od montażu elementów dyskretnych. Pół roku po Kilbym Robert Noyce w firmie Fairchild zademonstrował układ scalony w technologii planarnej z połączeniami elementów ścieżkami naparowanego aluminium. Był to początek ery technologii planarnej stosowanej do dziś z różnymi modyfikacjami. Był to też początek drogi w redukowaniu kosztów. Tak jest – podstawowym czynnikiem napędowym miniaturyzacji jest dążenie do redukcji kosztów. Pierwszy rynkowy układ scalony wypuszczony przez Texas Instruments w 1960 roku (opracowany przez Jacka Kilby'ego multiwibrator na dwóch tranzystorach, dwóch diodach i ośmiu elementach biernych) kosztował 450 dolarów. Dzisiaj za 1 dolara można kupić układ scalony zawierający ponad miliard tranzystorów. Drugim czynnikiem napędowym miniaturyzacji jest dążenie do zwiększania szybkości działania układów. Im krótszy jest kanał tranzystora, tym mniejszy jest czas przelotu nośników od źródła do drenu, a więc większa częstotliwość działania układu. Zatem kierunek i cel rozwoju mikroelektroniki jest oczywisty – coraz mniejsze rozmiary tranzystorów to coraz niższy koszt produkcji liczony na pojedynczy tranzystor i coraz większa szybkość działania układów scalających coraz większe liczby tranzystorów.

A co nam przeszkadza w realizacji tego celu? Przeszkód jest wiele, a ich działanie ograniczające rozwój ujawniało się z różną siłą na poszczególnych etapach rozwoju. Zmniejszanie rozmiarów od 10 mm do ok. 100 nm, czyli w latach 1970…2000, postępowało dość gładko w wyniku ulepszania procesów technologicznych, głównie litografii, przy niewielkich zmianach konstrukcji tranzystora poddawanego procedurze przeskalowania (scaling down). W kolejnych latach , przy zmniejszaniu rozmiarów od 100 nm do 10 nm, trzeba było pokonać kilka ograniczeń fizycznych.

Po pierwsze, wzrost szybkości działania układów scalonych zaczęły ograniczać obwody RC tworzone przez pojemności pasożytnicze i rezystancje kontaktów, a więc dalsze zmniejszanie długości kanału nie dawało oczekiwanego przyrostu szybkości działania.

Po drugie, w miarę zwiększania gęstości upakowania tranzystorów i liczby tranzystorów w układzie, rośnie ilość wydzielanego ciepła. Ma to też związek z pojemnościami pasożytniczymi, które zwiększają pobór prądu w stanie dynamicznym, przy przełączaniu inwertera CMOS. Aby zmniejszyć ilość wydzielanego ciepła, trzeba było sukcesywnie zmniejszać napięcie zasilania inwerterów CMOS. Było to też niezbędne dla uniknięcia przebicia skrośnego dren–źródło oraz prądu tunelowego źródło-dren dla zatkanego tranzystora. Dla długości kanału 10 nm stosuje się napięcie UDD=0,8 V, a dla kanału 5 nm UDD=0,65 V. Tak niskie napięcie UDD wymaga niezwykłej powtarzalności i stabilności napięcia progowego UT. Dla pokonania tych trudności trzeba było wprowadzić istotne modyfikacje w technologii planarnej.

Trzeba było wreszcie sięgnąć po trzeci wymiar. Tak powstała technologia FinFET, w której kanał tranzystora MOS ma kształt pionowej ściany pokrytej bramką, która oddziaływuje polem z dwóch boków i z góry. Kanał przypomina swoim kształtem płetwę rekina wystającą nad powierzchnię wody, stąd nazwa FinFET. Z tak zmodyfikowaną technologią planarną udało się „dojechać” do rozmiaru 7 nm i prawdopodobnie uda się jeszcze osiągnąć 3 nm, ale na tym będzie koniec rozwoju mikroelektroniki krzemowej. Czy na pewno? Otóż niezupełnie.

Pojawia się możliwość wytwarzania układów wielowarstwowych. Są już pamięci flash 3DNAND składające się z 96 warstw. Na rok 2021 planowane jest osiągnięcie 256 warstw. Samsung pracuje nad układami 4 Tbit (terabit, czyli 1012) z 410 warstwami. Przewiduje się, że ta koncepcja pozwoli wytwarzać układy z 1024 warstwami. Jednak wygląda na to, że to łabędzi śpiew technologii krzemowej. I co dalej? Od dość dawna pewne nadzieje wiąże się z wprowadzeniem do gry nowych (starych) materiałów, tj. Ge i GaAs.

Na horyzoncie widać też nowe idee fizyczne. Eksperymenty z zastąpieniem w układach scalonych połączeń miedzianych fotonową transmisją sygnałów mogą doprowadzić do podwyższenia szybkości działania układów. Od wielu lat wielkie nadzieje łączy się z grafenem i jeszcze większe z tzw. komputerem kwantowym (quantum computing), czyli z nową elektroniką, nazywaną również spintroniką. Historia uczy, że od nowych idei do praktycznych zastosowań na dużą skalę, o ile wszystko idzie dobrze, trzeba ok. 30 lat. Te nowe idee świetnie się zapowiadają już od ok. 10 lat, a więc pozostało jeszcze ok. 20 lat. Przez najbliższe 20 lat będziemy więc mieli ciągle elektronikę krzemową opartą na transporcie ładunków. Czy będzie to okres stagnacji, gdy prawo Moore’a nie będzie już działać?

Aż nie chce się wierzyć.

Zaloguj

Zaloguj