W 1965 roku Gordon Moore opublikował swój słynny artykuł w ósmym numerze Electronics Magazine. Stwierdził w nim, że liczba tranzystorów w jednym układzie scalonym podwaja się każdego roku, i przewiduje, że tak będzie nadal, przynajmniej do roku 1975. Później ulepszenia i dodatkowe obserwacje rynku elektronicznego spowodowały, że zrewidował odrobinę swój model, ale podstawowa zasada trwałego wykładniczego tempa wzrostu liczby tranzystorów stała się aksjomatem przemysłu elektronicznego. Wzrost ten nie ominął również układów programowalnych (FPGA).

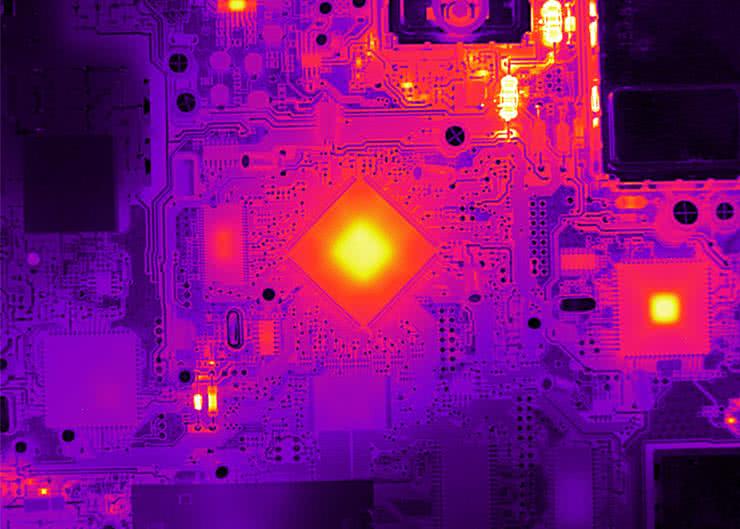

Tak zwane Prawo Moore’a stało się samospełniającą przepowiednią, dyktującą tempo i kierunek rozwoju branży elektronicznej. W wyniku tego, proces decyzyjny projektantów elektroniki zawsze preferował technologie, które wyciskają z urządzeń więcej wydajności obliczeniowej w mniejszym obszarze, kosztem mocy, użyteczności, a nawet trwałości układu. W wyścigu technologicznym rozmiar jest wszystkim. Konsekwencją tego są zaawansowane układy, które pobierają ogromne ilości mocy i potrzebują często wielu różnych, precyzyjnie stabilizowanych domen zasilania. Dokładnie takie są omawiane w tym cyklu artykułów układy FPGA.

W dwóch poprzednich częściach tego artykułu udzieliliśmy odpowiedzi na pytania „ile?” oraz „jak?”, dotyczące systemów zasilania układów programowalnych. W ostatniej, trzeciej części tego cyklu artykułów, postaramy się odpowiedzieć – przynajmniej częściowo – na pytanie „dlaczego?”. Część odpowiedzi mamy już powyżej – ekstremalnie wysoka gęstość upakowania tranzystorów, jaka jest typowa dla układów FPGA, jest jednym z głównych powodów problematycznego zasilania układów FPGA i innych nowoczesnych układów scalonych. Przyjrzyjmy się jednak temu zagadnieniu z większą dokładnością, by zrozumieć, jak fizyczna architektura FPGA wpływa na jego wymagania co do jakości i parametrów linii zasilania.

Inżynieria tranzystorów

Ponieważ tranzystory zmniejszyły się do rozmiarów nanometrycznych, dominujące zaczynają być zjawiska, które do niedawna pełniły rolę uboczną. Najbardziej oczywistym efektem tego jest poziom napięcia zasilania. Podczas gdy 5 V byłoby dobrym źródłem zasilania tranzystorów kilka dekad temu, to takie napięcie zepsułoby wszystkie połączenia i dielektryczne warstwy tlenków we współczesnym tranzystorze FET w układzie scalonym. Ponieważ geometrie tranzystora kurczą się, wewnętrzne pole elektryczne staje się znacznie silniejsze, a dopuszczalne napięcie robocze spada. Najnowsze generacje tranzystorów tolerują napięcie zasilania na poziomie jedynie około 1,0 V lub mniej. Ponadto, bezwzględna tolerancja napięcia zmniejsza się proporcjonalnie: 2% z 1,0 V to znacznie mniejszy zakres niż 2% z 5 V, co sprawia, że dokładność stabilizacji napięcia zasilania staje się coraz bardziej istotna.

Wraz ze zmniejszającymi się napięciami pojawia się rosnący prąd drenu tranzystora podczas pracy. Zwiększona siła sterowania spełnia co najmniej dwie role. Po pierwsze, pozwala tranzystorowi o mniejszym napięciu bramki sterować znacznym prądem – dzięki czemu jest on wystarczająco silny, aby przełączać się na użytecznej częstotliwości. Po drugie, pozwala na stworzenie fizycznie mniejszego tranzystora. Mniejszy tranzystor może być szybszy. Niestety, zwiększony prąd sterowania tranzystora ma swoje wady: większy prąd upływu.

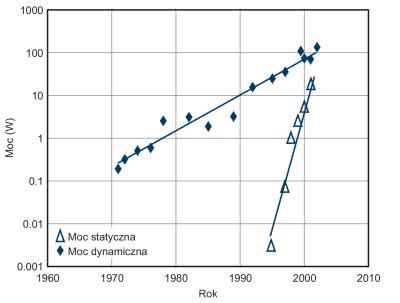

Istnieją dwa rodzaje rozpraszania mocy przez tranzystory w układzie scalonym. Moc dynamiczna to moc tracona podczas przełączania między napięciem stanu wysokiego i stanu niskiego w sygnale przy pewnej częstotliwości. Dynamiczna strata mocy jest powodowana przez ładowanie i rozładowywanie pasożytniczych pojemności związanych z samymi tranzystorami i liniami na urządzeniach łączących układ. Moc dynamiczna jest liniowo proporcjonalna do częstotliwości przełączania logicznych i kwadratowo do napięcia zasilającego układ.

Mniej oczywista jest moc wyciekająca przez tranzystory. Moc ta wycieka z układu przez cały czas, gdy obwód jest zasilany, niezależnie od tego, czy jest on aktywny, czy bezczynny, taktowany, czy nie. Zwiększony prąd sterowania tranzystora powoduje większy prąd upływu, ponieważ połączenia i struktury wykonane w celu przewodzenia większego prądu są trudniejsze do pełnego, prawdziwego wyłączenia (tj. redukcji prądu upływu do zera). Z każdą generacją tranzystorów narastały efekty prądu upływu. Tylko połączenie zaawansowanej inżynierii półprzewodnikowej (stosowanie odpowiedniej obróbki chemicznej, metalurgicznej, litograficznej i fizycznej) oraz dokładnego, elastycznego zarządzania zasilaniem w układzie utrzymuje w ryzach moc upływu.

Dziesięć lat temu Gordon Moore (ten sam, który zaobserwował wcześniej regularny postęp w zwiększaniu się gęstości tranzystorów) zaobserwował dwa ważne fakty, wymienione poniżej.

Po pierwsze, jeśli moc dynamiczna nadal będzie rosła w tym samym tempie to temperatura złącza na działającym układzie scalonym będzie po jakimś czasie zbliżona do temperatury powierzchni Słońca. Po drugie, jeśli nie zostanie z tym nic zrobione, to moc tracona w postaci prądu upływu, w pewnym momencie wyprzedzi dynamiczną stratę mocy jako podstawowy tryb rozpraszania energii w układzie, dodatkowo zaostrzając problem rozpraszania mocy (rysunek 2). Aby rozwiązać ten problem, przemysł półprzewodnikowy zastosował w tym czasie kilka nowych technik. Jedną z nich jest zarządzanie zegarem – spowalnianie lub zatrzymywanie zegarów taktujących układ w celu ograniczenia mocy dynamicznej – a drugą jest użycie wielu rdzeni przetwarzających na jednym chipie w celu zwiększenia liczby tranzystorów na których moc jest rozpraszana.

Nawet przy zaawansowanych architekturach układów FPGA, problem poboru i rozpraszania mocy pozostaje kłopotliwy. Inżynieria tranzystorów to potężny sposób na wygięcie krzywej pokazanej na rysunku 2 w dół, ale to nie wystarczy. Każda mniejsza generacja tranzystorów wymaga obniżonego napięcia zasilania, problem mocy dynamicznej pozostaje mniej istotny. Jednakże, wynikające z tego zwiększenie prądu pobieranego przez tranzystory, w połączeniu z ciągle rosnącą liczbą urządzeń półprzewodnikowych w układzie, jest problematyczne. Zwiększa to zapotrzebowanie na dokładniejsze zarządzanie sekcją zasilania współpracującą z tymi układami. Napięcie zasilania musi być ściśle kontrolowane, a także aktywnie stabilizowane, aby zaspokoić potrzeby każdego konkretnego urządzenia.

Zaawansowane architektury

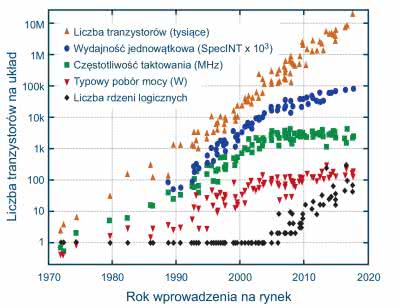

Rozwój architektury układów elektronicznych do przełomu tysiącleci koncentrował się głównie na optymalizacji pojedynczego rdzenia obliczeniowego, aby wykonać jak najwięcej obliczeń tak szybko, jak to tylko możliwe. Wiązało się to z podwyższaniem częstotliwości taktowania układu do fizycznych granic. Wymagało to również optymalizacji architektonicznych samego układu, ale miały one głównie na celu wyciśnięcie wyższej wydajności z każdego cyklu zegara.

Po zaskakującym uświadomieniu sobie, że pobierana moc ma znaczenie, inżynierowie zaczęli rozwijać układy w inny sposób – nie skupiać się na czystej prędkości, a bardziej na subtelnych rodzajach optymalizacji jego pracy. Ten nowy trend pojawił się przede wszystkim w architekturze układów obliczeniowych, towarzysząc zahamowaniu wzrostu prędkości zegara i wyrównaniu tempa wzrostu wydajności na tranzystor w każdej generacji (rysunek 3). Był to najbardziej oczywisty sposób na rozwiązanie problemu mocy dynamicznej: przestać pompować ładunek z zasilania do masy z tak dużą szybkością.

Jednak cały czas liczba tranzystorów w jednym chipie rosła – w nieuchronnym tempie przewidzianym przez Moora. Z tymi wszystkimi tranzystorami trzeba było coś zrobić. Wymagało to drugiej wielkiej innowacji: architektury wielordzeniowej. Mniej więcej w tym samym czasie, gdy prędkość taktowania zegara przestała rosnąć, liczba rdzeni na jednym układzie zaczęła się zwiększać.

Zalety stosowania układów wielordzeniowych obejmują m.in. prostsze projektowanie układów dzięki wielokrotnemu użyciu tych samych bloków czy możliwość indywidualnego wyłączania każdego rdzenia, aby sprostać wymaganiom dotyczącym wydajności obliczeniowej i poboru prądu. Rewolucja wielordzeniowa rozpoczęła się od procesorów komputerów stacjonarnych, ale szybko dotarła do świata FPGA, szczególnie wtedy, kiedy świat zdał sobie sprawę, że w pewnym sensie nic nie ma więcej rdzeni niż układ programowalny, złożony z niewielkich, programowalnych bloków logicznych!

Anatomia układów FPGA

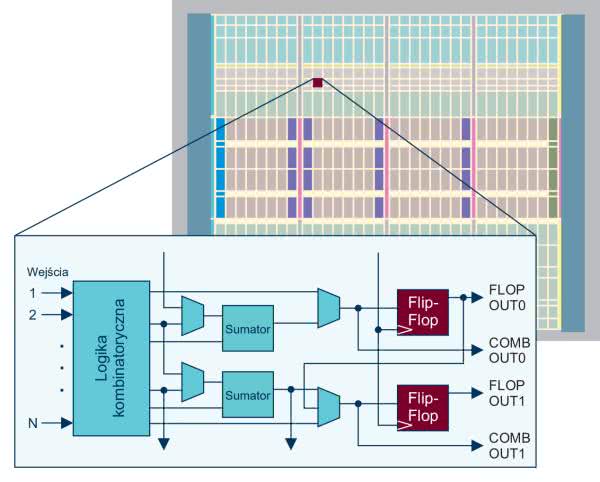

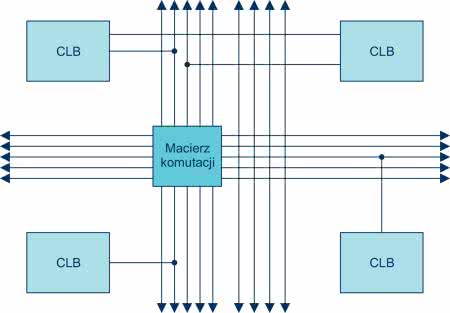

Układ FPGA, na najbardziej podstawowym poziomie, jest zbiorem konfigurowalnych prostych komórek logicznych połączonych ze sobą poprzez konfigurowalną macierz połączeń. Wraz z kompilatorem tworzą one wysoce elastyczną strukturę, która może przekształcić się w prawie każdą możliwą do wyobrażenia funkcję logiczną, w tym kombinatoryczne i sekwencyjne bloki logiczne.

Na wyższym poziomie abstrakcji, tkanka logiczna jest otoczona dodatkowymi funkcjami wspierającymi i rozszerzającymi funkcjonalność układu. Niektóre bloki, takie jak obwody stronicowania, pamięć RAM i pętle PLL, obsługują funkcje wewnętrzne układu. Różne konfigurowalne komórki GPIO, zaimplementowane sprzętowo makra szybkiej komunikacji (LVDS, DDR, HDMI, SMBus itp.) oraz szybkie transceivery w układzie pozwalają logice wewnątrz układu komunikować się ze światem zewnętrznym przy różnych napięciach, prędkościach i protokołach. Inne bloki, takie jak zintegrowane rdzenie procesora czy DSP, obsługują konkretne, zoptymalizowane funkcje.

Struktura rdzenia układu programowalnego składa się z tysięcy lub milionów prostych komórek zwanych konfigurowalnymi blokami logicznymi (CLB). Każdy CLB jest zbiorem kombinatorycznych i sekwencyjnych układów logicznych, które razem mogą realizować proste obliczenia i utrzymywać wartość w jednym lub kilku przerzutnikach.

Logika kombinatoryczna zwykle przyjmuje postać programowalnej tabeli wartości (look-up table – LUT), która może tłumaczyć kilka bitów wejściowych na kilka dowolnych bitów wyjściowych. Każdy LUT wykonuje jedną podstawową funkcję logiczną, zgodnie z programem i przekazuje wynik do konfigurowalnego interkonektu w celu dalszego przetwarzania (rysunek 5).

Sam projekt obwodów w CLB i LUT jest jednym z sekretów, które odróżniają jedne rodziny FPGA od innych. Niedrogie układy FPGA używają prostszych CLB z mniejszą liczbą wejść, wyjść i połączeń oraz mniejszą liczbą przerzutników. Najwyższej klasy układy programowalne używają znacznie bardziej złożonych bloków CLB, z których każdy może mieć wiele wejść i kombinacji logicznych, a także pracuje przy wyższej prędkości. Optymalizacja ta pozwala na przeprowadzenie większej ilości obliczeń na CLB i, w konsekwencji, optymalizację wydajności całego projektu, Oczywiście, dodatkowe wejścia i wyjścia w bardziej złożonych układach FPGA mają inne parametry dynamiczne, pociągające za sobą pewne kompromisy w zakresie m.in. pobieranej mocy w porównaniu do prostszych, mniejszych urządzeń programowalnych.

Poza samą struktura rdzenia, układ FPGA zawiera także wiele innych elastycznych bloków. Wysoce konfigurowalne są również komórki I/O, co jest konieczne, by sprostać różnym wymaganiom peryferii układu co do zakresu napięć pracy, prądu sterowania i rodzaju wyjścia logicznego (push-pull, trójstanowe, otwarty dren itp.). Podobnie jak konfigurowalne LUT-y i macierze połączeń między nimi, programowalne bloki wejścia/wyjścia konfigurowane są w czasie uruchamiania układu FPGA na podstawie ustawień zapisanych w pamięci konfiguracyjnej. Ma to wpływ na kolejność domen w sekwencji załączania napięć zasilających.

W układzie FPGA występują także bloki funkcjonalne, których nie można implementować za pomocą uniwersalnych CLB i GPIO. Są to tak zwane twarde makra, czyli wbudowane funkcje, które korzystają z optymalizacji układu lub których po prostu nie da się zaimplementować jako wystarczająco szybkie w blokach CLB. Należą do nich gigabitowe transceivery, logika arytmetyczna i elementy DSP, specjalistyczne kontrolery, pamięć oraz wbudowane rdzenie procesorów. Wszystkie wymienione bloki to właśnie twarde makra. Bloki będące twardymi makrami mają na ogół własne bloki zasilania, określone dedykowane napięcia i wymagania dotyczące sposobu załączania napięć zasilających i ich stabilizacji.

Wszystkie wymienione powyżej bloki znajdujące się w strukturze układu programowalnego mają inne wymagania co do zasilania – napięcia, prądu, sekwencji zasilania, dokładności stabilizacji etc. System zasilania FPGA musi być w stanie zaspokoić wszystkie te wymagania.

Na ogół największym konsumentem mocy w układzie jest tkanka FPGA (bloki CLB wraz z macierzą połączeń) – wykorzystuje ona najniższe napięcie zasilania w systemie, a przez to pobiera najwyższy prąd. Nowoczesne, rozbudowane układy FPGA mogą wymagać nawet do 100 A prądu dla rdzenia, przy zasilaniu napięciem równym 0,85 V.

Podobne napięcia występują w rdzeniu procesorów, ale przy innych, na ogół mniejszych, prądach i z odmiennymi wymaganiami dotyczącymi kolejności załączania domen zasilania.

Inne funkcje w układzie programowalnym mogą być zasilane napięciem 1,8 V lub 3,3 V i bardzo często muszą zostać zasilone zanim inne domeny zasilania zostaną uruchomione. Z kolei bloki GPIO – na ogół także zasilane napięciem 1,8 V lub 3,3 V – nie mogą zostać zasilone, dopóki rdzeń FPGA nimi sterujący nie zostanie uruchomiony.

Wszystkie tego rodzaju wymagania co do napięć sterujących i kolejności załączania poszczególnych domen zasilania, muszą być egzekwowane przez zasilacz urządzenia.

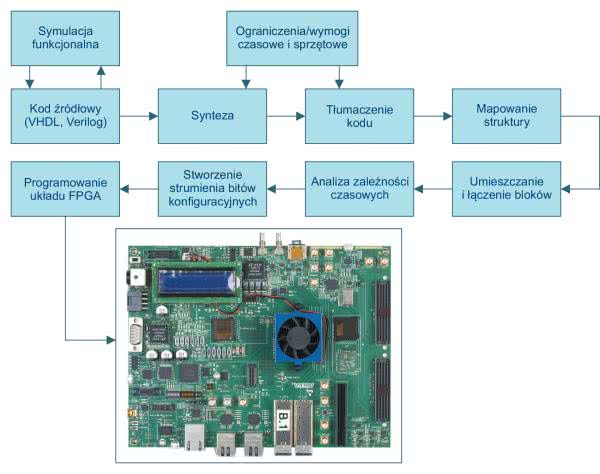

Ostatnim elementem architektury FPGA jest łańcuch narzędzi (rysunek 6). Aby przekształcić pustą tablicę konfigurowalnej struktury logicznej w obwód o wysokiej wydajności, konieczny jest kompleksowy zestaw narzędzi do tłumaczenia kodu napisanego w Verilogu lub VHDL-u na bloki logiczne, przypisania zasobów zegara, resetowania i testowania. Pozwala to zoptymalizować funkcje pod kątem ograniczeń prędkości, mocy lub rozmiaru. Następnie wynik jest ładowany do pamięci EEPROM układu FPGA. Bez tych narzędzi FPGA nigdy nie uzyska swego pełnego potencjału. Narzędzia i języki programowania są niezmiernie ważne. Często przyćmiewają samą fizyczną konstrukcję obwodu, która umożliwia mu działanie.

Inżynierowie spędzają większość czasu na programowaniu FPGA i nie chcą tracić czasu i energii na myślenie o zapewnieniu mu odpowiedniego zasilania. Często pomijane są jednak wymagania dotyczące zasilania sugerowane przez narzędzia programistyczne. Ponieważ tyle wysiłku poświęca się projektowi od strony software, dopiero w późnej fazie rozwoju, gdy pełen projekt jest skompilowany, znane są pełne wymagania dotyczące układu zasilania i można zaobserwować ewentualne problemy z zasilaczami. Kluczowym dla osiągnięcia sukcesu czynnikiem – tak w przypadku oprogramowania jak i sprzętu – jest elastyczność architektury. Odpowiednio zaprojektowane rozwiązanie zasilania zapewnia tego rodzaju elastyczność, niezależnie od wymagań i konfiguracji FPGA.

Historia, ekonomia i czynniki ludzkie nadal napędzają trendy w rozwoju urządzeń półprzewodnikowych. Dominują trendy zwiększające ilość tranzystorów i poziom skomplikowania architektur tworzących układy FPGA. Na każdym poziomie i na każdym etapie projektowania systemów z układami programowalnymi zasilacz odgrywa kluczową, niewidoczną rolę w sukcesie projektu. Najlepszy wybór zasilacza to układ, który jest dokładny, niezawodny, elastyczny, kompaktowy i łatwy w użyciu.

Nikodem Czechowski, EP

Źródło: http://bit.ly/2GrY4vS

Zaloguj

Zaloguj