STM32. Obsługa interfejsu I²S. Dekoder audio

01 września 2010

Zdecydowana większość interfejsów maszyna - człowiek korzysta

z ludzkiego zmysłu wzroku. Niekiedy jednak zadowalające efekty

komunikacji mogą być osiągnięte za pomocą słuchu. Interfejs

dźwiękowy może być podstawowym do komunikacji urządzenia

z operatorem lub być uzupełnieniem graficznego. W artykule

przedstawiono informacje na temat obsługi magistrali I²S w roli

medium łączącego mikrokontroler STM32 z dekoderem audio.

96 ELEKTRONIKA PRAKTYCZNA 9/2010

NOTATNIK KONSTRUKTORA

Dodatkowe informacje:

Dodatkowe informacje na temat

mikrokontrolerów STM32 oraz środowiska

Atollic TrueSTUDIO można znaleźć

w poprzednich numerach EP, m. in:

? ?Atollic TrueSTUDIO. Sposób na

mikrokontrolery STM32?, EP 02/2010,

? ?Obsługa portów we/wy, przerwań i timerów

w mikrokontrolerach STM32. Wykorzystanie

funkcji API?, EP 12/2008

Interfejs I2

S

Coraz większa liczba urządzeń, szcze-

gólnie należących do segmentu elektroniki

konsumenckiej, jest wyposażona w interfejs

dźwiękowy. Tor audio składa się zazwyczaj

z pamięci, w której zapisane są sekwencje

dźwiękowe, mikrokontrolera sterującego

oraz dekodera audio. Komunikacja z pamię-

cią zależy od jej typu, natomiast wiele de-

koderów audio może korzystać z interfejsu

I2

S (ang. Inter-IC Sound) zaprojektowanego

przez firmę Philips do przesyłania dźwięku

w formie cyfrowej pomiędzy układami sca-

lonymi. Standaryzacja przesyłania sygnału

audio w postaci cyfrowej miała na celu upo-

rządkowanie i zunifikowanie interfejsów sto-

sowanych przez różnych producentów ukła-

dów scalonych.

Zadaniem interfejsu I2

S jest więc przesy-

łanie tylko danych audio. Pozostałe sygnały,

jeśli takie są wymagane, muszą być przesyła-

ne w inny sposób. W minimalnej konfigura-

cji, do przesyłu informacji za pomocą magi-

strali I2

S wymagane są tylko trzy linie:

? zegarowa SCK,

? aktywnego kanału audio LRCK,

? danych SDATA.

Norma interfejsu przewiduje przesyłanie

jedynie sygnału stereofonicznego. Jeśli deko-

der audio nie ma własnego generatora sygna-

łu zegarowego, to istnieje możliwość dostar-

czenia go do dekodera za pomocą czwartej

linii sygnałowej MCLK. Częstotliwość sygna-

łu MCLK powinna być 256 razy większa od

częstotliwości linii zegarowej SCK. Przebiegi

czasowe przykładowego fragmentu komuni-

kacji pokazano na rysunku 1.

Urządzenia dołączone do magistrali I2

S

mogą pracować w kilku trybach w zależno-

ści od tego, które jest urządzeniem nadrzęd-

nym, a które podrzędnym. W bardziej rozbu-

dowanych aplikacjach może być konieczne

dołączenie do interfejsu kontrolera magistra-

li. Jego zadaniem będzie takie zarządzanie

STM32

Obsługa interfejsu I2

S

Dekoder audio

Zdecydowana większość interfejsów maszyna ? człowiek korzysta

z ludzkiego zmysłu wzroku. Niekiedy jednak zadowalające efekty

komunikacji mogą być osiągnięte za pomocą słuchu. Interfejs

dźwiękowy może być podstawowym do komunikacji urządzenia

z operatorem lub być uzupełnieniem graficznego. W artykule

przedstawiono informacje na temat obsługi magistrali I2

S w roli

medium łączącego mikrokontroler STM32 z dekoderem audio.

Rysunek 1. Komunikacja za pomocą interfejsu I2

S

Rysunek 2. Tryby pracy urządzeń dołączonych do

interfejsu I2

S

stanami linii sygnałowych, aby nie wystąpiły

konflikty, np. przełączenie się dwóch urzą-

dzeń w tryb master. Możliwe tryby pracy

przedstawiono na rysunku 2. Sygnały SCK

i LRCK są zawsze generowane po stronie

układu nadrzędnego. Należy

zaznaczyć, że długości ramek

danych nie są z góry zdefi-

niowane w normie. Nadajnik

nie musi wiedzieć ilu bitów

spodziewa się odbiornik, ana-

logicznie odbiornik nie musi

mieć informacji, ile bitów za-

wierają ramki wysyłane przez

nadajnik. Aby osiągnąć pra-

widłową komunikację przy ta-

kich założeniach, jako pierw-

szy transmitowany jest zawsze

bit najbardziej znaczący MSB.

Podziału strumienia danych

na linii SDATA na kanał lewy

i prawy dokonuje linia aktyw-

nego kanału LRCK. Poziom

wysoki na LRCK oznacza, że

przesyłana jest próbka należą-

ca do kanału lewego, a niski,

że do prawego. Częstotliwość

sygnału aktywnego kanału

określa zarazem częstotliwość

próbkowania sygnału audio.

Narzędzia

Punktem wyjścia dla każ-

dego projektu mikroproce-

sorowego jest odpowiednia

baza sprzętowa i środowisko programowe.

Do implementacji cyfrowego toru audio wy-

korzystano dwa zestawy: STM32Butterfly2

i KAmodDIGA. Zestaw STM32Butterfly2

jest nowszą i zarazem bogatszą wersją zesta-

97ELEKTRONIKA PRAKTYCZNA 9/2010

Obsługa interfejsu I2

S

aplikacji jest tryb z obsługą magistrali I2

S,

któremu odpowiadają poziomy wysokie na

wyprowadzeniach FORMAT. Dla takiego

ustawienia długość ramki danych jednego

kanału może zmieniać się w przedziale od

16 do 24-bitów. Połączenie obydwu płytek

nie powinno sprawić żadnych problemów,

ponieważ obydwa moduły mają dobrze opi-

sane wyprowadzenia sygnałów.

Ustawianie sygnałów zegarowych

Wraz ze wzrostem poziomu skompliko-

wania układów, a co ważniejsze, ze wzro-

stem ich stopnia scalenia, coraz ważniejsza

staje się potrzeba zarządzania w układach

mikroprocesorowych sygnałami zegarowy-

mi o różnych częstotliwościach, zależnych

od rodzaju zastosowanych układów pery-

feryjnych. Mikrokontrolery STM32, nale-

żące od rodziny connectivity line, są wy-

posażone w imponującą liczbę peryferiów

komunikacyjnych, m. in.: Ethernet MAC

(opcjonalnie), USB OTG, I2

S. Implikuje to,

w przypadku symultanicznej pracy wielu

urządzeń, konieczność generowania sygna-

łów zegarowych o różnych a co ważniej-

sze ? ściśle określonych częstotliwościach.

W przypadku interfejsu I2

S normalizacja

częstotliwości próbkowania sygnału audio

powoduje, że mikrokontroler powinien ge-

nerować sygnał zegarowy związany liczbo-

wo z wartością tej częstotliwości.

Układy z rodziny STM32 connectivi-

ty line mają wbudowane aż trzy układy

PLL, dzięki którym możliwości generowa-

nia przebiegów taktujących są naprawdę

duże. Źródłem sygnału zegarowego dla

I2

S może być zegar systemowy SYSCLK

lub PLL3. Na rysunku 4 przedstawiono

bloki, które mogą brać udział w generowa-

niu sygnału zegarowego dla I2

S. Pomimo

tego, że możliwości ich konfigurowania

są spore, to mnożniki i dzielniki zostały

zoptymalizowane pod kątem rezonatorów

kwarcowych o częstotliwościach 25 MHz

i 14,7456 MHz. Zestaw STM32butterfly2

ma zamontowany rezonator o częstotliwo-

ści 14,7456 MHz.

Najprostszym sposobem wyznacze-

nia wszystkich mnożników i dzielników

jest ich pobranie z tabeli zamieszczonej

w dokumencie ?RM0008 Reference manu-

al?, dostępnym na stronie www.st.com/

stm32. Fragment tej tabeli zamieszczono

na rysunku 5. Są w niej podane wszystkie

niezbędne wartości oraz błędy wynikające

z zastosowanych ustawień. W programie

konfigurującym sygnały zegarowe przed-

stawionym na listingu 1 zastosowano za-

lecane w tabeli wartości dla FS

= 44,1 kHz.

Program z listingu pozwala na uzyskanie

sygnału taktowania kontrolera I2

S, a czę-

stotliwości pracy poszczególnych linii in-

terfejsu są określane już przez samo urzą-

dzenie peryferyjne, co opisano poniżej.

Rysunek 3. Schemat blokowy dekodera audio TS4657 [Źródło: STMicroelectonics]

Rysunek 4. Źródła sygnału zegarowego dla kontrolera I2

S

Rysunek 5. Tabela określania częstotliwości próbkowania [Źródło: STMicroelectonics]

cza montaż, ponieważ zazwyczaj na płytce

modułu jest wyprowadzone standardowe

złącze szpilkowe.

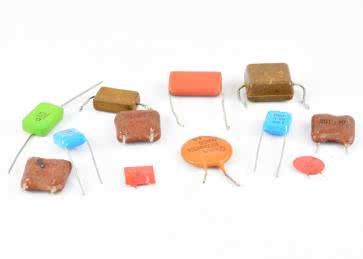

Do prawidłowej pracy układ TS4657

wymaga sygnału taktującego wynoszącego

256×częstotliwość próbkowania sygna-

łu audio FS

. Jak już wspomniano, przebieg

zegarowy jest dostarczany jedną linią in-

terfejsu I2

S, w postaci sygnału MCLK. Moc

wyjściowa układu jest wystarczająca do

zadowalającego wysterowania słuchawek.

Należy zwrócić uwagę, że dekoder może

pracować tylko częstotliwościami próbko-

wania z zakresu 32...48 kHz, dlatego nale-

ży przygotowywać sekwencje audio sprób-

kowane z częstotliwością należącą do tego

przedziału.

Kilka słów wyjaśnienia wymagają ak-

ceptowane przez dekoder formaty danych

wejściowych. Typ formatu jest wybierany

za pomocą stanów wyprowadzeń FOR-

MAT1 i FORMAT2. Na płytce modułu au-

dio (zastosowanego na potrzeby artykułu)

można go wybrać zworkami JP1 i JP2. Spo-

śród czterech trybów pracy najistotniejszym

z punktu widzenia przedstawionej niżej

wu STM32Butterfly, znanego z cyklu warsz-

tatów STM32TechDays przeprowadzonych

przez firmę STMicroelectronics. Najważ-

niejsze zmiany to m. in. dodanie złącz uła-

twiających dołączanie zewnętrznych modu-

łów, interfejsu USB Host oraz złącz dla kart

pamięci SD. Realizacja projektów przedsta-

wionych w artykule wymagała rozszerzenia

zestawu STM32Butterfly2 o moduł KAmod-

DIGA. Do przygotowania i przetestowania

zaprezentowanego dalej oprogramowania

użyto darmowej wersji środowiska Atollic

TrueSTUDIO.

Użyty moduł ?muzyczny? jest podsta-

wową aplikacją dekodera audio TS4657.

Jest to stereofoniczny, 16-bitowy przetwor-

nik C/A audio. Schemat blokowy układu

przedstawiono na rysunku 3. Układ jest

prosty w obsłudze. Wymaga tylko jednego

napięcia zasilania z przedziału 3...5,5 V.

Pewnym mankamentem w przypadku mon-

towania urządzeń prototypowych może być

mała obudowa dekodera typu QFN20, choć

jej montaż nawet w warunkach amatorskich

jest możliwy (co nie oznacza, że jest łatwy!).

Korzystanie z gotowych modułów uprasz-

98 ELEKTRONIKA PRAKTYCZNA 9/2010

NOTATNIK KONSTRUKTORA

Konfigurowanie I2

S

Sprzętowy kontroler interfejsu I2

S jest

wbudowany w mikrokontrolery STM32 na-

leżących do segmentu connectivity line oraz

high-density performance line. Interfejs I2

S

zaimplementowano jako dodatkową cechę

funkcjonalną interfejsu SPI, a więc oba ko-

rzystają z tych samych wyprowadzeń. Kon-

figurowanie wyprowadzeń dzięki bibliotece

API nie jest skomplikowana i nie nastręcza

trudności. Na listingu 2 zamieszczono frag-

ment programu, którego zadaniem jest usta-

wienie podstawowych parametrów pracy

magistrali, a następnie włączenie kontrolera

I2

S.

Mikrokontroler jest układem nadrzęd-

nego nadajnika dla dekodera audio, dlatego

jako tryb pracy I2S_Mode należy wybrać I2S_

Mode_MasterTx. Kontrolery I2

S w układach

STM32 obsługują sprzętowo pięć podsta-

wowych formatów ramek danych: I2S_Stan-

dard_LSB, I2S_Standard_MSB, I2S_Stan-

dard_PCMLong, I2S_Standard_PCMShort,

I2S_Standard_Philips. W aplikacjach oma-

wianych w dalszej części artykułu wykorzy-

stano ostatni format.

Próbki audio mogą być zapisywane

przy użyciu różnej liczby bitów. Zazwyczaj

w prostych interfejsach dźwiękowych na

jedną próbkę przypada 16 bitów. Pracę z taką

długością ramki umożliwia ustawienie pola

I2S_DataFormat na wartość określoną defini-

cją I2S_DataFormat_16b. Ponadto biblioteka

API umożliwia ustawienie długości ramek

na 24 lub 32 bity. Częstotliwość próbkowa-

nia jest ustalana przez modyfikację pola I2S_

AudioFreq struktury inicjującej kontroler I2

S.

Dostępne częstotliwości są zapisane w pliku

pomocy dostarczanym wraz z biblioteką pro-

gramistyczną API. W aplikacjach opisanych

poniżej używa się częstotliwości próbkowa-

nia 44,1 kHz, czyli wymienione pole struktu-

ry inicjującej powinno zostać zapisane war-

tością o definicji I2S_AudioFreq_44k. Para-

metr I2S_CPOL określa zachowanie się linii

zegarowej w stanie nieaktywnym - tutaj bę-

dzie ona sprowadzana do poziomu niskiego.

Ostatnią czynnością związaną z konfigu-

rowaniem interfejsu (wypełnianiem struk-

tury inicjującej) jest ? jeśli istnieje taka po-

trzeba ? włączenie sygnału MCLK. Dekoder

audio, zamontowany w module, do popraw-

nej pracy wymaga zewnętrznego sygnału

taktowania, a zatem wyjście MCLK zostało

aktywowane.

Wysyłanie danych może się odbywać

co najmniej trzema sposobami. Najprostszy

przypadek polega na ciągłym odpytywaniu

kontrolera I2

S, czy jego bufory nadawcze

są już puste. Nie jest to jednak rozwiązanie

ani efektywne, ani eleganckie. Znacznie lep-

szym jest użycie przerwania od kontrolera

I2

S. Jeszcze lepszym sposobem jest użycie

DMA do bezpośredniego przenoszenia da-

nych pomiędzy pamięcią (układem peryfe-

Listing 1. Konfigurowanie sygnałów zegarowych dla I2

S

/* Wlacznenie bufora dla pamieci Flash */

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

/* dwa ?wait state? */

FLASH_SetLatency(FLASH_Latency_2);

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

/* PCLK1 = HCLK/2 */

RCC_PCLK1Config(RCC_HCLK_Div2);

/* Konfiguracja PLL -----------------------------------------*/

/* PREDIV2: PREDIV2CLK = HSE / 6 = 2.45757 MHz */

RCC_PREDIV2Config(RCC_PREDIV2_Div6 );

/* PLL3: PLL3CLK = (HSE / 2) * 20 = 49.1513 MHz */

RCC_PLL3Config(RCC_PLL3Mul_20);

RCC_PLL3Cmd(ENABLE);

while(RCC_GetFlagStatus(RCC_FLAG_PLL3RDY) == RESET);

/* PLL2: PLL2CLK = (HSE / 2) * 20 = 49.1513 MHz */

RCC_PLL2Config(RCC_PLL2Mul_20);

RCC_PLL2Cmd(ENABLE);

while(RCC_GetFlagStatus(RCC_FLAG_PLL2RDY) == RESET);

/* PREDIV1: PREDIV1CLK = PLL2 / 3 = 16.38378 MHz */

RCC_PREDIV1Config(RCC_PREDIV1_Source_PLL2,RCC_PREDIV1_Div3);

/* PLL1: PLLCLK = PREDIV1 * 4 = 65.535 MHz */

RCC_PLLConfig(RCC_PLLSource_PREDIV1, RCC_PLLMul_4);

RCC_PLLCmd (ENABLE);

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);

/* PLL zrodlem zegara systemowego */

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

/* Czekaj na poprawny sygnal zegarowy */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08);

RCC_I2S2CLKConfig(RCC_I2S2CLKSource_PLL3_VCO);

Listing 2. Konfigurowanie kontrolera I2

S

I2S_InitTypeDef I2S_InitStructure;

I2S_InitStructure.I2S_Standard = I2S_Standard_Phillips;

I2S_InitStructure.I2S_DataFormat = I2S_DataFormat_16b;

I2S_InitStructure.I2S_MCLKOutput = I2S_MCLKOutput_Enable;

I2S_InitStructure.I2S_AudioFreq = I2S_AudioFreq_44k;

I2S_InitStructure.I2S_CPOL = I2S_CPOL_Low;

I2S_InitStructure.I2S_Mode = I2S_Mode_MasterTx;

I2S_Init(SPI2, &I2S_InitStructure);

SPI_I2S_ITConfig(SPI2, SPI_I2S_IT_TXE, ENABLE);

I2S_Cmd(SPI2, ENABLE);

Listing 3. Skrypt Octave/Matlab tworzący tablicę próbek w formacie pliku tekstowego

function wav2txt;

[fid] = fopen(?samples.txt?, ?w?);

[y, Fs, Nbits] = wavread(?input.wav?);

z = (y+1) * 32768;

len = length(z)

Fs

Nbits

for i=1:len

fprintf(fid, ?0x%X, ?, z(i));

rows = mod (i, 16);

if ~rows

fprintf(fid, ?\r\n?);

end;

end;

plot(z);

fclose(fid);

Listing 4. Funkcja NVIC_Configuration()

void NVIC_Configuration(void)

{

NVIC_InitTypeDef NVIC_InitStructure;

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0);

NVIC_InitStructure.NVIC_IRQChannel = SPI2_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

}

99ELEKTRONIKA PRAKTYCZNA 9/2010

Obsługa interfejsu I2

S

Listing 5. Obsługa przerwania od kontrolera I2

S

void SPI2_IRQHandler(void)

{

/* Sprawdzenie zrodla przerwania */

if (SPI_I2S_GetITStatus(SPI2, SPI_I2S_IT_TXE) == SET)

{

/* Wyslij dane przez I2S2 */

SPI_I2S_SendData(SPI2, (I2S2_Buffer_Tx[TxIdx] - 32768));

TxIdx++;

}

TxIdx &= (table_size + 1)

}

mi próbek w zapisie szesnastkowym. Wy-

starczy taką tablicę skopiować do programu

przeznaczonego dla mikrokontrolera jako ta-

blicę stałych wartości.

W aplikacji korzystano z mechanizmu

przerwań, dlatego przed ich użyciem i włą-

czeniem należy skonfigurować sterownik

przerwań NVIC. Odpowiada za to funkcja

NVIC_Configuration(), której kod zamieszczo-

no na listingu 4. Aby przerwanie działało pra-

widłowo, należy dodać do pliku stm32f10x_

it.c funkcję jego obsługi. Plik stm32f10x_it.c

jest automatycznie tworzony i dodawany do

projektu przez środowisko Atollic TrueSTU-

DIO. Nazwę funkcji można odczytać z tablicy

wektorów przerwań, w tym przypadku jest to

SPI2_IRQHandler(). Kod omawianej funkcji

zamieszczono na listingu 5.

Po uruchomieniu programu w mikrokon-

trolerze sekwencja audio zapisana w pamięci

Flash będzie odtwarzana dopóty, dopóki bę-

dzie włączone napięcie zasilania.

Krzysztof Paprocki, EP

krzysztof.paprocki@ep.com.pl

wyprowadzeń oraz włączeniu niezbędnych

sygnałów zegarowych.

Odtwarzacz audio

Dane audio mają być zapisane w pamię-

ci Flash mikrokontrolera, a więc należy je

wyłuskać np. z pliku *.wav. Prosty skrypt,

odczytujący dane z pliku wav i zapisujący je

do pliku tekstowego przedstawiono na listin-

gu 3. Skrypt można uruchomić w programie

Octave lub Matlab. Efektem jego wykonania

jest utworzenie w katalogu roboczym pliku

tekstowego z ułożonymi w tablicę wartościa-

ryjnym), a interfejsem I2

S. Ostatni przypadek

jest najbardziej efektywny pod względem

użycia mocy obliczeniowej jednostki central-

nej. Sprawa się nieco komplikuje, jeżeli dane

odczytywane z pamięci mają być modyfiko-

wane. W programie zaprezentowanym na

listingu 2 skorzystano z drugiej opcji, a więc

przyjęto, że wysyłanie danych następuje po

przerwaniu od pustego bufora nadawczego

kontrolera I2

S. Na koniec konfigurowania I2

S

trzeba jeszcze włączyć urządzenia przez wy-

wołanie funkcji I2S_Cmd(). Nie należy także

zapominać o odpowiednim konfigurowaniu

R E K L A M A

forum.ep.com.pl

Zobacz więcej w kategorii Notatnik konstruktora

Zaloguj

Zaloguj