W tym odcinku cofniemy się trochę w czasie. Dla pewnej grupy Czytelników będzie to podróż sentymentalna, dla młodszych zaś odkryjemy na nowo stary świat. Trudno sobie wyobrazić, aby nawet najmłodsi czytelnicy nigdy nie słyszeli o układach TTL, całkiem realne wydaje się natomiast, że duża część z nich nigdy nie miała takich układów w ręku. Rewolucyjne zmiany technologiczne zaszły, jakby nie patrzeć, już co najmniej kilkanaście lat temu. Przypomnijmy zatem krótko na czym polegały.

Rys historyczny

Pierwsze układy cyfrowe były produkowane w technologii bipolarnej. Charakterystyczna dla niej skala upakowania elementów w układach scalonych nie była początkowo zbyt wielka, ale wystarczająca w tym względzie. Przykładowo, podstawowy funktor logiczny – bramka NAND – zawierała 3 zwykłe tranzystory NPN i jeden tranzystor wieloemiterowy. W jednym układzie scalonym mieściły się 4 takie bramki. W sumie było więc 16 tranzystorów i tyleż rezystorów. Do pełnej realizacji układu scalonego należy jeszcze dodać kilka diod. Jeśli te osiągnięcia porównamy z współczesnymi układami cyfrowymi, to nie sposób uniknąć uśmiechu politowania, ale w tamtych czasach wszyscy byli zachwyceni tworzącą się właśnie nową dziedziną elektroniki. Pamiętajmy jednak, że układy 7400 z różnymi dodatkami literowymi przy oznaczeniu wynikającymi z kolejnych technologii są produkowane do dziś i trudno sobie wyobrazić, aby technika cyfrowa istniała bez układów realizujących podstawowe funkcje logiczne. Podobną budowę miały również inwertery NOT, bramki AND, OR, NOR, XOR, a także bogata kolekcja bardziej rozwiniętych układów, takich jak przerzutniki, liczniki, dekodery, multipleksery i wiele innych. Ze względu na zasadę działania rodzinę tę nazwano Transistor Transistor Logic, a do powszechnego użytku weszła nazwa TTL. Pierwszą bramkę NAND wyprodukowano w roku 1964 , a więc rok przed nagraniem „Michelle” zespołu The Beatles.

Układy TTL, z dzisiejszego punktu widzenia, charakteryzowały się bardzo dużym poborem mocy. Punkty pracy tranzystorów dobrano tak, aby płynęły przez nie stosunkowo duże prądy.

Niemal równolegle z układami TTL rozwijała się technologia CMOS. W tej rodzinie radykalnie obniżono zużycie mocy, były one jednak wyraźnie wolniejsze od TTL-i, ale największą ich wadą była wrażliwość na zewnętrzne pola elektrostatyczne. Montaż układów CMOS wymaga spełnienia szczególnych warunków. Już krótkie dotknięcie wyprowadzeń gołą ręka może spowodować nieodwracalne zniszczenie struktury. Cecha ta zniechęcała wielu amatorów od stosowania układów CMOS. Nowoczesne układy mają szereg zabezpieczeń zwiększających odporność na pola elektrostatyczne. Niestety technologie CMOS i TTL nie zachowują kompatybilności pod względem poziomów logicznych. Stanowi to pewną trudność w łączeniu obu tych technologii w jednym urządzeniu. Często w projektach łączących różne technologie konieczne jest uwzględnianie specjalnych translatorów.

Duży pobór mocy układów TTL i chęć poprawy ich szybkości stał się pretekstem do poszukiwania nowych rozwiązań. Jako pierwsza powstała rodzina TTL-S, w której zastosowano diodę Schottky’ego łączoną zaporowo do złącza klektor-baza. Zmniejszała ona pojemność tego złącza, a zatem skracała czas jej przeładowywania. Niestety, okazało się, że układy TTL-S choć szybsze od zwykłych TTL-i charakteryzowały się jeszcze większą prądożernością. Pozostając przy tych rozwiązaniach układowych można było jedynie zwiększyć rezystancje wewnętrzne i zmniejszyć napięcie zasilające. Ostatecznie powstała więc rodzina TTL-LS (Low Power Schottky TTL). Jest to właściwie stan obowiązujący dzisiaj. Obecnie, mówiąc o układach TTL myślimy zwykle o odmianie TTL-LS 3,3 V, a o klasycznych TTL-ach już prawie nikt nie pamięta.

Standardowa bramka TTL – symulacja i pomiary statyczne

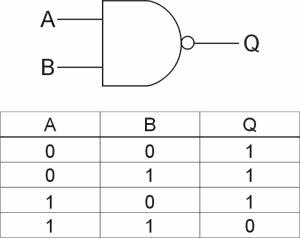

Cofnijmy teraz zegary, wróćmy do czasów panowania standardowej bramki TTL. Jest to umownie przyjęty okres między latami sześćdziesiątymi a dziewięćdziesiątymi XX wieku. Na warsztat bierzemy podstawowy funktor logiczny, jakim jest bramka NAND. Ograniczamy się do bramki 2-wejściowej. Schemat logiczny wraz z tablicą prawdy tego funktora został pokazany na rysunku 1. Zadaniem konstruktorów bramki NAND było zaprojektowanie takiego układu, który podczas normalnej pracy mógłby przyjmować jedynie dwa dozwolone stany wyjściowe: niski i wysoki. Stan niski powinien występować jedynie w przypadku, gdy na oba wejścia są podawane jednocześnie stany wysokie.

Wszystko wygląda bardzo pięknie, tylko że zaklasyfikowanie jakiegoś układu do rodziny układów cyfrowych jest umowne. De facto każdy układ jest analogowy. Bez głębszej analizy można przypuszczać, że napięcie wyjściowe dla określonego stanu (niskiego lub wysokiego) nie będzie utrzymywało się na stałym poziomie. Z pewnością będzie ono zależało od obciążenia wyjścia bramki, być może od szybkości zmian stanu wyjściowego. Można również przypuszczać, że napięcie wyjściowe w określonym stanie będzie zależało od napięcia wejściowego, nawet jeśli mieści się ono w dozwolonym zakresie. Konieczne stało się zatem zdefiniowanie zakresów napięć dla stanu niskiego i wysokiego.

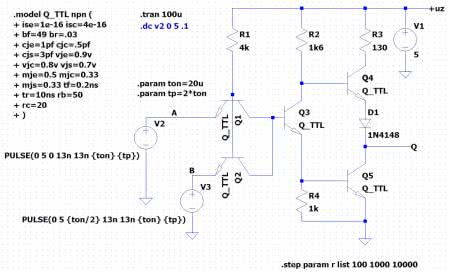

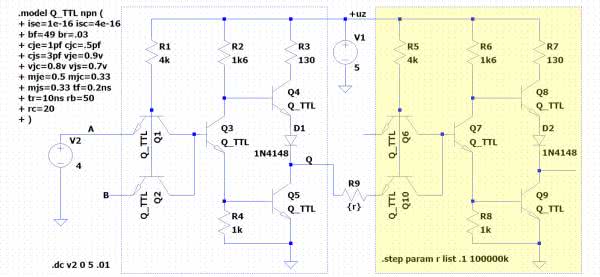

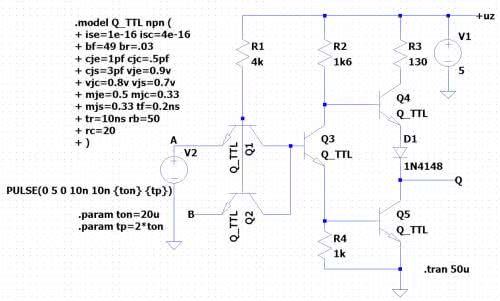

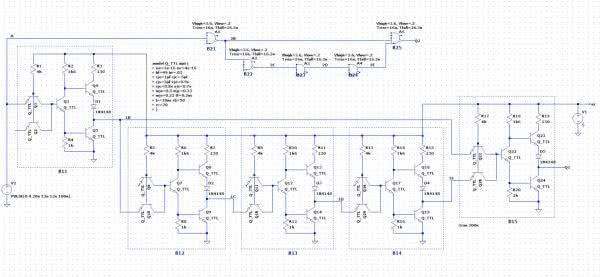

Nie będziemy powtarzać projektu, sprawdzimy jedynie efekt pracy jaką wykonali wiele lat temu konstruktorzy. Najpierw przeprowadzimy symulację pojedynczej bramki NAND zawartej w układzie 7400. Problemem do rozwiązanie jest zamodelowanie wejściowego tranzystora dwuemiterowego. W standardowej bibliotece LTspice’a nie ma takiego elementu, zastosujemy dwa tranzystory z połączonymi bazami i kolektorami (tanzystory Q1 i Q2 na rysunku 2). Należy jeszcze wybrać typ tranzystora, który najlepiej odpowiadałby tranzystorom układu scalonego. Po kilku próbach odrzucamy modele typowych tranzystorów dyskretnych, zastosujemy tranzystor o poniższym modelu:

.model Q_TTL npn (

+ ise=1e-16 isc=4e-16

+ bf=49 br=.03

+ cje=1pf cjc=.5pf

+ cjs=3pf vje=0.9v

+ vjc=0.8v vjs=0.7v

+ mje=0.5 mjc=0.33

+ mjs=0.33 tf=0.2ns

+ tr=10ns rb=50

+ rc=20

+ )

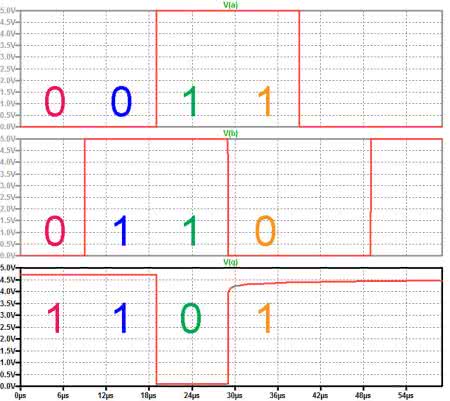

Definicję tego modelu umieszczamy na arkuszu roboczym symulatora. Najpierw zweryfikujemy układ pod względem logicznym. Do wejść doprowadzamy dwa przebiegi prostokątne o parametrycznie zadanym czasie trwania impulsu .param ton=20u i czasie powtarzania .param tp=2*ton. Źródło V3 ma dodatkowo wprowadzone opóźnienie równe ton/2. Dzięki temu można łatwo wygenerować wszystkie kombinacje stanów wejściowych i sprawdzić czy na wyjściu pojawią się stany zgodne z tablicą prawdy. Wyniki symulacji zostały pokazane na rysunku 3. Jak widać, układ działa zgodnie z oczekiwaniami.

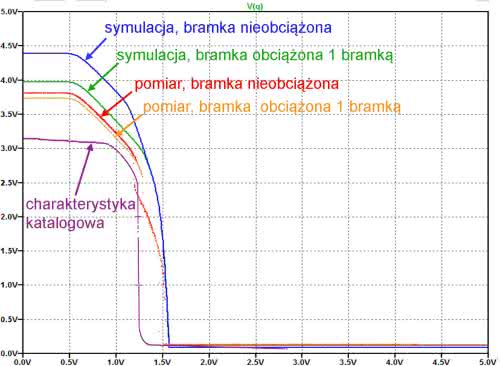

Sprawdźmy teraz jak wygląda charakterystyka przejściowa symulowanej bramki NAND, badamy więc zależność napięcia wyjściowego od wejściowego. Porównamy ją z analogicznymi charakterystykami często zamieszczanymi w literaturze, a na koniec zmierzymy tę charakterystykę sami w układzie rzeczywistym. Należy zauważyć, że niepodłączone wejście zachowuje się tak, jakby był do niego podany stan wysoki. W praktyce zwykle jest ono jednak dołączane do napięcia zasilania przez rezystor o oporności kilku kΩ, dzięki czemu zabezpieczamy się przed wyłapywaniem zakłóceń przez wejście niepodłączone. W symulacji takich zakłóceń oczywiście nie będzie, więc niewykorzystane wejście (np. B) możemy pozostawić bez żadnego połączenia.

Do wykonania charakterystyki przejściowej korzystamy z symulacji „DC Sweep”. Źródłem wejściowym jest V2. Napięcie zmieniamy w zakresie od 0 do 5 V z krokiem 0,01 V – polecenie .dc v2 0 5 .01. Schemat pomiarowy został pokazany na rysunku 4, zaś wyniki symulacji na rysunku 5. W układzie pomiarowym występują dwie bramki. Wyjście pierwszej jest połączone z wejściem drugiej przez rezystor o parametrycznie określonej rezystancji: .step param r list .1 100000k. W pierwszym kroku wyznaczana jest więc charakterystyka bramki obciążonej jedną bramką (podświetloną na żółto), w drugim kroku można uznać, że pierwsza bramka (badana) pozostaje nieobciążona. Z uzyskanych charakterystyk wynika, że obciążenie jedną bramką spowodowało obniżenie napięcia wyjściowego o ok. 0,4 V. Napięcia wyjściowe w stanie wysokim przy braku obciążenia i z obciążeniem jedną bramką wahają się w układzie symulowanym w przedziale od ok. 4 V do 4,4 V. Pomiary wygrzebanego z szuflady układu UCY7400 wykazały, że napięcia te w analogicznym przypadku zmieniają się od 3,7 V do 3,82 V.

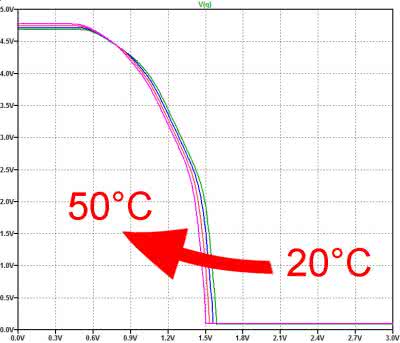

W katalogach można znaleźć charakterystyki, w których napięcie to jest równe ok. 3,2 V i może wystąpić przy maksymalnym obciążeniu bramki. Różnica pomiędzy charakterystykami wynika poza tym z nieidealnych modeli tranzystorów układu scalonego. Należałoby ponadto uwzględnić wpływ temperatury na charakterystyki. W tym celu wprowadzamy opcję: .option temp {temperatura} oraz komendę .step param temperatura list 20 30 40 50. Uzyskujemy w ten sposób rodzinę charakterystyk dla temperatur: 20°C, 30°C, 40°C, i 50°C (rysunek 6).

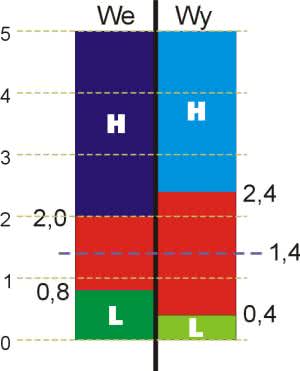

Ważnym parametrem układów cyfrowych są dopuszczalne zakresy napięć dla stanu niskiego i wysokiego w odniesieniu do wejścia i wyjścia. Ze względu na zmiany napięć powodowane różnymi przyczynami konieczne jest zachowanie odpowiednich marginesów rozdzielających stan niski od wysokiego. Dla standardowych układów TTL przyjęto, że dopuszczalne napięcie wejściowe dla stanu niskiego może zawierać się w przedziale od 0 V do 0,8 V, a dla stanu wysokiego od 2 V do 5 V. Analogiczne zakresy dla napięcia wyjściowego: od 0 V do 0,4 V dla stanu niskiego i od 2,4 V do 5 V dla stanu wysokiego (rysunek 7).

Standardowa bramka TTL – symulacja i pomiary dynamiczne

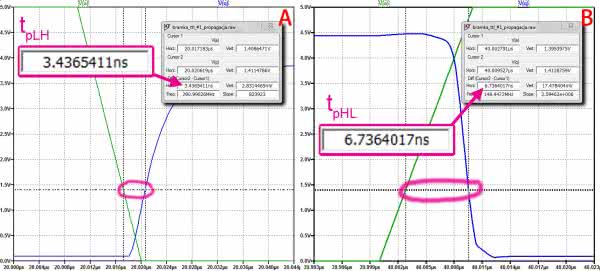

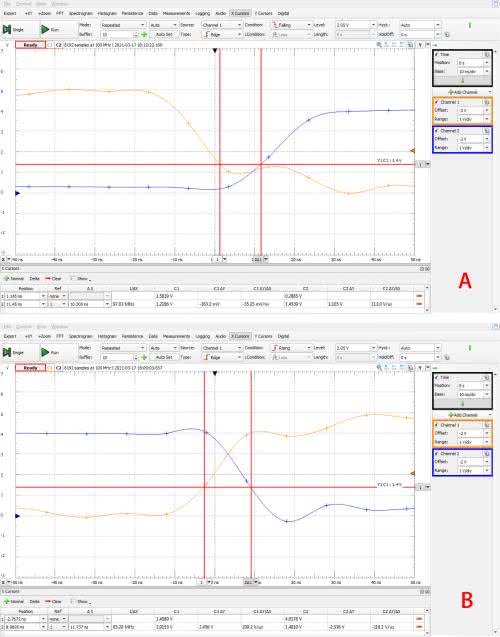

Sprawdzimy teraz jak symulator poradzi sobie z parametrami dynamicznymi. Wyniki symulacji pokażą, jak dobrym modelem tranzystorów dysponujemy, gdyż to on decyduje o zależnościach czasowych występujących w bramce NAND. Podstawowym parametrem dynamicznym układów cyfrowych jest czas propagacji. Jest to czas, po którym na wyjściu układu pojawia się odpowiedź na wymuszenie. W praktyce rozróżnia się czasy propagacji dla zmian ze stanu niskiego na wysoki (tpLH) oraz dla zmian ze stanu wysokiego na niski (tpHL). Konieczne jest jeszcze ustalenie napięcia, dla jakiego dokonywany jest pomiar czasu. Popatrzmy jeszcze raz na graficzną interpretację przyjętych napięć dla poszczególnych stanów logicznych (rysunek 7). Średnie napięcie strefy zabronionej zarówno dla wejścia, jak i dla wyjścia jest równe 1,4 V.

Napięcie to jest przyjmowane jako odniesienie dla pomiarów czasu propagacji. Naszym zadaniem jest więc określenie momentu, w którym napięcie wejściowe przyjmuje wartość 1,4 V i zmierzenie czasu, po którym tę samą wartość przyjmuje napięcie wyjściowe. Pomiar powtarzamy dla zmian stanu w obu kierunkach. Przyjmujemy, że czas zmiany stanu wyidealizowanego przebiegu wejściowego od 0 do 5 V, a także od 5 V do 0 jest równy 10 ns. Schemat pomiarowy przedstawiono na rysunku 8, wyniki natomiast na rysunku 9.

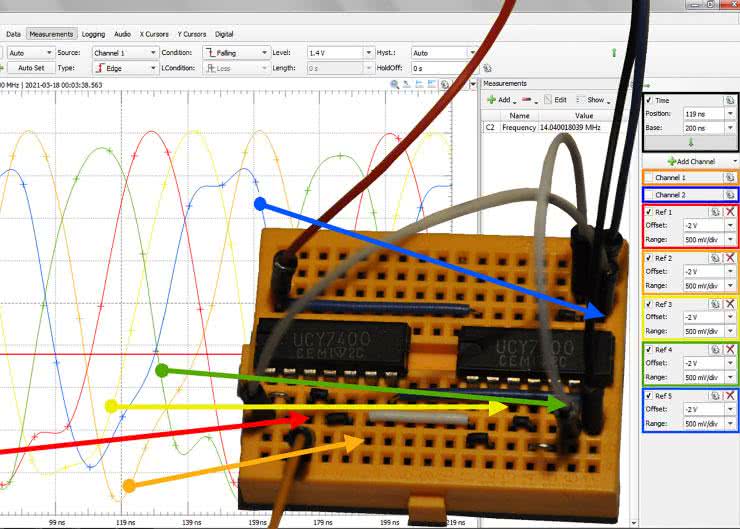

Wynika z nich, że czas tpLH symulowanej bramki jest równy 3,4 ns, a czas tpHL 6,7 ns. Są to czasy dużo krótsze niż katalogowe. Pomiar tych parametrów w układzie rzeczywistym dał wyniki: tpLH=10,3 ns i tpHL=11,7 ns (rysunek 10).

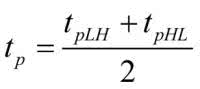

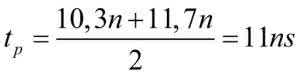

Często podaje się jeden uśredniony czas propagacji równy:

W tym przypadku uśredniony czas rzeczywistej mierzonej bramki byłby równy:

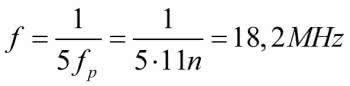

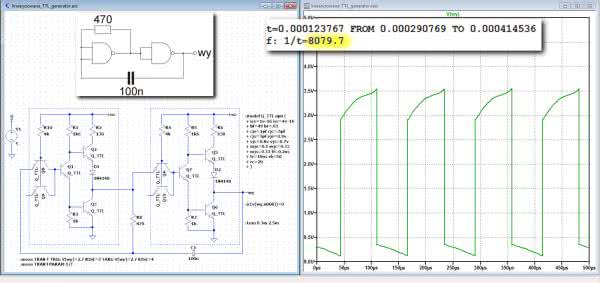

Wyobraźmy sobie teraz układ pokazany na rysunku 11. Połączono tu kaskadowo nieparzystą liczbę bramek. Jeśli na wejściu pierwszej występuje stan 1, to na kolejnych wyjściach powinny występować stany: 0-1-0-1-0. Ale jeśli stan wysoki na wejściu podamy w określonym momencie, to stan niski na wyjściu ostatniej bramki pojawi się dopiero po czasie równym sumie czasów propagacji 5 bramek, a więc z pewnym opóźnieniem. Połączenie wyjścia ostatniej bramki z wejściem pierwszej powinno więc spowodować oscylacje o częstotliwości:

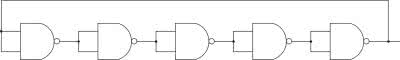

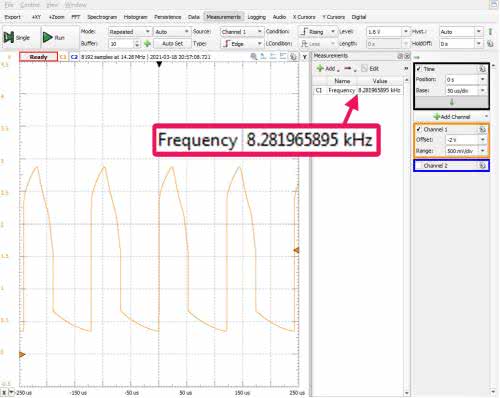

Nie pozostaje nic innego, jak tylko naocznie przekonać się czy tak będzie rzeczywiście. Montujemy układ według schematu z rysunku 11. Emocje rosną. Rzeczywiście, w układzie pojawiły się oscylacje (rysunek 12). Ich częstotliwość jest równa 14,25 MHz, a więc znacznie mniej niż się spodziewaliśmy. Odpowiedź na pytanie skąd wynika taka różnica nie jest prosta. Pierwszą przyczyną może być rozrzut czasów propagacji poszczególnych bramek, tym bardziej że do eksperymentu konieczne jest użycie dwóch układów scalonych. Różnica może również wynikać, z błędów pomiaru czasów tpLH i tpHL.

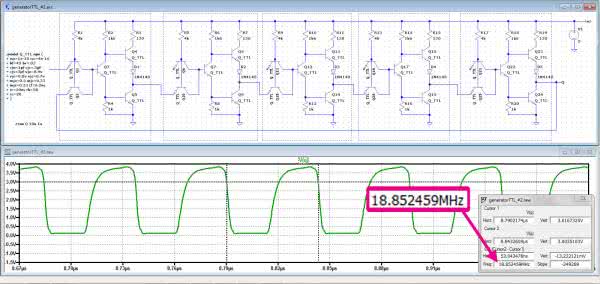

Prawdopodobnie wielu czytelnikom przyszedł do głowy pomysł, aby przeprowadzić symulację analogicznego pomiaru. Spodziewamy się uzyskać znacznie większą częstotliwość oscylacji, gdyż czas propagacji symulowanej bramki był krótszy od jej rzeczywistego odpowiednika.

Powielamy 5-krotnie naszą bramkę i łączymy tak uzyskany zestaw zgodnie ze schematem z rysunku 11. Schemat układu symulowanego i wyniki symulacji zostały pokazane na rysunku 13. Wynik: 18,85 MHz, a więc więcej niż w pomiarze.

Multiwibrator na bramkach TTL

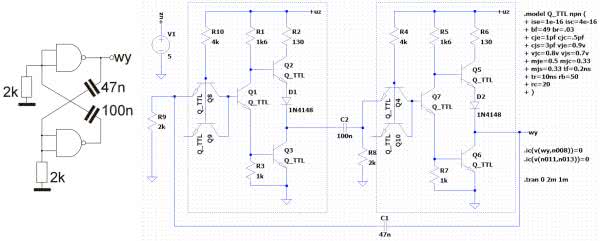

W czasach panowania układów TTL, w aplikacjach o niewygórowanych wymaganiach bardzo często był stosowany prosty układ multiwibratora astabilnego zbudowany na dwóch bramkach NAND, dwóch rezystorach i dwóch kondensatorach.

Schemat układu i jego realizację w symulatorze LTspice pokazano na rysunku 14, a wyniki symulacji na rysunku 15.

Przy wartościach elementów takich jak na schemacie częstotliwość drgań symulowanego układu jest równa 3,625 kHz. Należy zwrócić uwagę na dwie instrukcje użyte w symulacji:

.ic(v(wy,n008))=0

.ic(v(n011,n013))=0

Wymuszają one zerowe napięcie na obu kondensatorach w chwili startu symulacji. Bez tego zabiegu nasz multiwibrator nie wzbudziłby się.

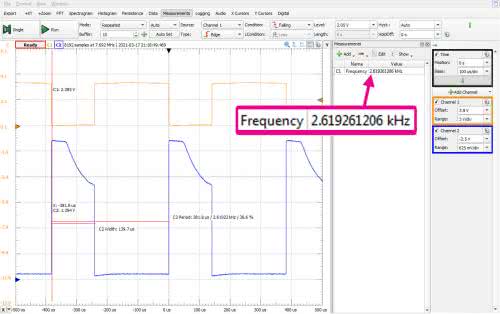

Szybko budujemy analogiczny układ i mierzymy częstotliwość jego drgań. Okazuje się, że jest ona równa 2,62 kHz (rysunek 16). Tym razem taka różnica nie powinna dziwić, gdyż może wynikać z tolerancji użytych elementów. Symulacja metodą Monte Carlo (opisaną w odcinku 13. kursu) przy założeniu 10-procentowych tolerancji rezystancji i pojemności wykazała, że częstotliwość drgań takiego multiwibratora może się zmieniać w szerokim przedziale (1688...4380 Hz).

Zlinearyzowana bramka TTL

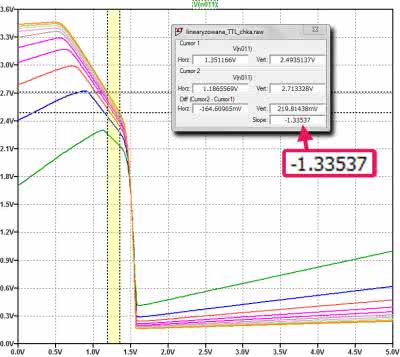

Do konstruowania prostych generatorów dość powszechnie był kiedyś stosowany zabieg linearyzacji bramek. Polegał on na połączeniu wyjścia bramki z jej wejściem przez rezystor o rezystancji kilkuset omów. Przykładową rodzinę takich charakterystyk dla kilku wartości rezystancji pokazano na rysunku 17.

Można na nich wyróżnić 4 strefy. W pierwszej wzmocnienie jest mniejsze od 1 V/V. W drugiej strefie, zaznaczonej na rysunku kolorem żółtym, bramkę możemy traktować jak wzmacniacz odwracający o wzmocnieniu nieznacznie większym od jedności (znak minus oznacza odwracanie fazy). W strefie trzeciej wzmocnienie to szybko wzrasta do ok. 20 V/V, a począwszy od napięcia wejściowego powyżej 1,6 V bramka staje się znowu wzmacniaczem nieodwracającym o wzmocnieniu mniejszym od 1 V/V.

Taką bramkę można użyć do budowy prostego generatora. Schemat generatora na zlinearyzowanej bramce NAND oraz wyniki symulacji zostały pokazane na rysunku 18, a wyniki pomiarów na rysunku 19. W niektórych jego odmianach zamiast kondensatora są stosowane rezonatory kwarcowe, co znacząco zwiększa precyzję generowanej częstotliwości.

Uwaga na współczesne odmiany układów TTL

Zaprezentowane przykłady symulacji bramki TTL dotyczą wyłącznie klasycznej jej odmiany. Już pierwsze modyfikacje tej technologii, takie jak TTL-S, TTL-LS powodowały na tyle duże zmiany parametrów, że symulacja bramek z zastosowaniem pokazanych modeli stają się zupełnie niewiarygodne. Dotyczy to wszystkich serii układów bipolarnych, a więc S, LS, F, AS i ALS. Tym bardziej dotyczy to technologii mieszanych, tzw. BICMOS, a w nich serii: ABT, ABTE, ALB, ALVT, BCT, FB, GTL, HSTL, JTAG, LVT czy SSTL.

Biblioteczne funktory logiczne symulatora LTspice

Program LTspice jest przeznaczony do symulacji układów analogowych, jednak jak już wielokrotnie w tym cyklu wspominałem, we współczesnych urządzeniach elektronicznych łączenie bloków analogowych z cyfrowymi stało się zabiegiem niemal rutynowym. Oczywiście nikt nie będzie modelował poszczególnych funktorów, tak jak to robiliśmy w przykładach opisanych wcześniej. Do symulacji układów cyfrowych służą programy przeznaczone specjalnie do tego celu. Natomiast, jeśli działanie jakiegoś bloku analogowego ma zależeć np. od wypracowanego cyfrowo układu sterującego, implementacja bloku cyfrowego staje się koniecznością.

Standardowa biblioteka LTspice’a zawiera kilka podstawowych funktorów logicznych, przerzutników, liczników itp. Są to jednak elementy bardzo specyficzne, gdyż nie są związane z żadną technologią i... nie wymagają zasilania. Standardowe napięcie w stanie niskim jest równe 0, a w stanie wysokim 1 V. Są to układy idealne – mają zerowy czas propagacji. Nie rozróżniamy bramek 2-, 4- czy 8-wejściowych. Jest jeden uniwersalny element o 5 wejściach. Aby dany funktor pracował zgodnie z jego tablicą prawdy nie musimy dbać o podanie odpowiednich stanów na niewykorzystywane wejścia. Symulator nie uwzględnia w analizie niepodłączonych wejść. Pobrana z biblioteki bramka ma dwa wyjścia, może być więc traktowana jednocześnie jako AND lub NAND.

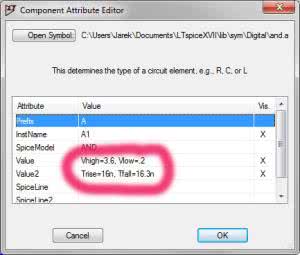

O ile taki element mógłby być wykorzystywany do badania realizacji funkcji logicznych na bramkach, to zastosowanie go do symulacji układów rzeczywistych byłoby raczej nieprzydatne. Aby przybliżyć modele standardowych funktorów logicznych do ich rzeczywistych odpowiedników uwzględniono możliwość wprowadzenia kilku parametrów. Są to na przykład:

- Vlow – napięcie w stanie niskim,

- Vhigh – napięcie w stanie wysokim,

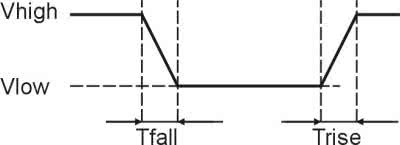

- Trise – czas narastania,

- Tfall – czas opadania.

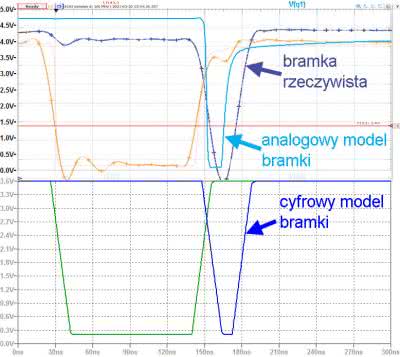

Komentarza wymagają dwa parametry dotyczące czasów, gdyż nie odpowiadają one katalogowym odpowiednikom. Na przykład Trise to czas, po którym napięcie wyjściowe bramki narasta (liniowo) od napięcia Vlow, do napięcia Vhigh (rysunek 20).

Na ile takie podejście przybliża wynik symulacji do rzeczywistości przekonamy się budując układ generowania opóźnionego impulsu. Tradycyjnie zrealizujemy go na symulowanych modelach bramki TTL, na bibliotecznych funktorach LTspice’a i na układach rzeczywistych. Wymienione wyżej parametry bramek definiuje się po kliknięciu prawym przyciskiem myszki na bramce umieszczonej w obszarze roboczym symulatora (rysunek 21).

Przyjmujemy: Vlow=0,2 V, High=3,6 V, Trise=16 ns, Tfall=16,3 ns. Opóźnienie impulsu wyjściowego wynika z czasu propagacji sygnału wymuszającego przez 3 bramki (rysunek 22).

Opóźniony sygnał jest mnożony logicznie przez bramkę wyjściową z sygnałem wymuszającym, w wyniku czego powstaje wąski impuls przesunięty dodatkowo o kilkanaście nanosekund względem przebiegu wejściowego. W zaprezentowanym układzie został on wygenerowany celowo, ale stanowi dobrą ilustrację hazardu często występującego w źle zaprojektowanych układach cyfrowych. Wyniki symulacji i pomiarów zostały pokazane na rysunku 23. Bramki B11 i B21 pełnią funkcję bufora wejściowego.

Znaczenie modelu tranzystorów użytych do analogowej implementacji bramki TTL

Mimo, że bramkę TTL skonstruowano ponad pół wieku temu, to tranzystory w niej zastosowane odznaczają się znacznie lepszymi parametrami dynamicznymi niż współcześnie dostępne popularne tranzystory dyskretne, np. 2N3904. W pierwszym podejściu do symulacji bramki TTL zastosowałem tranzystory właśnie tego typu. Okazało się, że taka bramka mogłaby pracować do częstotliwości zaledwie ok. 600 kHz. Jako standardowy element w modelu bramki użyłem diody 1N4148, ale prawdopodobnie jej parametry nie wpływają istotnie na działanie bramki.

Jarosław Doliński, EP

Zaloguj

Zaloguj