STM32WB55xx jest pierwszym układem dostępnym w serii STM32WB [2]. Jego 2-rdzeniowa architektura jest zoptymalizowana do pracy z komunikacją radiową w czasie rzeczywistym. Wewnętrzne regulatory napięcia i rozbudowane zarządzanie zasilaniem umożliwiają pracę przy bardzo małym poborze mocy. Przy zasilaniu napięciem z zakresu 1,71…3,6 V (–40…+85/105°C) układ pobiera prąd o zróżnicowanym natężeniu, zależnym od trybu pracy:

- Shutdown: 13 nA.

- Standby+RTC+32 kB RAM: 600 nA.

- Stop2+RTC+256 kB RAM: 2,1 μA.

- Run+RF (SMPS): <53 μA/MHz.

Układ jest wyposażony w szybką pamięć Flash (do 1 MB) z mechanizmami zabezpieczenia sektorów (PCROP) oraz pamięć SRAM (do 256 kB), w tym 64 kB z kontrolą parzystości. Pamięć Flash umożliwia przechowywanie programu, danych lub kluczy użytkownika. Zastosowano układ adaptive real-time accelerator (ART Accelerator) umożliwiający pracę rdzenia ARM Cortex-M4F z pamięcią Flash przy zerowych cyklach oczekiwania. Każdy układ zawiera łącze Quad-SPI obsługujące interfejs do zewnętrznej pamięci Flash (dostępnej w przestrzeni adresowej mikrokontrolera). Wbudowany bootloader obsługuje interfejsy USART, SPI, I2C oraz USB.

Udostępnionych jest też wiele wyprowadzeń I/O (do 72), z czego do 70 wyprowadzeń toleruje wejściowe napięcie 5 V. Dla układu STM32WB55xx firma STMicroelectronics udostępnia certyfikowany stos protokołu OpenThread oraz stos BLE 5. Jest możliwość aktualizacji oprogramowania poprzez transmisję radiową OTA (Over the Air) z użyciem obu protokołów. Układ może też prowadzić jednoczesną (concurrent) transmisję z dwoma protokołami BLE5 i OpenThread.

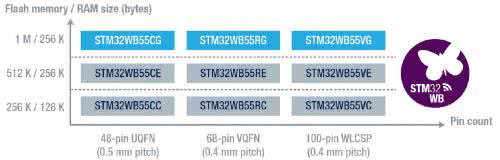

Układy scalone STM32WB55xx są oferowane w trzech rodzajach obudowy oraz z trzema pojemnościami pamięci Flash/RAM (rysunek 1). Rodzaj obudowy jest identyfikowany w nazwie układu pierwszą literką po numerze, gdzie:

- C: UFQFPN48, 7 mm×7 mm, 0,5 mm pitch, 30 GPIO, LCD (COM×SEG) 4×13,

- R: VFQFPN68, 8 mm×8 mm, 0,4 mm pitch, 49 G PIO, L CD (COM×SEG) 7×23 lub 4×26,

- V: WLCSP100, 0,4 mm pitch, 72 GPIO, LCD (COM×SEG) 8×40 lub 4×44.

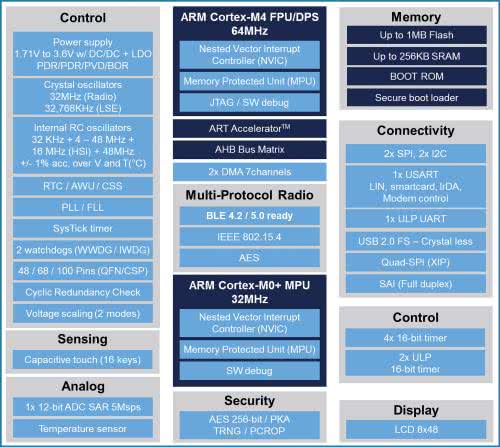

Ogólny schemat budowy układu STM32WB55 pokazano na rysunku 2. Układ ma dużą liczbę modułów peryferyjnych, w tym trzy analogowe: przetwornik A/C 12 bit 4,26 MSa/s, dwa komparatory oraz dokładne, buforowane źródło napięcia odniesienia 2,5 V lub 2,048 V.

Peryferyjne układy cyfrowe obejmują:

- 1×USART (ISO 7816, IrDA, SPI Master, tryby Modbus oraz Smartcard),

- 1×LPUART (Low Power),

- 2×SPI 32 Mbit/s,

- 2×I2C (SMBus/PMBus),

- 1×SAI (dwukanałvowe audio),

- 1×USB 2.0 (FS, BCD oraz LPM),

- Sterownik Touch Sensing (do 28 kanałów),

- Sterownik wyświetlacza LCD (do 8×40) z konwerterem napięcia,

- 16-bitowy, 4-kanałowy timer,

- Dwa 16-bitowe, 2-kanałowe timery,

- 32-bitowy, 4-kanałowy timer,

- Dwa 16-bitowe, 2-kanałowe timery o bardzo małym poborze mocy.

Dokumentacja

Poszukiwania dokumentacji dotyczącej układów scalonych serii STM32WB należy zacząć od strony serii [2]. Tam można zaleźć odnośniki do stron poszczególnych wersji układu scalonego. Można zacząć od odnośnika dla układu w największej obudowie STM32WB55VG [3], ponieważ dokumentacja jest wspólna dla wszystkich wersji układów. Na stronie tego produktu jest spory opis wstępny a potem odnośnik do dokumentu Data Sheet (DS11929 [5]) Multiprotocol wireless 32-bit MCU Arm-based Cortex-M4 with FPU, Bluetooth Low Energy and 802.15.4 radio solution. Drugi odnośnik udostępnia całkiem już spory dokument Device Errata (ES0394 [4]) z lutego 2019.

Na tej stronie można jeszcze znaleźć prezentację New STM32WB Series MCU with built-in BLE 5 and IEEE 802.15.4 [6] oraz broszurkę STM32WB Wireless Series with BLE 5.0 & IEEE 802.15.4 [7]. I to jest wszystko, co jest dostępne na portalu firmowym na końcu lutego 2019 r.

Szczegółowy opis układu zawiera Reference manual (RM0434) STM32WB55xx advanced Arm®-based 32-bit MCUs [8]. Opis zestawu uruchomieniowego P-NUCLEO-WB55 zawiera dokument Bluetooth Low Energy and 802.15.4 Nucleo pack based on STM32WB Series microcontrollers, User manual [9].

W Internecie można jeszcze znaleźć sporo informacji o serii STM32WB, tyle że nieaktualnych, z początku roku 2018.

Układ scalony STM32WB55xx

Opisywanie budowy układu scalonego STM32WB55xx nie jest łatwe. W dokumentacji są zamieszczone listy cech układu oraz dokładny opis poszczególnych bloków układu. Jednak nie ma opisu ogólnego architektury. Jest zdawkowy opis dla modułu rdzenia ARM Cortex-M4F (CPU1) oraz zupełny brak opisu dla modułu rdzenia ARM Cortex-M0+ (CPU2). Oczywiście, w opisach szczegółowych jest dokładnie omówione, np. jak pamięć Flash współpracuje z rdzeniem CPU1 oraz CPU2. Ale są to szczegóły porozrzucane po całej bardzo obszernej dokumentacji.

Nowy układ scalony serii STM32WB to praktycznie układ serii STM32L4 (z układami peryferyjnymi) z dodanym procesorem ARM Cortex M0+ oraz modułem radiowym. Oznacza to trzy autonomiczne podsystemy:

- ARM Cortex-M4F ( 64 M Hz): ( CPU1), g łówny p rocesor aplikacyjny.

- ARM Cortex-M0+ (32 M Hz): (CPU2), procesor k omunikacyjny, obsługa stosów komunikacyjnych.

- Moduł radiowy: (Radio System), składający się z bloku radiowego oraz bloków obsługi standardów BLE5.0 oraz IEEE 802.15.4.

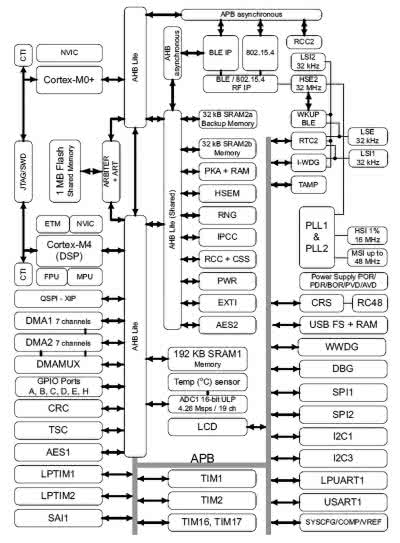

A właściwie jest to pięć autonomicznych podsystemów, ponieważ układ ma jeszcze dwa bardzo rozbudowane układy DMA1 i DMA2. Schemat blokowy układu scalonego STM32WB55 jest pokazany na rysunku 3.

Komunikacja i współdzielenie modułów peryferyjnych pomiędzy rdzeniem ARM Cortex-M4F oraz ARM Cortex-M0+ jest wykonywana poprzez sterownik Inter Processor Communication Controller (IPCC) oraz blok semaforów (HSEM) dostarczający 32 semafory z obsługą sprzętową [8]. Komunikacja międzyrdzeniowa jest wykonywana z zastosowaniem znormalizowanego API.

Układy DMA są przeznaczone do bardzo szybkiego transferu danych pomiędzy modułami peryferyjnymi a pamięcią oraz pomiędzy różnymi adresami pamięci bez udziału CPU. Układy DMA udostępniają 14 niezależnych kanałów z własnym sprzętowym sygnałem żądania obsługi oraz przerwaniem i znacznikami stanu. Stosowane są priorytety (4 poziomy) oraz ich szeregowanie. Liczba danych (do 65535) do odczytu i zapisu jest niezależnie programowana dla różnych danych (byte, half word, word) z możliwością emulacji pakowania i rozpakowania.

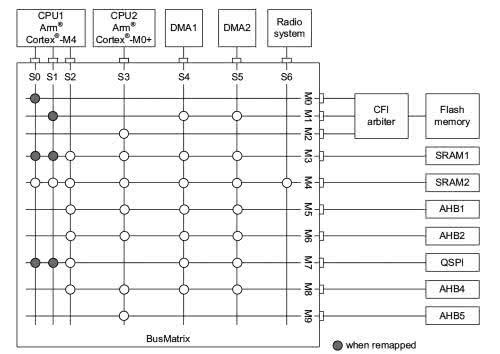

Układ scalony STM32WB55 jest zorganizowany wokół matrycy 32-bitowych magistral. Matryca zestawia połączenia pomiędzy modułami master oraz slave. Schemat takiej architektury jest pokazany na rysunku 4:

- Szyna S0 (I-bus) modułu procesora CPU1 jest używana przez rdzeń procesora do pobierania instrukcji. Typowo może być ona dołączona do pamięci SRAM1, SRAM2a, SRAM2b lub pamięci zewnętrznej poprzez łącze QUADSPI.

- Szyna S1 (D-bus) modułu procesora CPU1 jest używana do pobierania literałów oraz do debugowania.

- Szyna S2 (S-bus) modułu procesora CPU1 jest używana poprzez rdzeń procesora do transferu danych z pamięciami SRAM1, SRAM2a, SRAM2b, pamięci zewnętrznej poprzez łącze QUADSPI oraz układów peryferyjnych dołączonych do szyn AHB1, AHB4, APB1 i APB2.

- Szyna S3 (S-bus) modułu procesora CPU2 jest używana przez rdzeń procesora do pobierania instrukcji, do pobierania literałów oraz do transferu danych z pamięcią Flash, pamięciami SRAM oraz układów peryferyjnych.

- Szyny S4 oraz S5 modułów DMA są używane do transferu danych z pamięciami SRAM, pamięci zewnętrznej poprzez łącze QUADSPI oraz z układami peryferyjnymi.

- Szyna S6 modułu radiowego jest używana do transferu danych z pamięciami SRAM.

Dodatkowo są jeszcze dwa mostki pomiędzy szynami AHB i APB1 oraz AHB i ABP2. Tak zorganizowana architektura umożliwia jednoczesną (współbieżną) pracę wielu szybkich modułów.

Moduł radiowy

Moduł radiowy (Radio System) jest zbudowany z bloku radiowego i bloków obsługi standardu BLE 5 oraz IEEE 802.15.4. Moduł radiowy jest sterowany przez rdzeń CPU2, który obsługuje niskie warstwy stosu komunikacyjnego. Stos jest umieszczony w pamięci Flash, wspólnej z rdzeniem CPU1. Umożliwia to łatwą aktualizację oprogramowania komunikacyjnego.

Interfejs pomiędzy modułem radiowym i rdzeniem CPU2 używa systemu „mailbox message” sterownika IPC. Najważniejsze cechy modułu radiowego:

- Praca w paśmie 2,4 GHz (2405–2480 MHz).

- Zintegrowany balun.

- Dokładny pomiar RSSI.

- Programowana moc wyjściowa do +6 dBm z krokiem 1 dB.

- Możliwość współpracy z zewnętrznym wzmacniaczem.

- Obsługa pełnego protokołu Bluetooth BLE 5 z transferem 1 Mbps i 2 Mbps. Obsługuje jednoczesną pracę z wieloma rolami: central, peripheral, observer oraz broadcaster, oraz pracuje jako master/slave. Zapewnia wykonywanie w locie obsługi potwierdzania klucza z kodowaniem Elliptic Curve Diffie-Hellman (ECDH).

- Obsługa protokołu IEEE 802.15.4-2011. • Czułość odbiornika: –96 dBm (Bluetooth Low Energy 1 Mb/s), –100 dBm (IEEE 802.15.4).

- Pobór mocy: RX 3,8 mA, TX (0 dBm) 5,5 mA.

Zegary

System generowania i dystrybucji sygnałów zegarowych układu scalonego STM32WB55 jest bardzo rozbudowany. Zegar systemowy (SYSCLK) układu scalonego STM32WB55 może pochodzić z czterech źródeł:

- HSI16 (high speed internal): wewnętrzny oscylator RC wysokiej dokładności, 16 MHz. Może być trymowany programowo.

- MSI (multispeed internal): wewnętrzny oscylator RC niskiej mocy, może generować 12 częstotliwości od 100 kHz do 48 MHz. M oże być t rymowany s przętowo przy u życiu zegara LSE do dokładności ±0,25%.

- HSE: oscylator wysokiej jakości z zewnętrznym kwarcem 32 MHz, wymagany do pracy modułu radiowego.

- PLL: Może pracować do maksymalnej częstotliwości 64 MHz z sygnałami wejściowymi HSE, HSI16 lub MSI.

Układ scalony zawiera dwa układy PLL o nazwie: PLL oraz PLLSAI1. Każdy układ PLL pobiera taki sam sygnał wejściowy i generuje trzy niezależne sygnały wyjściowe.

Układ scalony zawiera Clock security system (CSS) włączany przez oprogramowanie. Jeśli wystąpi problem z sygnałem HSE, to źródło sygnału systemowego zostanie automatycznie przełączone na sygnał HSI16 i zostanie wygenerowane przerwanie. Problemy z sygnałem LSE też mogą być wykrywane.

Układ zawiera też dodatkowe źródła sygnału zegarowego:

- LSE: oscylator wysokiej dokładności z zewnętrznym kwarcem 32768 Hz. Jest przeznaczony dla układu RTC i używany do wybudzania z trybów Stop oraz Standby.

- LSI1: wewnętrzny oscylator RC niskiej mocy, 32 kHz (±5%). Jest przeznaczony dla zegara czasu rzeczywistego. Może być użyty przez watchdog oraz do wybudzania z trybów Stop oraz Standby (bez modułu radiowego)

- LSI2: wewnętrzny oscylator RC niskiej mocy i wysokiej stabilności, 32 kHz (±500 ppm). Jest używany przez moduł radiowy. Może być użyty przez watchdog oraz do wybudzania z trybów Stop oraz Standby.

- HSI48: wewnętrzny oscylator RC 48 MHz (±1%). Jest używany przez sterownik USB oraz moduł True RNG.

Wiele układów peryferyjnych (RNG, SAI, USARTs, I2Cs, LPTimers, ADC) wykorzystuje własne sygnały zegarowe niezależne od zegara systemowego. Dwa układy PLL mogą generować sygnały zegarowe dla modułów ADC, RNG oraz SAI.

W celu optymalizacji poboru mocy każdy sygnał zegarowy, gdy nie jest potrzebny, może być indywidulanie wyłączany zarówno dla rdzenia jak i dla pamięci oraz dla poszczególnych układów peryferyjnych. Przełączanie źródła sygnału zegarowego może być wykonywane bezpiecznie podczas pracy. Do konfigurowania częstotliwości pracy szyn AHB i APB układ wyposażono w wiele programowanych preskalerów. Zegar MSI jest używany jako źródło zegara systemowego 4 MHz po restarcie.

Zarządzanie zasilaniem

Cechą charakterystyczną nowoczesnych układów scalonych do komunikacji radiowej jest bardzo rozbudowany układ zarzadzania zasilaniem oraz złożone drzewo sygnałów zegarowych.

Układ scalony STM32WB55xx wymaga napięcia zasilającego z zakresu 1,71…3,6 V. Napięcie VDD jest monitorowane przez układ Peripheral Voltage Monitoring (PVM). Wiele niezależnych napięć zasilania jest generowanych wewnętrznie (VDDSMPS, VFBSMPS, VDDA, VDDRF, VDDUSB, VLCD). Wbudowana przetwornica impulsowa obniżająca (SMPS step- -down converter) wysokiej wydajności pracuje w dwóch trybach:

- Bypas – bezpośrednio po restarcie oraz w trybach pracy układu scalonego: Stop1, Stop2 oraz Standby.

- SMPS – gdy napięcie VDD jest powyżej progu BORH.

Przetwornica dostarcza napięcia VFBSMPS=1,40…3,6 V, które jest zasilaniem głównym całego systemu oraz modułu radiowego. Do wytwarzania napięcia zasilania układów cyfrowych VCORE są stosowane dwa regulatory zasilania LDO: główny regulator (MR) lub regulator niskiej mocy (LPR). Osobne zasilanie VBAT=1,55…3,6 V jest stosowane do zasilania zegara RTC, oscylatora 32 kHz oraz rejestrów podtrzymania, gdy nie ma zasilania głównego VDD. Gdy napięcie VDD jest włączone, istnieje możliwość ładowania zewnętrznej baterii (akumulatora) dołączonego do zasilania VBAT.

STM32WB55xx ma zintegrowane układy power-on reset (POR), power-down reset (PDR) oraz brown-out reset (BOR).

Tryby pracy

Układ scalony STM32WB55xx może pracować w wielu trybach, zaczynając od trybu pracy normalnej (Run) oraz w wielu trybach obniżonego poboru mocy: Systemowy tryb pracy zależy od trybów pracy rdzenia CPU1, rdzenia CPU2 i modułu radiowego. Po wykonaniu operacji Reset układ STM32WB55xx pracuje w trybie Run. Rdzeń CPU1 jest w stanie CRUN. Wtedy układ STM32WB55xx pracuje jako system jednoprocesorowy. Rdzeń CPU1, poprzez bit rejestru, umożliwia wykonanie bootowania rdzenia CPU2. Układ STM32WB55xx może włączyć systemowy tryb pracy z obniżoną mocą zasilania tylko wtedy, gdy wszystkie trzy podsystemy mogą to także zrobić.

Systemowe tryb pracy:

- Run – po wyjściu ze stanu Reset układ pracuje w trybie Run.

- Low-power run (LP run) – praca normalna ze zredukowaną częstotliwością zegara do poziomu poniżej 2 MHz oraz z możliwością kluczowania zegara dla nieużywanych układów peryferyjnych dołączonych do szyn APB i AHB. Kod jest pobierany z pamięci SRAM lub pamięci Flash. Włączony jest regulator niskiej mocy (LPR).

- Sleep – zegar CPU1 jest wyłączony. Wszystkie układy peryferyjne mogą pracować i wybudzić CPU1, gdy zostanie zgłoszone przerwanie lub zdarzenie.

- Low-power sleep (LP sleep) – ten tryb można włączyć z trybu LP run mode. Rdzeń CPU1 jest wyłączony.

- Stop0 – podtrzymywana jest zawartość pamięci SRAM1, SRAM2 oraz wszystkich rejestrów. Wszystkie zegary w domenie zasilania VCORE są zatrzymane. Sygnał LSI i LSE jest generowany. W trybie Stop0 główny regulator zasilania jest włączony, co umożliwia szybkie wybudzanie, ale też większy pobór mocy. Niektóre układy peryferyjne mogą włączać zegar HSI16 do wykrywania warunków ich wybudzania. Dodatkowo może być włączony zegar RTC (Stop + RTC) lub wyłączony.

- Stop1 – układ pracuje tak jak w trybie Stop0, lecz zamiast głównego regulatora LDO pracuje regulator małej mocy.

- Stop2 – w trybie Stop2 jest dostępnych mniej układów peryferyjnych i źródeł wybudzania niż w trybie Stop1.

- Standby – domena z asilania VCORE j est w yłączona. D odatkowo może być włączone podtrzymywanie zawartości pamięci SRAM2 zasilanej z regulatora niskiej mocy (LPR). Mogą też być włączone zegar RTC (Standby + RTC) i zegar systemowy HSI16.

- Shutdown – domena zasilania VCORE j est w yłączona. W yłączone są wszystkie zegary domeny zasilania VCORE (MSI, HSI16, LSI i układ PLL). Sygnał LSE jest generowany. W tym trybie pracy wyłączone jest monitorowanie napięcia zasilania. Dodatkowo może być włączony zegar systemowy MSI (4 MHz).

Sterownik wyświetlacza LCD

Układy scalone STM32WB55xx zawierają sterownik monochromatycznego pasywnego wyświetlacza LCD mającego do 4 wejść wspólnych oraz do 44 segmentów. Daje to maksymalny rozmiar wyświetlania 176 (44×4) lub 320 (40×8) pikseli (w największej obudowie układu scalonego). Pamięć RAM danych LCD o rozmiarze 16×32b zawiera dane do wyświetlania. Dane sterowania i wyświetlania są podwójnie buforowane w wewnętrznej pamięci, co umożliwia ich aktualizowanie w dowolnym momencie bez utracenia integralności wyświetlanej zawartości. Możliwe jest migotanie pikselami (do 8 pikseli).

Zasilanie VLCD sterownika może być pobierane z zewnętrznego wyprowadzenia VLCD układu scalonego lub wytwarzane przez zintegrowany w sterowniku LCD przetwornik podwyższający do napięcia wyższego niż zasilanie główne VDD całego układu scalonego. Zegar LCDCLK jest pobierany z sygnału zegarowego RTCCLK generatora czasu rzeczywistego. Dlatego w trybach obniżonego poboru mocy sterownik LCD może być włączony lub wyłączony. Do obsługi wyświetlacza LCD jest przeznaczonych wiele wyprowadzeń układu scalonego. Niewykorzystane wyprowadzenia mogą być użyte do obsługi innych układów peryferyjnych lub jako GPIO.

Układy scalone STM32WB55xx zawierają sterownik Touch sensing controller (TSC) do obsługi panelu dotykowego w technologii pojemnościowej. Sterownik może obsłużyć do 21 kanałów, w tym do 7 jednocześnie. Firma dostarcza darmowe biblioteki STM Touch, które umożliwiają implementowanie niezawodnej obsługi panelu dotykowego.

Bezpieczeństwo

Omawianie zagadnień bezpieczeństwa jest trudne z powodu skomplikowanej natury zagadnienia oraz typowo zbyt skąpej i niedokładnej informacji.

Układ scalony STM32WB55xx zawiera bardzo wiele rozbudowanych mechanizmów sprzętowego wspomagania bezpieczeństwa. Już na poziomie komunikacji międzyrdzeniowej można zastosować sprzętowe mechanizmy wyłączności dostępu do pamięci Flash. Również można zastosować mechanizm zablokowania odczytu/zapisu wyróżnionego obszaru pamięci Flash dostępnej tylko do wykonywania kodu (PCROP).

Funkcjonalności wspomagające bezpieczeństwo:

- Dwa akceleratory AES (AES hardware accelerator) AES1 I AES2. Obsługują pracę z kluczami o długości 128 i 256 bitów z wieloma trybami pracy (ECB, CBC, CTR, GCM, GMAC, CCM) przy przetwarzaniu bloków danych 128 b i obsłudze algorytmów takich jak: RSA, Diffie-Helman, ECC over GF(p). Zawierają długie rejestry do przechowywania klucza (256 b), wektora inicjalizacji (128 b) oraz danych (32 b). Wykonują automatyczną obsługę transferu DMA na szynie AHB z osobnymi kanałami wejścia i wyjścia. Akceleratory są obsługiwane przez firmową bibliotekę kryptograficzną STM32.

- Jednostka wyliczania CRC (Cyclic Redundancy Check) dla słów 8-, 16- i 32-bitowych.

- Generator „dokładnej” liczby pseudolosowej (RNG) dostarczający ciągły strumień próbek 32-bitowych generowanych na podstawie szumu analogowego.

- Akcelerator klucza publicznego PKA (Public Key Accelerator) zapewnia wszystkie obliczenia potrzebne do obsługi klucza.

- Unikalne UID64 zapisane w pamięci Flash. Może być zastosowane do otrzymania adresów: 48-bit Device Address (EUI-48) dla komunikacji Bluetoooth Low Energy oraz 64-bit Device Address (EUI-64) dla komunikacji IEEE 802.15.4.

- Unikalny identyfikator (ID) każdego egzemplarza układu scalonego (96 b) programowany w procesie produkcji. Dostępny tylko do odczytu bez możliwości zmiany. Może być zastosowany jako: numer seryjny (np. do transmisji USB), do generowania klucza, do uwierzytelniania bezpiecznego bootowania.

- Obsługa szyfrowania komunikacji w standardach Bluetooth Low Energy and IEEE 802.15.4, także z bezpieczną aktualizacją kodu Secure Firmware Installation (SFI).

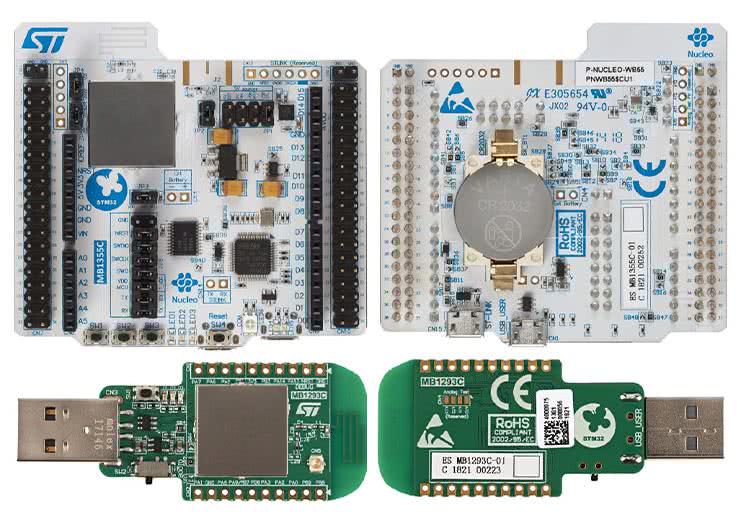

Zestaw uruchomieniowy P-NUCLEO-WB55

Zestaw uruchomieniowy P-NUCLEO-WB55 składa się z dwóch modułów sprzętowych: płytki „Nucleo-68” (MB1355C) oraz wtyczki USB “USB dongle” (MB1293C).

Płytka „Nucleo-68” (MB1355C)

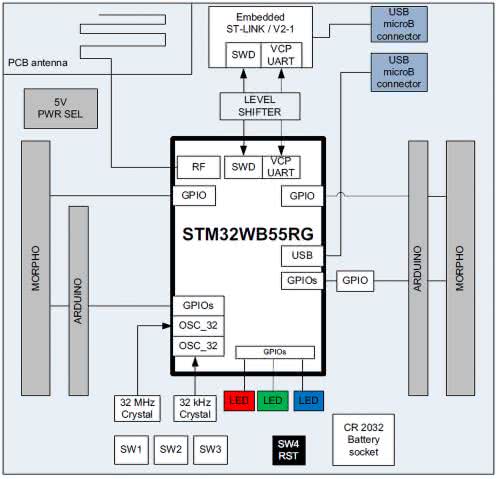

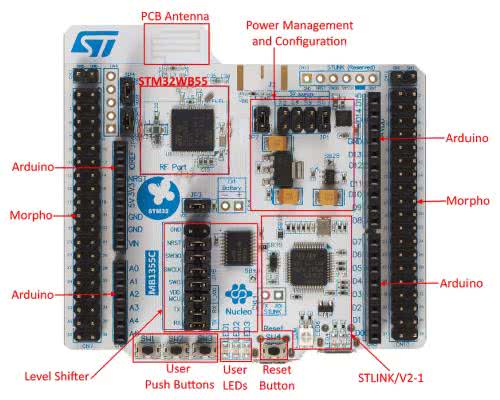

Schemat blokowy płytki „Nucleo-68”jest pokazany na rysunku 5. Rozmieszczenie głównych elementów na płytce drukowanej jest pokazane na rysunku 6. Widok dolnej strony płytki drukowanej jest na rysunku w nagłówku artykułu. Na płytce drukowanej można wyróżnić kilka obszarów.

Obszar procesora. Układ scalony STM32WB55RG ( U1, obudowa VFQFNP68) z kwarcem X2 (32768 Hz, generator LSE układu STM32WB55), z elementami układu zasilania (L1, C23, C24, C29 itd.) oraz elementami dopasowania wyjścia RF1 (C1, C2, L5) z filtrem FLT1 są umieszczone pod metalowym ekranem o wymiarach 17,2 mm×17,2 mm×3 mm. Pod tym samym ekranem są również umieszczone elementy dołączone do wewnętrznego konwertera SMPS: L1, C29, C23, C24. Drugi kwarc X1 (32 MHz, generator HSE układu STM32WB55) jest umieszczony w tym obszarze na odwrotnej stronie płytki drukowanej.

Wyjściowy sygnał radiowy jest, po filtrze FLT1, podawany na dwa kondensatory pełniące funkcję klucza wyboru. Zamontowany kondensator C35 doprowadza sygnał do układu dopasowania (L3, C36, C37) a następnie do anteny wykonanej na płytce drukowanej. Można też zamontować elementy drugiej ścieżki sygnałowej: C38, dopasowanie (L4, C39, C40) oraz gniazdko SMA (J2). Do tego gniazdka można dołączyć antenę 50 V lub urządzenie (pomiarowe) z dopasowaniem.

Obszar zarządzania mocą. Płytka „Nucleo-68” jest przystosowana do zasilania z różnych źródeł napięcia:

- Napięcie 5V_ST_LINK pobierane z gniazdka micro USB CN15 („ST-LINK”), domyślna konfiguracja. Napięcie jest pobierane z gniazdka micro USB i podawane na scalony przełącznik mocy STMPS2141STR (U4) z ograniczaniem prądu do 500 mA. Jeśli enumeracja łącza USB debuggera ST-LINK zostanie zakończona sukcesem, to jego procesor STM32F- 103CBT6 (U8) wystawi sygnał PWR_ENn włączenia klucza. Podczas enumeracji komputer dostarcza tylko 100 mA prądu. Jeśli komputer nie może dostarczyć prądu 500 mA, to klucz mocy nie zostanie włączony i dioda LED5 nie świeci. Wtedy trzeba do zasilania płytki zastosować zewnętrzny zasilacz.

- Napięcie 5V_USB_MCU pobierane z gniazdka micro USB CN1 (USER).

- Napięcie 5V_EXT pobierane ze złącza ST-Morpho (CN7.6).

- Napięcie VIN (7 do 12 V) pobierane ze złącza Arduino (CN6.8), ze złącza ST-Morpho (CN7.24) lub z gniazdka CN4. Napięcie to jest podawane na regulator LD1117S50TR (U2), który dostarcza napięcia 5 V (do 1000 mA).

- Bateria CR2032, w gniazdku SK-BT1 zamontowanym na płytce drukowanej. Może również dostarczać napięcia VBAT dla układu scalonego TM32WB55xx.

Wszystkie napięcia 5 V są dołączone do złącza JP1, gdzie zworą można wybrać odpowiednie źródło. Obecność napięcia 5 V na wyjściu złącza JP1 jest sygnalizowana przez diodę LED5. Następnie napięcie 5 V jest podawane na regulator LD39050PU33R (U3), który dostarcza głównego napięcia VDD (500 mA) o poziomie 3,3 V. Napięcie pobierane z baterii jest podawane z pominięciem regulatora U3.

Do konfigurowania źródeł zasilania służy również kilka lutowanych zwor SBxx.

Jeśli pobór prądu płytki (z dołączonymi płytkami rozszerzeń) dla napięcia 5 V przekracza 500 mA, to zalecane jest zasilanie płytki z napięcia VIN lub 5V_EXT. Gdy płytka „Nucleo-68” jest zasilana ze źródeł 5V_USB_MCU, 5V_EXT lub VIN, to może dostarczać napięć zasilania dla płytek rozszerzeń Arduino: 5 V (CN6.5 i CN7.18) oraz 3,3 V (CN6.4 i CN7.16). Należy pamiętać, że dostarczany prąd ma ograniczenie 500 mA. Zwora JP2 na napięciu VDD umożliwia pomiar poboru prądu płytki. Zwora JP3 na napięciu VDD_MCU umożliwia pomiar poboru prądu zasilania układu scalonego STM32WB55RG.

Obszar debuggera/programatora. N a płytce „ Nucleo-68” jest umieszczony debugger/programotor typu ST-LINK/V2-1 z procesorem STM32F103CBT6 (U8). Obsługuje on port micro USB (CN15, „ST- -LINK”), z którego pobiera napięcie zasilania 5V_ST_LINK. Jest ono podawane na regulator LD3985M33R (U5), który dostarcza napięcia zasilania debuggera 3V3_STLINK (150 mA) o poziomie 3,3 V. Debugger poprzez port USB udostępnia dla komputera wirtualny port COM (dołączony do portu LPUART lub USART procesora STM32WB55), port debugowy oraz pamięć masową. Jest też możliwość reenumeracji.

Przyciski. Na płytce „Nucleo-68” są umieszczone cztery przyciski. Kiedy są wciśnięte, wymuszają niski poziom logiczny. W przeciwnym przypadku jest poziom wysoki.

- SW4 („RESET”) – dołączony do wejścia NRST procesora STM32WB55RG oraz do masy.

- SW1 dołączony poprzez zworę SB47 do wejścia PC4 procesora. Może być zastosowany do wybudzania procesora (Wake-Up). Należy wtedy rozłączyć zworę SB47 i założyć zworę SB48, co spowoduje dołączenie przycisku do wejścia PC13 procesora.

- SW2 dołączony do wejścia PD0 procesora oraz do masy.

- SW3 dołączony do wejścia PD1 procesora oraz do masy.

Diody LED. N a płytce „ Nucleo-68” zamontowano następujące diody LED:

- LED1 (niebieska) dołączona do wyprowadzenia PB5 procesora STM32WB55RG oraz do masy.

- LED2 (zielona) dołączona do wyprowadzenia PB0 procesora oraz do masy.

- LED3 (czerwona) dołączona do wyprowadzenia PB1 procesora oraz do masy.

- LED4 (czerwona) dołączona do wyjścia /FOULT przełącznika mocy STMPS2141STR (U4). Świeci, kiedy zostanie aktywowane ograniczanie prądu do 500 mA.

- LED5 (czerwona) świeci, gdy jest napięcie 5 V na wyjściu złącza JP1.

- LED6 (czerwona + zielona) dołączona do wyprowadzenia PA9 procesora STM32F103CBT6 (U8) układu debugger/programotor typu ST-LINK/V2-1. Dioda LED6 sygnalizuje stan komunikacji USB pomiędzy komputerem a debuggerem:

- Wolne miganie na czerwono – po włączeniu zasilania, przed inicjalizacją USB.

- Szybkie miganie na czerwono – po pierwszej komunikacji pomiędzy PC i debuggerem.

- Ciągłe świecenie na czerwono – po pomyślnym zakończeniu inicjalizacji.

- Ciągłe świecenie na zielono – po pomyślnym zakończeniu inicjalizacji komunikacji dla danych.

- Miganie na czerwono i zielono – podczas komunikacji dla danych.

- Ciągłe świecenie na zielono – po pomyślnym zakończeniu komunikacji dla danych.

- Ciągłe świecenie na czerwono – błąd komunikacji.

Złącza rozszerzeń. Na zewnętrznych krawędziach płytki drukowanej są zamontowane złącza CN7 i CN10 standardu ST-Morpho. Udostępniają one większość wyprowadzeń procesora STM32WB55RG oraz masę i zasilania. Po wewnętrznej stronie tych złączy są zamieszczone na płytce drukowanej złącza CN5, CN6, CN8 i CN9 standardu Arduino Uno V3. Gniazdko micro USB (CN15, „ST-LINK”) jest przeznaczone na obsługę debuggera i doprowadzenie zasilania. Gniazdko micro USB (CN1, „USB-USER”) jest dołączone do wyprowadzeń PA11 oraz PA12 procesora i jest przeznaczone na obsługę połączenia użytkownika. Na dole płytki drukowanej jest umieszczone gniazdko dla baterii CR2032.

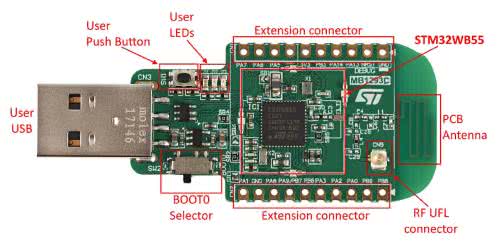

Wtyczka „USB dongle” (MB1293C)

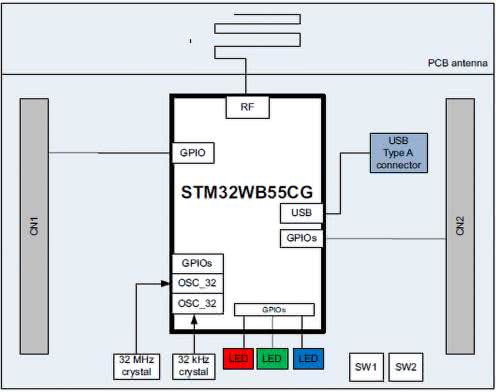

Drugim elementem w zestawie uruchomieniowym P-NUCLEO-WB55 jest wtyczka „USB dongle”. Schemat blokowy wtyczki „USB dongle” pokazano na rysunku 7, a rozmieszczenie głównych elementów na płytce na rysunku 8.

Na płytce drukowanej jest umieszczony układ scalony STM32WB55CG (U1, obudowa UFQFPN48) z kwarcem X2 (32768 Hz, generator LSE układu STM32WB55), kwarc X1 (32 MHz, generator HSE układu STM32WB55), elementy układu zasilania (L2, C9, C10, itd.) oraz elementy dopasowania wyjścia RF1 (C3, C30, L6) z filtrem FLT1. Wszystko pod metalowym ekranem o wymiarach 17,2 mm×17,2 mm×3 mm. Wyjściowy sygnał radiowy jest po filtrze FLT1 podawany na dwa kondensatory pełniące funkcję klucza wyboru. Zamontowany kondensator C4 doprowadza sygnał do układu dopasowania (L1, C6, C7), a następnie do anteny wykonanej na płytce drukowanej. Można też zamontować elementy drugiej ścieżki sygnałowej: C8, dopasowanie (L4, C28, C29) dołączonej do gniazdka UFL (CN5, zamontowane). Do tego gniazdka można dołączyć antenę 50 V lub urządzenie z dopasowaniem.

Na wtyczce „USB dongle” jest zamontowany wtyk USB-A (CN3, „USB-USER”) dołączony do wyprowadzeń PA11 oraz PA12 procesora. Napięcie 5V_USB_MCU jest pobierane z wtyku USB (CN3). Następnie napięcie 5 V jest podawane na regulator LD3985M33R (U3), który dostarcza głównego napięcia 3V3 (150 mA) o poziomie 3,3 V.

Na wtyczce „USB dongle” są umieszczone dwa elementy interfejsu:

- Przycisk SW1 – dołączony do wejścia PA10 procesora oraz do masy. Kiedy jest wciśnięty, wymusza niski poziom logiczny. W przeciwnym przypadku na wejściu jest poziom wysoki.

- Przełącznik SW2 (BOOT) – dołączony do wejścia BOOT0 procesora. Ma dwie pozycje „BOOT1” (z dołączeniem do zasilania 3V3) oraz „BOOT0” (pozycja domyślna, od strony wtyku USB).

Diody LED:

- D1 (niebieska) dołączona do wyprowadzenia PA4 procesora STM32WB55CG oraz do masy.

- D2 (zielona) dołączona do wyprowadzenia PB0 procesora oraz do masy.

- D3 (czerwona) dołączona do wyprowadzenia PB1 procesora oraz do masy.

Po obu stronach płytki drukowanej są zamieszczone pola lutownicze do zamocowania standardowych listew R=2,54 mm (po 10 pinów). Na nich są dostępne wyprowadzenia procesora, zasilanie i masa.

Podsumowanie

Układ scalony STM32WB55 na tle innych układów SoC z obsługą standardu BLE 5 prezentuje się bardzo dobrze [1]. Gdyby ten układ ukazał się na rynku rok temu (jak pierwotnie planowano), to byłby jednym z niewielu układów z pełną obsługą standardu BLE5 oraz obsługą wielu protokołów komunikacyjnych. Dzisiaj jest jednym z wielu.

A jednak dalej zaciekawia swoim olbrzymim potencjałem. W odniesieniu sukcesu u użytkowników mogą zadecydować własności funkcjonalne dostarczane przez oprogramowanie firmowe oraz sprawnie przeprowadzone działania edukacyjne. Pierwszy krok w postaci warsztatów jest już realizowany. Czekamy na kolejne.

Henryk A. Kowalski

Instytut Informatyki

Politechnika Warszawska

Literatura:

- Układy scalone z obsługą Bluetooth 5, Henryk A. Kowalski, EP 5/2018

- STM32WB Series, ST Microelectronics, http://bit.ly/2EvsXiZ

- STM32WB55VG, ST Microelectronics, http://bit.ly/2NnX7aH

- Device Errata, ES0394, STM32WB55Cx STM32WB55Rx STM32WB55Vx, Ver.4.0, February 2019, ST Microelectronics, http://bit.ly/2tJmWce

- Data Sheet, DS11929: Multiprotocol wireless 32-bit MCU Arm-based Cortex-M4 with FPU, Bluetooth Low Energy and 802.15.4 radio solution, Ver.4, February 2019, ST Microelectronics, http://bit.ly/2T1uWo9

- New STM32WB Series MCU with built-in BLE 5 and IEEE 802.15.4, Ver.1, Presentation, ST Microelectronics, http://bit.ly/2Euv3PW

- STM32WB Wireless Series with BLE 5.0 & IEEE 802.15.4, Ver.18.02, Flayer, ST Microelectronics, http://bit.ly/2VhDe7P

- STM32WB55xx advanced Arm-based 32-bit MCUs, Reference manual, RM0434 Rev 2, April 2018, ST Microelectronics

- Bluetooth Low Energy and 802.15.4 Nucleo pack based on STM32WB Series microcontrollers, User manual, UM2435 Rev 1, September 2018, ST Microelectronics

- STM32WB hands-on workshop, 15 January – 4 April 2019, ST Microelectronics, http://bit.ly/2tBFsDi

Zaloguj

Zaloguj