Podłączenie wejść

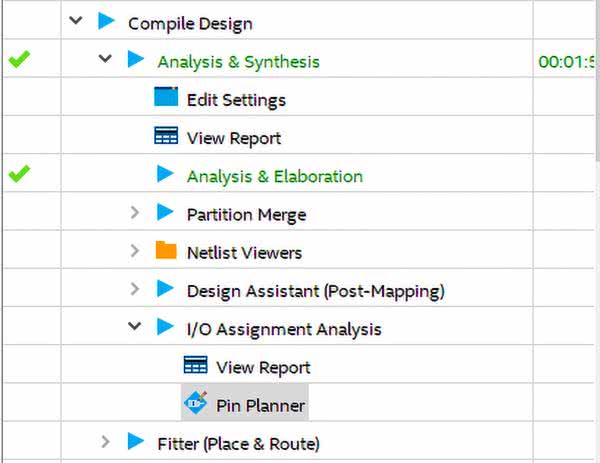

Po udanej syntezie możemy połączyć wejścia/wyjścia naszego modułu z pinami układu FPGA. W tym celu w znanym nam już panelu Tasks w głównym oknie programu Quartus rozwijamy opcję I/O Assignment Analysis (ang. analiza połączeń wejść/wyjść) i wybieramy opcję Pin Planner (ang. planowanie wyprowadzeń) (rysunek 21).

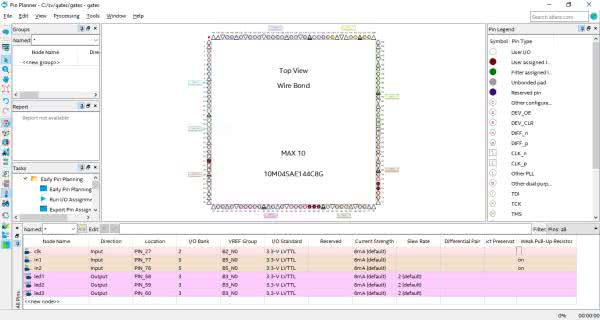

Pojawi się nowe okno (rysunek 22). W jego środkowej części widzimy rysunek prezentujący obudowę układu scalonego.

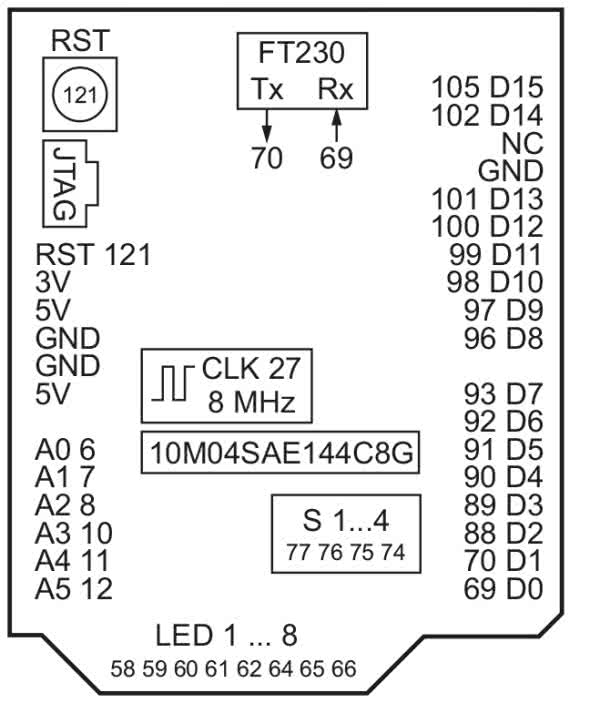

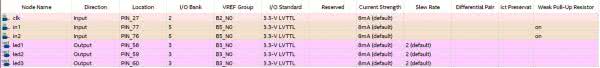

Dolny panel zawiera natomiast listę wejść i wyjść głównego modułu. Aby je połączyć po prostu chwytamy daną nazwę i przeciągamy ją na odpowiedni pin. Przy wykonywaniu połączeń przydatna będzie ściąga z opisem wyprowadzeń (rysunek 23). Kolejne złącza podłączamy zgodnie z tabelą 1.

| Złącze | Pin |

| clk | PIN_27 |

| in1 | PIN_77 |

| in2 | PIN_76 |

| led1 | PIN_58 |

| led2 | PIN_59 |

| led3 | PIN_60 |

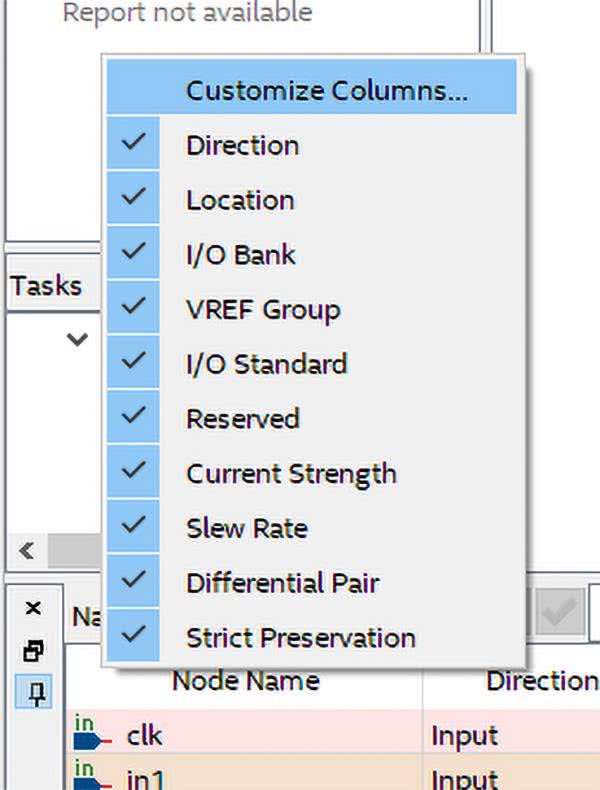

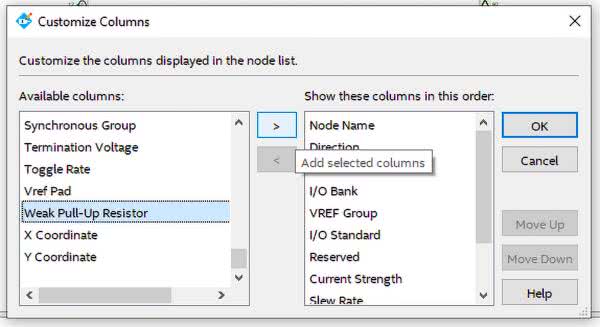

Musimy jeszcze skonfigurować podciąganie wejść przełączników do plusa zasilania. Niestety tej opcji nie ma w domyślnym widoku. Dlatego naciskamy nagłówek tablicy z pinami i wybieramy opcję Customize Columns… (ang. dostosuj kolumny), tak jak pokazuje rysunek 24. Pojawi się okno podobne do tego z rysunku 25. Na liście Available columns (ang. dostępne kolumny) klikamy opcję Weak Pull-Up Resistor (ang. opornik podciągający do plusa) i przenosimy ją do prawej listy klikając przycisk ze znakiem >. Zatwierdzamy klikając OK. Teraz dla pól in1 i in2 w nowej kolumnie wybieramy opcję on (ang. włączony). Następnie w polu I/O Standart (ang. standard wejścia/wyjścia) ustawiamy dla każdego złącza wartość 3.3-V LVTTL. Gotową konfigurację prezentuje rysunek 26. Konfiguracji pinów nie musimy zapisywać - dzieje się to automatycznie na bieżąco. Po prostu zamykamy okno programu Pin Plannera.

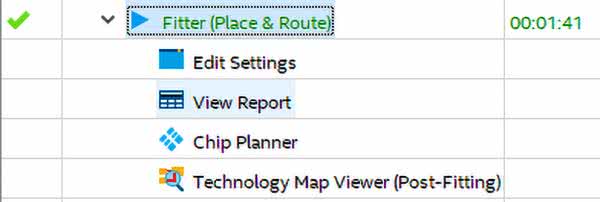

Fitter

Analiza i synteza przygotowały plan w jaki sposób za pomocą dostępnych zasobów zrealizować nasz model. Teraz do pracy może przystąpić Fitter (ang. instalator). Zadaniem tego narzędzia jest przyporządkowanie odpowiednich zasobów do konkretnych elementów (place - ang. rozmieszczanie) i skonfigurowanie połączeń pomiędzy nimi (route - ang. planowanie trasy).

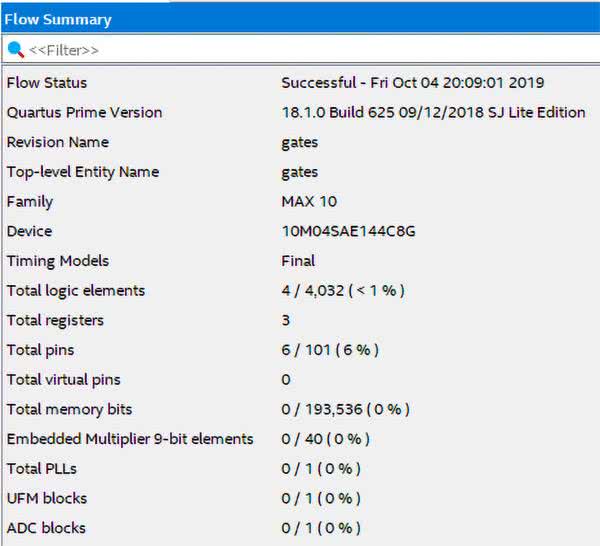

Uruchamiamy go dwukrotnie klikając w menu Tasks opcję Fitter. Jego działanie może chwilę potrwać, u mnie zajęło niecałe 2 minuty. Po jego zakończeniu w oknie Flow Summary pojawiły się już dokładne informację o zużytych zasobach. Jak widzimy na rysunku 27 nasz projekt korzysta z 4 (a nie jak wskazywała analiza z 3) z 4032 dostępnych elementów logicznych.

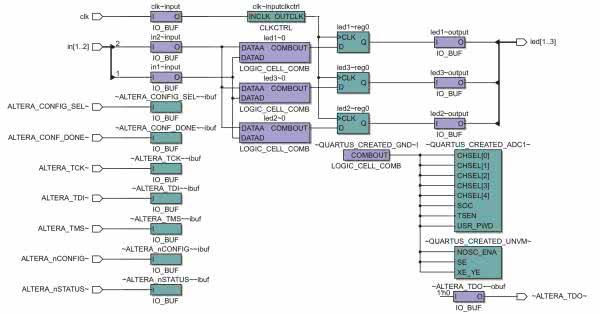

Rozwińmy teraz zakładkę Fitter w panelu Task (rysunek 28). Najpierw uruchomimy Technology Map Viewer (Post-Mapping). Zobaczymy wtedy okno podobne do tego z rysunku 29. Jest podobne do tego z rysunku 17, ale pojawiło się kilka nowych elementów. Nasz projekt, tak jak poprzednio zajmuje 3 tablice LUT i 3 przerzutniki. Doszła natomiast między innymi konfiguracja interfejsu JTAG, czy przetwornika ADC. To właśnie te elementy zużyły czwarty element logiczny.

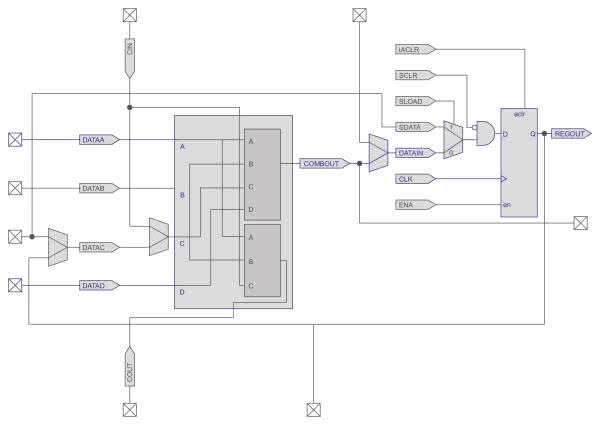

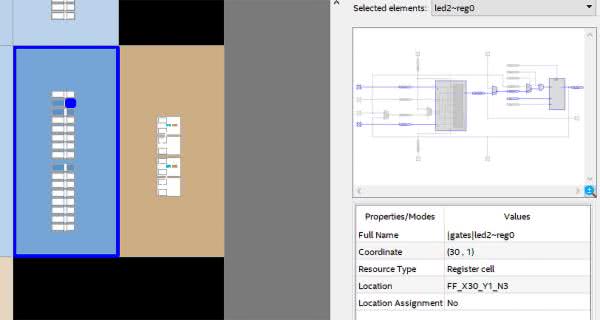

Tym razem poszczególnym elementom zostało już przyporządkowane konkretne miejsce w strukturze układu FPGA. Możemy się o tym przekonać otwierając znowu Resource Properity Editor (w ten sam sposób jak pokazany na rysunku 19). Zobaczymy, że zarówno tablica LUT, jak i przerzutnik pochodzą z tego samego elementu logicznego (rysunek 30).

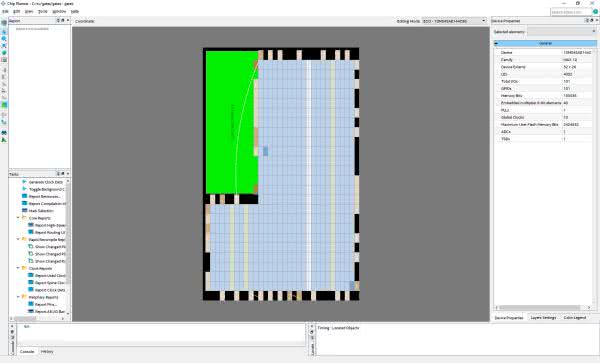

Jeszcze więcej możemy dowiedzieć się na temat wewnętrznej struktury układu z programu Chip Planner (ang. planowanie układu scalonego). Uruchamiamy go z panelu Tasks (rysunek 28).

Po uruchomieniu zobaczymy ekran podobny do tego z rysunku 31. Na środku widzimy schemat przedstawiający wnętrze układu FPGA. Po kliknięciu na kolejne elementy w panelu po prawej stronie pojawia się ich opis. Także kolory określają różne rodzaje bloków. Niebieski to LAB (ang. Logic Array Block - blok tablic logicznych). Składa się z 16 elementów logicznych oraz konfigurowalnych zasobów połączeniowych. Kolorem białym przedstawiono bloki DSP (digital signal processing - ang. cyfrowe przetwarzanie sygnałów), które zawierają tak zwaną mnożarkę - sprzętowy układ realizujący mnożenie. Kolor jasnozielony wskazuje natomiast na 9 kb bloki pamięci RAM. Różnego rodzaju zasobom zawartym w układzie FPGA będziemy przyglądać się w kolejnych częściach. Gdy za pomocą kółka myszy przybliżymy któryś z fragmentów zobaczymy jego schematyczny rysunek. Na przykład użyte przez nas elementy logiczne pokazuje rysunek 32. Gdy klikniemy któryś z elementów w panelu po prawej stronie zobaczymy jego opis.

Programujemy sprzęt

Przeszliśmy długą drogę od przygotowania modułu w języku SystemVerilog, poprzez symulację do jego zmapowania na zasoby (logiczne i połączeniowe) dostępne w naszym układzie FPGA. Teraz pozostało już wygenerowanie pliku konfiguracyjnego (tak zwany bitstream) i wgranie go do płytki.

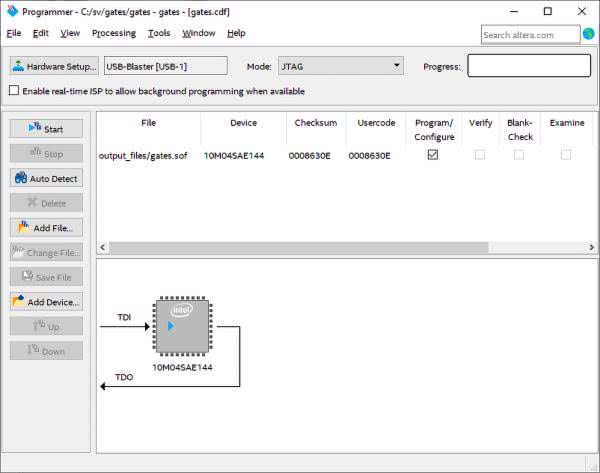

Aby go wygenerować w panelu Tasks uruchamiamy opcję Assembler (Generate programming files) (ang. generowanie plików konfiguracyjnych). Po jego zakończeniu uruchamiamy Program Device (Open Programmer) (ang. programuj urządzenie otwórz programator). Pojawi się okno podobne do tego z rysunku 33.

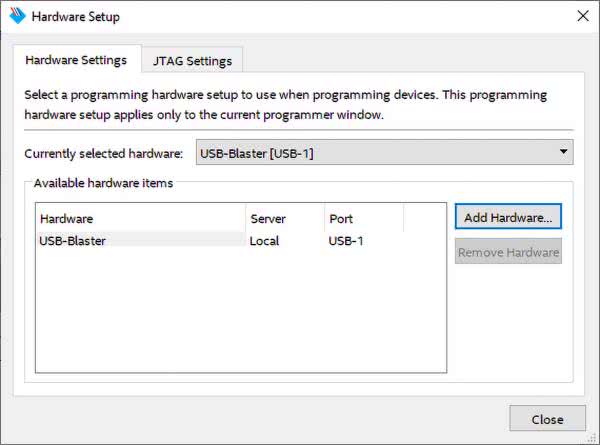

Następnie podłączamy programator USB Blaster oraz zasilanie do płytki. Gdy to zrobimy klikamy znajdujący się w prawym górnym rogu przycisk Hardware Setup… (ang. konfiguracja sprzętu). W kolejnym oknie (rysunek 34) wybieramy z listy Currently selected hardware (ang. obecnie wybrany sprzęt) nasz programator i zamykamy okno przyciskiem Close.

Teraz możemy rozpocząć programowanie klikając Start. Gdy się zakończy w prawym górnym rogu powinien pojawić się napis 100% (Successful). Teraz możemy sprawdzić działanie programu w sprzęcie. Zmieniamy położenie dwóch pierwszych suwaków i oglądamy zmiany stanu trzech pierwszych diod LED. Pozostałe 5 domyślnie są zaświecone.

W następnych odcinkach

Umiemy już stworzyć moduł i uruchomić go w układzie FPGA. W kolejnym odcinku uruchomimy kilka podstawowych układów logicznych takich jak rejestr przesuwny, czy licznik.

Rafał Kozik

rafkozik@gmail.com

Bibliografia:

[1] http://bit.ly/33Xec2e

[2] https://intel.ly/2DESKUJ

[3] https://intel.ly/2MC6TYp

[4] http://bit.ly/33uYPxs

Zaloguj

Zaloguj