W artykule opisano moduły rozszerzające funkcjonalność DSP1701A_DSP_MK2 o:

- DSP1701A_AD_PCM1809 – dwa liniowe wejścia analogowe (I²S),

- DSP1701A_ADCTDM_TAA5242 – cztery liniowe wejścia analogowe (TDM),

- DSP1701A_DACTDM_TAD5142 – cztery liniowe wyjścia analogowe (TDM),

- DSP1701A_SPDIF_IN_ASRC – moduł odbiornika SPDIF/Toslink z konwerterem częstotliwości próbkowania ASRC,

- DSP1701A_SPDIF_OUT_DIT4192 – moduł nadajnika SPDIF/Toslink,

- DSP1701A_ASRC4192 – moduł ASRC

- DSP1701A_TPA505x – moduł stereofonicznej, cyfrowej linii opóźniającej.

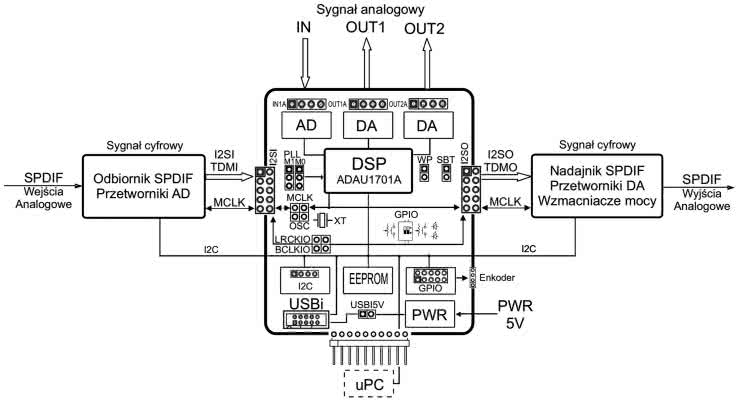

Schemat blokowy zestawu, ilustrujący przepływ sygnałów audio, sterujących oraz połączenia pomiędzy poszczególnymi modułami rozszerzeń, pokazano na rysunku 1.

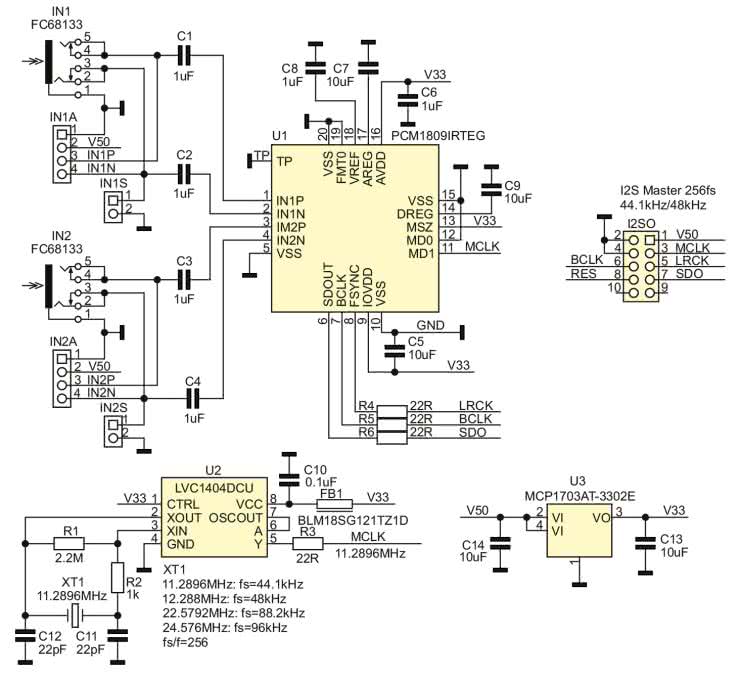

Podstawowym rozszerzeniem DSP1701A_DSP_MK2 jest uzupełnienie o dodatkowe dwa wejścia analogowe, oparte na przetworniku A/D typu PCM1809 (Texas Instruments). Schemat ideowy modułu DSP1701A_AD_PCM1809 zaprezentowano na rysunku 2.

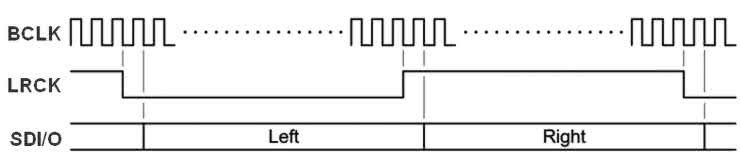

Przetwornik PCM1809 ma różnicowe wejścia analogowe o czułości (w trybie różnicowym) 2 Vrms (Zwe=10 kΩ). Linowy sygnał różnicowy (zbalansowany) doprowadzony jest do złączy IN1A/2A, na których dostępne jest także zasilanie 5 V oraz do gniazd mini jack 3,5 mm (zbalansowany mono). W przypadku obróbki sygnału niezbalansowanego konieczne jest założenie zwór IN1S/2S łączących z masą jedno z wejść różnicowych IN1N/2N przetwornika U1. Dane z przetwornika do procesora DSP przesyłane są magistralą I²S, której typowe przebiegi pokazano na rysunku 3. PCM1809 skonfigurowany jest sprzętowo do pracy w trybie master, czyli generuje sygnały zegarowe LRCK/BCLK dla procesora.

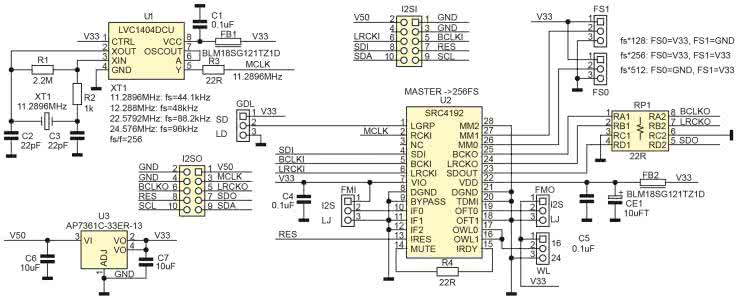

Aby zapewnić zgodność z pierwszą wersją płytki bazowej, moduł uzupełniony został o generator sygnału zegarowego MCLK oparty na układzie U2 typu LVC1404, który zawiera obwód oscylatora współpracującego z kwarcem oraz bramkę buforową. W zależności od użytej częstotliwości próbkowania należy zastosować kwarc XT1 o częstotliwości równej 256×fs, tj. 11,2896 MHz przy 44,1 kHz, a 12,288 MHz przy 48 kHz. Podobnie jak w przypadku płytki bazowej, polecam zastosowanie podstawki pod kwarc, ułatwiającej manipulację częstotliwościami fs podczas prototypowania. PCM1809 ma wbudowane filtry dolno- i górnoprzepustowe, zależne od częstotliwości fs. Filtr górnoprzepustowy, separujący m.in. składową stałą, ma częstotliwość odcięcia 0,00025×fs (12 Hz przy 48 kHz). Filtr dolnoprzepustowy (linowa faza) pracuje z częstotliwością 0,454×fs (około 21,8 kHz przy fs=48 kHz) i tłumieniem powyżej 70 dB. Należy zwrócić uwagę na częstotliwości odcięcia filtru górnoprzepustowego przy wyższych częstotliwościach próbkowania (88,2 kHz, 96 kHz), które wypadają w pasmie użytecznym audio i przy 96 kHz wynoszą 24 Hz. W zależności od zastosowania może być to pożądana cecha użytkowa (np. odcięcie najniższych częstotliwości w subwooferze) lub problem – gdy zależy nam na pełnym paśmie przenoszenia.

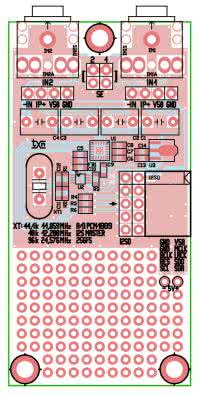

Układ zasilany jest napięciem 3,3 V z lokalnego stabilizatora U3. Moduł z płytką bazową połączony jest złączem I2SO i montowany z lewej strony płytki bazowej do złącza I2SI. Moduł nie wymaga uruchamiania, rozmieszczenie elementów na dwustronnej płytce drukowanej pokazano na rysunku 4, a zmontowany moduł na fotografii 1.

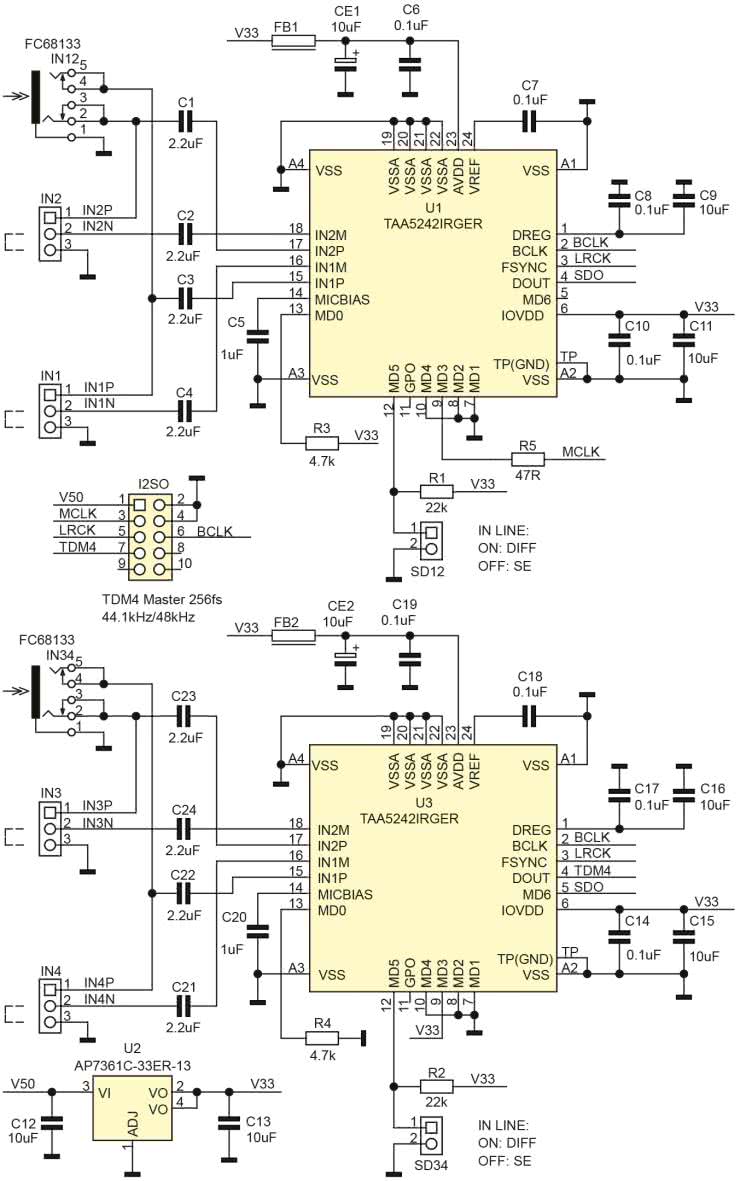

Gdy cztery wejścia analogowe to zbyt mało dla naszej aplikacji, należy użyć modułu DSP1701A_ADCTDM_TAA5242 z czterema wejściami liniowymi. Mamy wtedy do dyspozycji sumarycznie sześć wejść, co umożliwia już tworzenie prostych aplikacji miksujących sygnały z różnych źródeł. Moduł DSP1701A_ADCTDM_TAA5242, którego schemat ideowy pokazano na rysunku 5, używa do komunikacji z DSP interfejsu TDM4 (multipleksowanego czasowo), dzięki któremu dane z czterech przetworników wysłane są tylko jedną linią sygnałową.

Oszczędza to zasoby wyprowadzeń oraz – w przypadku naszego zestawu – upraszcza podłączenie.

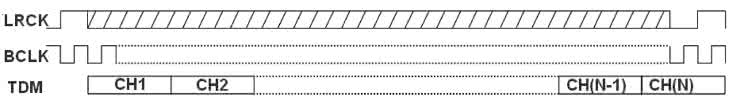

ADAU1701 zapewnia obsługę interfejsu slave TDM8 (do ośmiu kanałów audio), przyporządkowaną do interfejsu szeregowego dostępnego na wyprowadzeniu SDI0. Opisywany przetwornik wykorzystuje dwa układy przetworników TAA5242 z najnowszej linii A/D i D/A audio firmy Texas Instruments. Każdy z układów U1/U3 obsługuje dwa kanały przetwornika A/D. Konfigurację wejść określa się położeniem zwór SD12/34 podłączonych do wejść MD5 przetworników. Przy zwartej zworze (stan niski na MD5) przetworniki przełączają obwody wejściowe do współpracy z sygnałem różnicowym, a napięcie należy doprowadzić do złączy IN1...4. Rozwarta zwora ustala tryb niezbalansowany – w tej konfiguracji sygnał należy doprowadzić do gniazd IN12/34 (stereo) oraz założyć zwory pomiędzy wyprowadzenia 23 na opowiadających złączach IN1...4. Czułość wejść w trybie różnicowym wynosi 2 Vrms (Zwe=5 kΩ). Ustawienia trybu wejść są niezależne dla każdego przetwornika A/D. Za konfigurację trybu TDM odpowiada wyprowadzenie MD0. Zwarcie tej linii do masy poprzez rezystor 4,7 kΩ włącza tryb slave TDM układu (U3), a do szyny zasilania – tryb master TDM (U1). Moduł korzysta z sygnału zegarowego MCLK z płytki bazowej, taktującego przetwornik U1. Sygnały LRCK, BCLK są wspólne (generuje je master U1), a sygnał danych SDO z U1 doprowadzony jest do wejścia MD6 U3, które stanowi wejście kaskady TDM. Wyjściowy sygnał TDM4 dostępny jest natomiast na wyprowadzeniu SDO U2. Dane z układu master U1 zajmują 3 i 4 slot TDM, czyli są doklejane na końcu ramki TDM przez układ slave U3. Każdy kanał zajmuje 32 bity/64 cykle zegara BCLK. Przykładową ramkę TDM pokazano na rysunku 6.

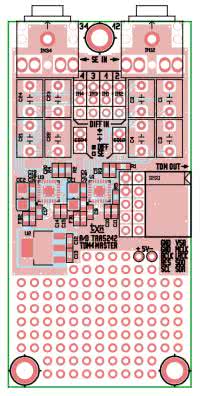

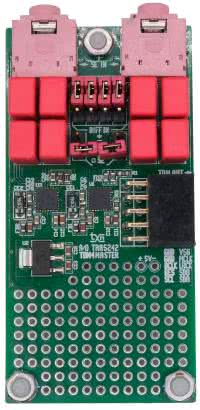

Pozostałe elementy zapewniają filtrację i odsprzęganie zasilania. Moduł zasilany jest napięciem 3,3 V z lokalnego stabilizatora LDO U2. Podobnie jak PCM1809, układ TAA5242 ma wbudowane filtry dolno- i górnoprzepustowe, zależne od częstotliwości fs. Filtr górnoprzepustowy (IIR), separujący m.in. składową stałą, ma częstotliwość odcięcia 1 Hz przy fs=48 kHz. Filtr dolnoprzepustowy o linowej charakterystyce fazowej pracuje z częstotliwością 0,454×fs (około 21,8 kHz przy 48 kHz) i tłumieniem powyżej 80 dB. Moduł z płytką bazową połączony jest złączem I2SO i montowany z lewej strony płytki bazowej do złącza I2SI. Moduł nie wymaga uruchamiania, rozmieszczenie elementów na czterowarstwowej płytce drukowanej pokazano na rysunku 7, a zmontowany moduł na fotografii 2.

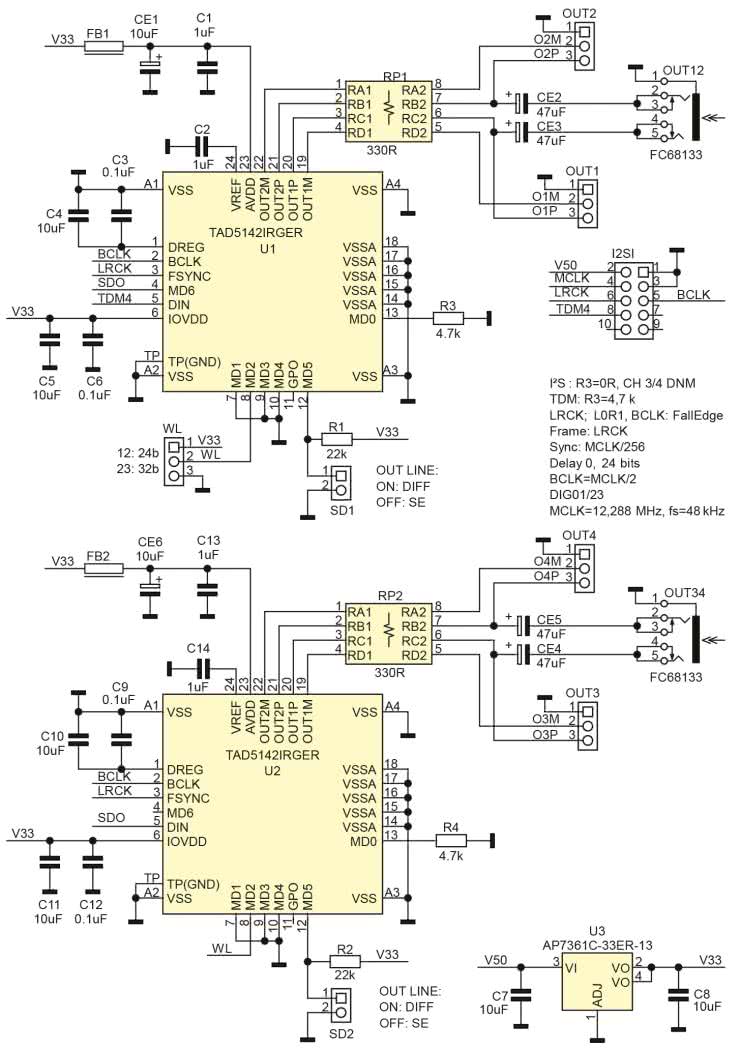

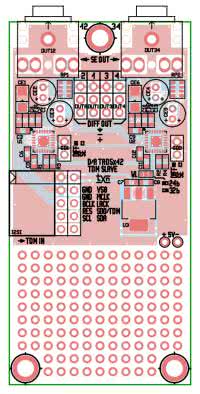

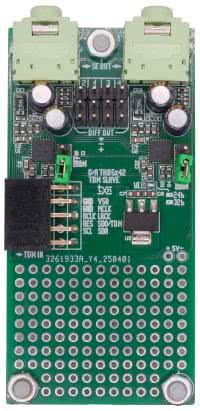

Ostatnim opracowanym modułem przeznaczonym do obróbki sygnału analogowego jest czterokanałowy przetwornik D/A, który – razem z czterema wyjściami zastawu DSP1701A_DSP_MK2 – daje możliwość realizacji m.in. aktywnych, trójdrożnych zestawów głośnikowych. Moduł używa dwóch przetworników TAD5142 lub TAD5242 (zgodny z tym pierwszym pod względem układu wyprowadzeń, ale mający nieco lepsze parametry audio od TAD5142) z najnowszej linii układów audio Texas Instruments. Schemat ideowy modułu pokazano na rysunku 8.

Każdy z układów U1, U2 obsługuje dwa kanały audio. Przetworniki oferują konfigurowalne stopnie wyjściowe z możliwością użycia trybu różnicowego (zbalansowanego) i niesymetrycznego (niezbalansowanego), wybieranego zworą SD1/2 (zwora zwarta – tryb różnicowy, zwora rozwarta – tryb niesymetryczny). W zależności od konfiguracji sygnał wyjściowy różnicowy dostępny jest na złączach OUT1...4, a niesymetryczny – na gniazdach OUT12/34 typu mini jack 3,5 mm stereo. Sygnał cyfrowy audio do przetworników, podobnie jak w przypadku modułu A/D, korzysta ze standardu TDM4, ale w trybie slave, tj. wszystkie sygnały zegarowe generowane są przez DSP. Układy U1, U2 pracują w trybie slave w kaskadzie TDM, która określona jest konfiguracją i wartością rezystorów R3, R4. Możliwy jest wybór długości słowa 24/32 bitów za pomocą zwory WL (domyślnie 32 bity, zwarte 2–3). Pozostałe elementy odsprzęgają zasilanie, lokalny stabilizator U3 dostarcza napięcie 3,3 V do zasilania przetworników. Jeżeli nie potrzebujemy wszystkich czterech kanałów, można zmontować przetwornik DA w wersji dwukanałowej, pomijając elementy kanału 3/4 i zwierając rezystor R3 zworą 0 Ω – konfiguruje to standardowy tryb I²S slave. Moduł z płytką bazową połączony jest złączem I2SI i montowany z prawej strony płytki bazowej do złącza I2SO. Moduł nie wymaga uruchamiania, rozmieszczenie elementów na czterowarstwowej płytce drukowanej pokazano na rysunku 9, a zmontowany moduł – na fotografii 3.

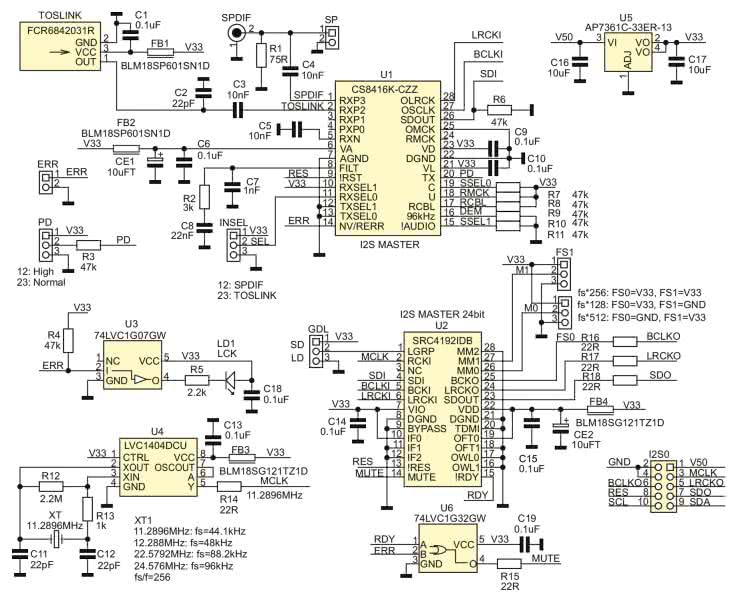

Procesor ADAU1701 nie ma wbudowanego odbiornika/nadajnika standardu SPDIF, powszechnie używanego do połączeń pomiędzy urządzeniami cyfrowego audio. Aby umożliwić obróbkę sygnału cyfrowego w standardzie przewodowym SPDIF lub optycznym (TOSLINK), opracowane zostały dwa moduły: odbiornika DSP1701A_SPDIF_IN_ASRC oraz nadajnika DSP1701A_SPDIF_OUT_DIT4192. Schemat tego pierwszego widać na rysunku 10.

Moduł bazuje na układzie scalonego odbiornika SPDIF – U1 typu CS8416K. Wbudowany w U1 multiplekser wejść umożliwia – za pomocą zwory INSEL – wybór pomiędzy wejściem cyfrowym SPDIF (gniazdo RCA) a odbiornikiem optycznym w standardzie TOSLINK (FCR684203R). Interfejs wyjściowy CS8416K skonfigurowany jest w tryb master I²S. Zwora PD określa konfigurację wbudowanego detektora fazy: w stanie niskim detektor (zwarte 2–3) odświeżany jest wolniej, zapewniając synchronizację i odtwarzanie generowanego przez CS8416K sygnału MCLK z fs z zakresu 32 kHz...108 kHz. Domyślnie zwora PD ustawia stan wysoki (zwarte 1–2), zapewniając szybką synchronizację detektora i współpracę z sygnałami do 192 kHz, a sygnał MCLK generowany przez CS8416K nie jest używany. U1 sygnalizuje poprawność odbieranych danych cyfrowych (synchronizację) sygnałem ERR, który używany jest do potwierdzenia odbioru danych diodą LCK (buforowaną przez U3). Sygnał ERR dostępny jest na złączu o tej samej nazwie i może zostać przykładowo zastosowany do wyciszania lub wprowadzenia współpracujących układów w tryb obniżonego poboru mocy, gdy nie są odbierane żadne dane. Dla zwiększenia funkcjonalności modułu wyposażony został w konwerter częstotliwości próbkowania (ASRC), bazujący na układzie U2 typu SRC4192 (lub zamiennie SRC4190, o nieco gorszych parametrach, ale z identycznym układem wyprowadzeń).

Interfejs wejściowy z sygnałami SDI, LRCKI, BCLKI, U2 pracuje w trybie slave, odbierając dane z odbiornika U1, a interfejs wyjściowy U2 z sygnałami SDO, LRCKO, BCLKO pracuje w trybie master, generując dane dla procesora DSP. Układ U2 wymaga zewnętrznego generatora sygnału zegarowego MCLK, w module zrealizowany jest on na układzie U4 typu LVC1404 – specjalizowanym generatorze współpracującym z kwarcem XT. Podobnie jak w przypadku pozostałych modułów, częstotliwość próbkowania fs zależna jest od wybranej częstotliwości kwarcu XT (domyślnie jest to kwarc 12,288 MHz przy fs=48 kHz). Sygnał MCLK doprowadzony jest także do procesora DSP, zapewniając synchroniczność z sygnałami danych cyfrowych. Zwory FS0,1 umożliwiają wybór krotności fs 128/256/512. Domyślnie przy współpracy z ADAU1701 ustawiana jest krotność 256 dla fs równej 48 kHz. Zwora GDL określa opóźnienie grupowe filtru ASRC, w położeniu 2–3 (stan wysoki) wybierane jest mniejsze opóźnienie (32 próbki), a w pozycji 1–2 (stan niski) większe (64 próbki). U2 ma obwód wyciszania MUTE, który aktywowany jest gdy układ ASRC nie jest gotowy do wystawiania przeliczonych danych lub gdy wystąpi błąd w odbiorniku. Sygnały RDY, ERR są sumowane za pomocą bramki U6, sterującej wyprowadzeniem MUTE. Stabilizator LDO U5 zapewnia zasilanie 3,3 V układu. Moduł połączony jest z płytką bazową złączem I2SO i montowany z lewej strony, do złącza I2SI. Układ nie wymaga uruchamiania, rozmieszczenie elementów na czterowarstwowej płytce drukowanej pokazano na rysunku 11, a zmontowany moduł – na fotografii 4.

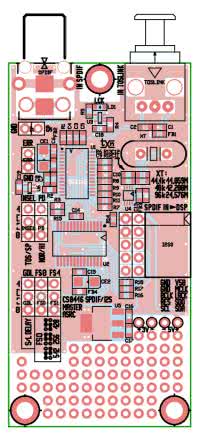

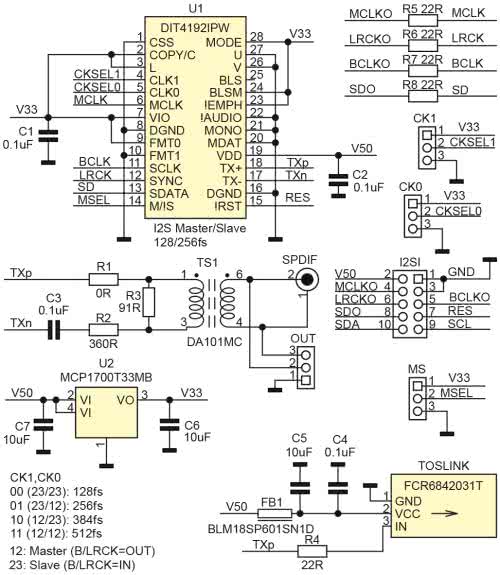

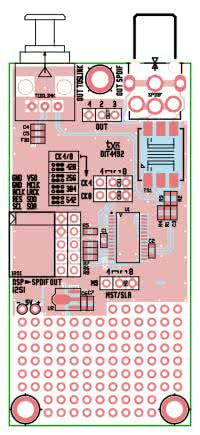

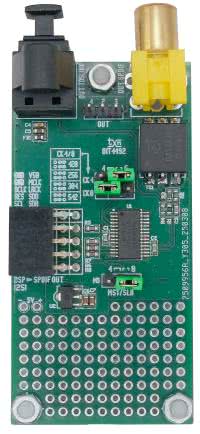

Schemat modułu nadajnika DSP1701A_SPDIF_OUT_DIT4192 pokazano na rysunku 12. Całość została oparta na układzie nadajnika SPDIF – U1 typu DIT4192. W zastosowanej konfiguracji konwertuje on dwukanałowy sygnał I²S do standardu SPDIF. Sygnał dostępny jest w dwóch standardach: przewodowym (po separacji galwanicznej transformatorem TS1) na gnieździe RCA SPDIF i złączu OUT oraz optycznym, dostępnym przez nadajnik TOSLINK typu FCR6842031T. Zwora MS konfiguruje tryb master/slave układu DIT4192, domyślnie zwarte piny 2–3 ustawiają tryb slave. Zwory CK0,1 określają krotność fs, domyślnie 256×fs (zwora CK1: zwarte 2–3, CK0: zwarte 1–2).

Stabilizator U2 dostarcza zasilanie 3,3 V do całego układu. Moduł połączony jest z płytką bazową złączem I2SI i montowany z jej prawej strony, do złącza I2SO. Moduł nie wymaga uruchamiania, rozmieszczenie elementów na czterowarstwowej płytce drukowanej pokazano na rysunku 13, a zmontowany moduł na fotografii 5.

Pochodną modułu odbiornika SPDIF jest wydzielony moduł konwertera częstotliwości próbkowania (ASRC) DSP1701A_ASRC4192, którego schemat pokazano na rysunku 14. Moduł jest niezbędny, gdy źródło sygnału stanowi urządzenie z interfejsem cyfrowym o częstotliwości fs zmiennej lub stałej, ale różnej od skonfigurowanej w procesorze DSP, np. przy współpracy z Raspberry Pi, modułami audio HDMI/I²S lub odbiornikami USB/I²S. Moduł umożliwia – oprócz zmiany krotności próbkowania zworami FS0/1, tak jak w odbiorniku SPDIF – dodatkową zmianę formatu odbieranych (zwora FMI) i wysyłanych danych (zwora FMO) do formatu I²S lub LJ (dane w ramce wyrównane do lewej). Ponadto istnieje możliwość ustalenia długości słowa na 16/24 bity zworą WL. Układ uzupełnia lokalny generator częstotliwości taktowania U1, współpracujący z kwarcem XT1 (zasady doboru częstotliwości są analogiczne do tych w opisanych wcześniej modułach). Port wejściowy ASRC pracuje w trybie slave, port wyjściowy w trybie master z ustalanym fs (zworami FS0/1). Napięcie zasilania 3,3 V dostarcza lokalny stabilizator LDO U3. Moduł połączony jest z płytką bazową złączem I2SO i montowany z jej lewej strony do złącza I²SI. Sygnały I²S/LJ z urządzenia zewnętrznego doprowadzone są do złącza szpilkowego I2SI. Na złącze I2SI wyprowadzone jest także zasilanie 5 V, które może służyć do zasilania współpracującego układu (po uwzględnieniu uwag o obciążalności szyny 5 V na płytce bazowej).

Moduł nie wymaga uruchamiania, rozmieszczenie elementów na dwustronnej płytce drukowanej pokazano na rysunku 15, a zmontowany moduł na fotografii 6.

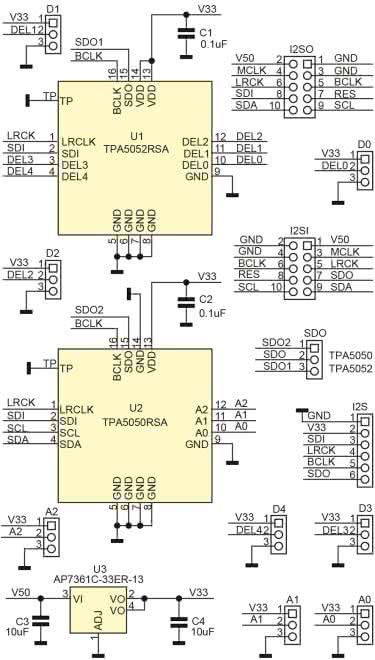

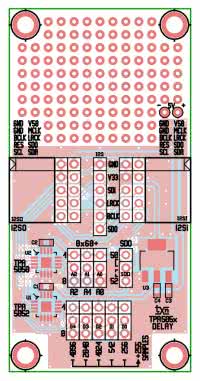

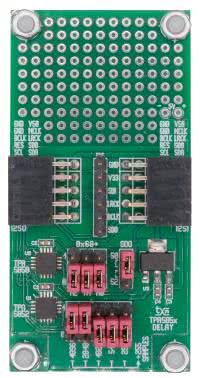

Ostatni z modułów rozszerzeń to blok cyfrowego opóźnienia sygnału. ADAU1701, ze względu na ograniczone zasoby, ma niewielkie możliwości opóźniania sygnału. W przypadku wykorzystania go do budowy efektów do instrumentów muzycznych, takich jak Delay, Echo lub zwrotnic sygnału, gdzie zależy nam na opóźnieniu sygnału, możliwe jest wykorzystanie zewnętrznej cyfrowej linii opóźniającej. Schemat modułu DSP1701A_TPA505x przedstawiono na rysunku 16.

W module zastosowano układy opóźnienia stosowane w odbiornikach TV do synchronizacji dźwięku z obrazem (tzw. Lip Sync Delay). Moduł przewiduje możliwość wlutowania dwóch typów układów o identycznym zakresie opóźnienia w obu kanałach (do 170 ms przy fs=48 kHz): TPA5052, którego czas opóźnienia ustalany jest sprzętowo zworami D0...D4 aż do 8191 próbek (z krokiem co 255 próbek) oraz TPA5050, którego czas opóźnienia konfigurowany jest programowo poprzez magistralę I²C. W przypadku TPA5050 zwory A0...2 umożliwiają ustalenie adresu magistrali 0x68...0x6F. Zwora SDO wybiera aktywny układ opóźnienia. Oba układy obsługują format I²S, dane wejściowe SDI po opóźnieniu dostępne są na wyprowadzeniu SDO. Do poprawnej pracy wymagane jest doprowadzenie sygnałów taktujących LRCK, BCLK oraz danych SDI poprzez złącze I2SO. Opóźnione dane SDO oraz niezmienione sygnały LRCK, BCLK dostępne są na złączu I²SI oraz I²S. Napięcie zasilania 3,3 V pochodzi z lokalnego stabilizatora LDO U3. Sposób podłączenia modułu zależy od aplikacji – trzeba zdecydować, czy mamy zamiar opóźniać dane przed, czy po obróbce (lub w pętli sprzężenia DSP). Narzuca to właściwą stronę, z której moduł łączony jest z płytką bazową.

Moduł nie wymaga uruchamiania, rozmieszczenie elementów na dwustronnej płytce drukowanej pokazano na rysunku 17 a zmontowany moduł – na fotografii 7. Jeżeli nie przewidujemy używania któregoś ze sposobów sterowania opóźnieniem, to odpowiednie elementy można pominąć przy montażu.

Praktyczny sposób korzystania z modułów opisany zostanie w jednym z kolejnych odcinków kursu.

Adam Tatuś, EP

- R1: 2,2 MΩ

- R2: 1 kΩ

- R3...R6: 22 Ω

- C1...C4: foliowy 1 μF (THT, R=5 mm, 7,2 × 5,0 mm)

- C5, C7, C9, C13, C14: 10 μF (SMD 0603, 10 V, X7R)

- C6, C8: 1 μF (SMD 0603, 10 V, X7R)

- C10: 0,1 μF (SMD 0603, 10 V, X7R)

- C11, C12: 22 pF (SMD 0603, 16 V, NP0)

- U1: PCM1809IRTEG (WQFN20_4x4P0.5)

- U2: SN74LVC1404DCUR (VSSOP8_050)

- U3: MCP1703AT-3302E (SOT-89)

- FB1: dławik ferrytowy BLM18SG121TZ1D (SMD 0603)

- I2SO: gniazdo kątowe 2×5 pin żeńskie (ZL263-10DG)

- IN1, IN2: gniazdo jack 3,5 mm stereo, czerwone (FC68133)

- IN1A, IN2A: złącze SIP 1×4 pin, proste, 2,54 mm

- IN1S, IN2S: złącze SIP 1×2 pin, proste, 2,54 mm

- XT1: kwarc HC49U niski 11,2896 MHz, dobrać odpowiednio do fs (patrz opis)

- R1, R2: 22 kΩ

- R3, R4: 4,7 kΩ

- R5: 47 Ω

- C1...C4, C21...C24: foliowy 2,2 μF (THT, R=5 mm, 7,2 × 5,0 mm)

- C5, C20: 1 μF (SMD 0603, 10 V, X7R)

- C6...C8, C10, C14, C17...C19: 0,1 μF (SMD 0603, 10 V, X7R)

- C9, C11...C13, C15, C16: 10 μF (SMD 0603, 10 V, X7R)

- CE1, CE2: tantalowy 10 μF (SMD A 3216, 10 V

- U1, U3: TAA5242IRGER (VQFN24_050RGE)

- U2: AP7361C-33ER-13 (SOT-223)

- FB1, FB2: dławik ferrytowy BLM18AG121SN1D (SMD 0603)

- I2SO: gniazdo kątowe 2×5 pin żeńskie (ZL263-10DG)

- IN1...IN4: złącze SIP 1×3 pin, proste, 2,54 mm

- IN12, IN34: gniazdo jack 3,5 mm stereo, czerwone (FC68133)

- SD12, SD34: złącze SIP 1×2 pin, proste, 2,54 mm

- R1, R2: 22 kΩ (SMD 0603, 1%)

- R3, R4: 4,7 kΩ (SMD 0603, 1%)

- RP1, RP2: drabinka 4×330 Ω (CRA06S08)

- C1, C2, C13, C14: 1 μF (SMD 0603, 10 V, X7R)

- C3, C6, C9, C12: 0,1 μF (SMD 0603, 10 V, X7R)

- C4, C5, C7, C8, C10, C11: 10 μF (SMD 0603, 10 V, X7R)

- CE1, CE6: tantalowy 10 μF (SMD A 3216, 10V)

- CE2...CE5: elektrolityczny 47 μF (THT R=5 mm, D=2 mm)

- U1, U2: TAD5124IRGER (VQFN24_050RGE)

- U3: AP7361C-33ER-13 (SOT-223)

- FB1, FB2: dławik ferrytowy BLM18AG121SN1D (SMD 0603)

- I2SI: gniazdo kątowe 2×5 pin żeńskie (ZL263-10DG)

- OUT1...OUT4: złącze SIP 1×3 pin, proste, 2,54 mm

- OUT12, OUT34: gniazdo Jack 3,5 mm stereo, zielone (FC68133)

- SD1, SD2: złącze SIP 1×2 pin, proste, 2,54 mm

- R1: 75 Ω

- R2: 3 kΩ

- R3, R4, R6...R11: 47 kΩ

- R5: 2,2 kΩ

- R12: 2,2 MΩ

- R13: 1 kΩ

- R14...R18: 22 Ω

- C1, C6, C9, C10, C13...C15, C18, C19: 0,1 μF (SMD 0603, 10 V, X7R)

- C2, C11, C12: 22 pF (SMD 0603, 16 V, NP0)

- C3...C5: 10 nF (SMD 0603, 10 V, X7R)

- C7: 1 nF (SMD 0603, 16 V, NP0)

- C8: 22 nF (SMD 0603, 10 V, X7R)

- C16, C17: 10 μF (SMD 0603, 10 V, X7R)

- CE1, CE2: tantalowy 10 μF (SMD A 3216, 10V)

- LD1: dioda LED (SMD 0603)

- U1: CS8416K-CZZ (TSSOP28L_065)

- U2: SRC4192IDB (SSOP28_065)

- U3, U6: 74LVC1G07GW.125 (TSSOP5)

- U4: SN74LVC1404DCUR (VSSOP8_050)

- U5: AP7361C-33ER-13 (SOT-223)

- ERR, SP: złącze SIP 1×2 pin, proste, 2,54 mm

- FB1, FB2: dławik ferrytowy BLM18SP601SN1D (SMD 0603)

- FB3, FB4: dławik ferrytowy BLM18SG121TZ1D (SMD 0603)

- FS0, FS1, GDL, INSEL, PD: złącze SIP 1×3 pin, proste, 2,54 mm

- I2S0: gniazdo kątowe 2×5 pin żeńskie (ZL263-10DG)

- SPDIF: gniazdo RCA do druku ekranowane (RCA_PCB_CC134/RCA-105K)

- TOSLINK: odbiornik Toslink (FCR6842031R)

- XT: kwarc 11,2896 MHz, HC49U niski, dobrać odpowiednio do fs (patrz opis)

- R1: 0 Ω

- R2: 360 Ω

- R3: 91 Ω

- R4...R8: 22 Ω

- C1...C4: 0,1 μF (X7R, 10 V)

- C5...C7: 10 μF (X7R, 10 V)

- U1: DIT4192IPW (TSSOP28_065)

- U2: MCP1700T-3302MB (SOT-89)

- CK0, CK1, MS, OUT: złącze SIP 1×3 pin, proste, 2,54 mm

- FB1: dławik ferrytowy BLM18SP601SN1D (SMD 0603)

- I2SI: gniazdo kątowe 2×5 pin żeńskie (ZL263-10DG)

- SPDIF: gniazdo RCA do druku, ekranowane (RCA_PCB_CC134/RCA-105K)

- TOSLINK: odbiornik TOSLINK (FCR6842031T)

- TS1: transformator DA101MC

- C1, C2: 0,1 μF (10 V, X7R)

- C3, C4: 10 μF (10 V, X7R)

- U1: TPA5052RSA (QFN16_065)

- U2: TPA5050RSA (QFN16_065) – opcjonalnie zamiast U1

- U3: AP7361C-33ER-13 (SOT-223)

- A0...A2, D0...D4, SDO: złącze SIP 1×3 pin, proste, 2,54 mm

- I2S: złącze SIP 1×6 pin, proste, 2,54 mm

- I2SO: gniazdo kątowe 2×5 pin żeńskie (ZL263-10DG)

- R1: 2,2 MΩ

- R2: 1 kΩ

- R3, R4: 22 Ω

- RP1: drabinka 4×22 Ω (CRA06S08)

- C1, C4, C5: 0,1 μF (SMD 0603, 10 V, X7R)

- C2, C3: 22 pF (SMD 0603, 10 V, NP0)

- C6, C7: 10 μF (SMD 0603, 10 V, X7R)

- CE1: tantalowy 10 μF (SMD B 3528)

- U1: SN74LVC1404DCUR (VSSOP8_050)

- U2: SRC4192 (SSOP28)

- U3: AP7361C-33ER-13 (SOT-223)

- FB1, FB2: dławik ferrytowy BLM18SG121TZ1D (SMD 0603)

- FMI, FMO, FS0, FS1, GDL, WL: złącze SIP 1×3 pin, proste, 2,54 mm

- I2SI: złącze kątowe 2×5 pin, męskie 2,54 mm (IDC10H)

- I2SO: gniazdo kątowe 2×5 pin, żeńskie 2,54 mm (ZL263-10DG)

- XT1: kwarc 11,2896 MHz, HC49U niski, dobrać odpowiednio do fs (patrz opis)

Zaloguj

Zaloguj