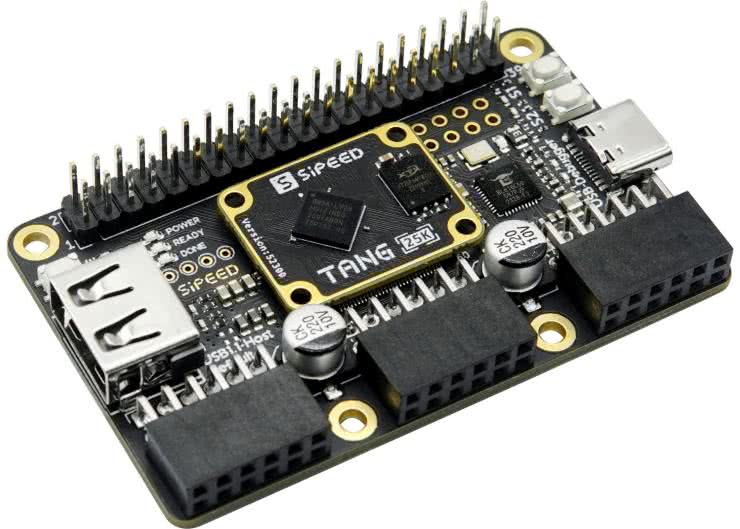

Firma Sipeed oferuje wiele różnych zestawów startowych i modułów, spośród których przyjrzymy się serii Tang zawierającej układy FPGA firmy Gowin (pełna nazwa: Guangdong Gowin Semiconductor Corporation). Skupimy się na zestawie Tang Primer 25k, który oferuje świetny stosunek możliwości do ceny. A ta ostatnia jest nawet kilka razy niższa od cen zestawów bardziej renomowanych marek. Nawet w rodzinie Tang zestaw Primer 25k plasuje się dość korzystnie pod względem specyfikacji i dlatego też może być on dobrym wyborem na początek przygody z FPGA.

Zakup, cena i specyfikacja

Sipeed Tang Primer 25k nie jest dostępny w polskich sklepach, za to bez problemu można go znaleźć na portalu AliExpress. Co więcej, Sipeed na swojej stronie Wiki zapewnia linki do większości oferowanych przez markę zestawów właśnie na tej platformie. Cena Tang Primer 25k wynosi 174,39 zł za cały zestaw oraz 122,99 zł za główny moduł (są to ceny obowiązujące w chwili pisania tego artykułu).

Zestaw składa się z płytki głównego modułu, zawierającej układ FPGA typu GW5A-LV25MG121, pamięć konfiguracji Flash 64 Mb oraz przetwornicę napięcia, a także płytki bazowej wyposażonej w debugger, złącza USB (jedno do podłączenia zewnętrznych urządzeń, drugie do programowania i zasilania), trzy złącza PMOD dla dodatkowych modułów oraz jedno złącze 2×20 pinów. Na płytce głównego modułu znajdują się dwa złącza męskie typu DF40C-60DP-0.4V(51) udostępniające 75 pinów IO, linie JTAG i MIPI oraz zasilanie (zarówno napięcie wejściowe, jak i wyjściowe przetwornicy). Sipeed dostarcza w dokumentacji informacje o dokładnych wymiarach płytki (22,9 mm × 17,8 mm) i rozstawie złączy (14 mm), dzięki czemu ten moduł można bezproblemowo zintegrować z własnymi projektami. Płytka bazowa ma złącza żeńskie typu DF40C-60DS-0.4V(51), a Sipeed dodaje w dokumentacji, iż są one dostępne w różnych wysokościach. Płytka modułu może być zasilana napięciem 3,6...5,5 V. Producent nie podaje w opisie dokładnej wartości poboru prądu, gdyż ten mocno zależy od stopnia wykorzystania układu FPGA Gowin GW5A-LV25MG121.

Macierz FPGA zawarta na płytce zawiera 23040 elementów logicznych (LUT4), tyle samo rejestrów (FF), a także 180 kilobitów pamięci SRAM rozdystrybuowanej w całym układzie oraz dodatkowe 1008 kilobitów pamięci SRAM w 56 blokach. Dokumentacja Sipeed podaje też, że układ jest wyposażony w 28 elementów DSP, ale nota Gowin podaje dokładniejszą informację: jest to bowiem 28 bloków... mnożenia 18-bit × 18-bit. Układ ma ponadto sześć pętli PLL, 16 globalnych zegarów i 16 zegarów w.cz. Prędkość transferu danych w standardzie LVDS, odbywającej się przez jeden z ośmiu banków IO, wynosi 1,25 Gbps, a oddzielne linie MIPI zapewniają aż 2,5 Gbps, oferując cztery linie Rx/Tx i jedną linię zegarową. Fotografia 1 prezentuje zbliżenie na zestaw od strony elementów (a) i druku (b), z oznaczeniami pinów układu FPGA gniazda rozszerzeń (użytkownika) i modułów.

Sipeed oferuje następujące moduły rozszerzeń do płytki bazowej:

- moduł z kontrolerami gier w standardzie SNES,

- moduł z matrycą LED 64×64,

- moduł kamery 5 Mpx (2592×1944 px),

- zestaw modułów z przyciskami, diodami, złączem kart SD, i złączem DVI,

- moduł pamięci SDRAM wpinany w złącze 2×20 pin (64 MB, 16-bit).

Moduły te nie są wymagane do pracy z zestawem, ale mogą być przydatne. Nic nie stoi na przeszkodzie, by wykorzystać także płytki innych producentów, podłączone za pomocą przewodów lub samodzielnie zaprojektowanych i wykonanych adapterów. Zestaw podstawowy dostarczony został w dedykowanym, plastikowym pudełku i poza samymi płytkami zawiera też krótki kabel USB-C.

Zestaw nie zawiera też żadnej dokumentacji papierowej, więc należy od razu sięgnąć po stronę Wiki Sipeed. Dokumentacja techniczna jest dość bogata i dobrze przetłumaczona na język angielski, podobnie jak dokumentacja firmy Gowin. Jedynym „zgrzytem” jest strona „Getting Started”, dostępna jedynie w języku chińskim, z opcją tłumaczenia przez Google. Zawiera głównie informacje o aktualizacji firmware debuggera. Przez Wiki można też pobrać wersję edukacyjną środowiska programistycznego Gowin EDA.

Gowin EDA i pierwsze kroki z zestawem Tang Primer 25

Instalacja środowiska nie nastręcza problemów. Po otwarciu programu dostajemy kilka opcji do wyboru, w tym dostęp do przykładowych projektów lub stworzenie nowego. Przy wyborze układu, na którym będziemy pracować, nie zauważono opcji wyszukiwania po rodzajach zestawu rozwojowego – a szkoda, bo niektóre środowiska preferują taką opcję. Bezproblemowo udało się jednak odnaleźć właściwy układ i stworzyć nowy projekt. Pewnym problemem jest wybór lokalizacji projektu – program nie akceptuje folderów, które zawierają spacje w nazwach, przy czym program informuje użytkownika jedynie o „niedozwolonych znakach w nazwie projektu”, co jest dość niejasnym komunikatem.

Kolejnym „zgrzytem” jest sam edytor, w którym nie można zmienić powiększenia (co jest standardem w wielu innych środowiskach programistycznych). Trudno wskazać konkretne przyczyny tego faktu, ale w odczuciu autora Gowin EDA sprawia wrażenie oprogramowania napisanego jeszcze w czasach, gdy wszyscy używali systemu Windows 95, albo nawet 3.11. W ustawieniach można zmienić zarówno wygląd całego programu (klasyczny lub ciemny), jak i edytora kodu. Zmiana na tryb ciemny nie modyfikuje wszystkich elementów, a ciemne wersje edytora nie są wybitnie użyteczne. Dlatego autor zdecydował się na domyślny wygląd programu i po prostu odwrócił wszystkie kolory systemowe, korzystając z funkcji ułatwień dostępu. Rozmiar czcionki też został zwiększony.

Dla osób, które nigdy wcześniej nie korzystały z układów FPGA ważne jest, by producent zestawu startowego dostarczał wraz z nim jakiś poradnik dla początkujących. Sipeed, jak wspomniano wcześniej, nie daje żadnego użytecznego poradnika dla początkujących. Hobbysta jest pozostawiony samemu sobie, z kilkoma odnośnikami do tutoriali nt. języka Verilog (a gdzie VHDL?). Doświadczony użytkownik sobie poradzi, ale cena zestawu i jego opis sugerują raczej przeznaczenie dla początkujących. Trudno nawet znaleźć informacje, do których pinów i banków podłączone są dwa przyciski na płytce bazowej (S1 do pinu H11, S2 do pinu H10). Jest to definitywnie duża wada tego zestawu. Jako przykład „Hello World” autor postanowił napisać rejestr przesuwny z liniowym sprzężeniem zwrotnym, który na wyjścia poda sygnał zegarowy i strumień bitów. Ten prosty kod wygenerowano z pomocą Gemini, a następnie ręcznie dopisano fragment dzielący częstotliwość zegara przez pięć, dzięki czemu ta wynosi 10 MHz. Listing 1 pokazuje ów kod. Nie jest on napisany zgodnie z dobrymi praktykami programowania, ale celem było wykonanie czegoś, co zadziała i pozwoli szybko zweryfikować poprawność działania całego zestawu.

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity lfsr_16bit is

port (

clk : in std_logic;

reset_p : in std_logic;

enable : in std_logic;

lfsr_out : out std_logic;

clk_out : out std_logic

);

end entity lfsr_16bit;

architecture rtl of lfsr_16bit is

signal lfsr_reg : std_logic_vector(15 downto 0) := „0101010101010101”;

signal feedback_bit : std_logic;

signal counter : integer :=1;

signal cbit : std_logic := ‘1’;

begin

process(clk, reset_p)

begin

if (reset_p = ‘1’) then

lfsr_reg <= „0101010101010101”;

counter <=1;

elsif (rising_edge(clk)) then

if (enable = ‘1’) then

counter <= counter+1;

if (counter = 6) then

feedback_bit <= lfsr_reg(15) xor lfsr_reg(14) xor lfsr_reg(11) xor lfsr_reg(5);

lfsr_reg <= feedback_bit & lfsr_reg(15 downto 1);

cbit <= not cbit;

counter <= 1;

end if;

end if;

end if;

end process;

lfsr_out <= lfsr_reg(0);

clk_out <= cbit;

end architecture rtl;

Listing 1. Przykładowy kod VHDL dla rejestru przesuwnego z liniowym sprzężeniem zwrotnym. Gowin EDA, w przeciwieństwie do innych środowisk programistycznych, nie pozwala skopiować formatowania

Drugim krokiem było skonfigurowanie zegara, a także połączeń między sygnałami logicznymi, a fizycznymi pinami układu FPGA. O ile narzędzie „FloorPlanner” pozwala dość łatwo i przyjemnie skonfigurować fizyczne piny oraz przynależne im sygnały, o tyle konfiguracja zegara sprawiła autorowi nie lada problem. Ktoś doświadczony oczywiście wie, co należy zrobić, ale w przypadku osób zaczynających w tym temacie od zera (tak, jak autor niniejszego artykułu) jest to już pewne wyzwanie. Inne zestawy startowe FPGA, szczególnie od takich firm, jak Digilent (którego grupą klientów są głównie uczelnie), czy nawet Xilinx, Altera lub Lattice, zwykle zawierają bogaty zbiór materiałów edukacyjnych dla początkujących, w tym poradniki „krok po kroku”. Sipeed, mimo iż cenowo plasuje się w kategorii hobbystycznych zestawów startowych, nie dostarcza absolutnie niczego. Jeśli, szanowny Czytelniku, kupisz ten zestaw, to... pozostajesz zdany na siebie. Autor zajrzał z ciekawości do pliku pomocy Gowin EDA, ale tam też nie znalazł żadnej pomocy. Na szczęście jednak firma Gowin zapewnia sporą kolekcję dokumentów wyjaśniających różne aspekty programowania swoich układów FPGA. Tu należy pochwalić producenta za wysoki poziom anglojęzycznej dokumentacji, z wyjątkiem jednego detalu: kody źródłowe są sformatowane jak zwykły tekst.

Rozwiązanie problemu okazało się dość proste: trzeba było przypisać wejście zegarowe do pinu E2 połączonego z generatorem kwarcowym 50 MHz. Oczywiście to nie zadziałało, gdyż ów ten pełni dodatkową funkcję o oznaczeniu CPU. Trzeba zatem w ustawieniach konfiguracji zezwolić syntezatorowi na użycie tej linii jako pinu ogólnego. Po wskazaniu go jako wejścia dla sygnału zegara pojawił się nowy komunikat:

WARN (TA1132) : ‘clk’ was determined to be a clock but was not created

Tu trzeba przejść do narzędzia Timing Constraints, znaleźć nasz port clk i dodać go jako zegar 50 MHz. Po tym błąd znika.

Ostatnim krokiem jest programowanie. Płytka została połączona z komputerem za pomocą dołączonego do zestawu przewodu, programator/debugger został rozpoznany bez większych problemów. Mamy dostępne dwie opcje umieszczenia kodu: w zewnętrznej pamięci Flash, która przechowuje całą konfigurację, albo bezpośrednio w pamięci układu FPGA. Druga metoda ma tę wadę, iż odłączenie zasilania wymazuje konfigurację i po jego ponownym podłączeniu wczytana zostanie zawartość pamięci Flash. Z drugiej strony programowanie pamięci SRAM układu jest znacznie szybsze (w przypadku przykładowego kodu było to niecałe 5 sekund programowania SRAM, kontra ponad 110 sekund programowania całej pamięci Flash) i pozwala na szybkie testowanie zmian w kodzie VHDL lub Verilog, bez utraty zapisanej w pamięci Flash, poprzedniej konfiguracji.

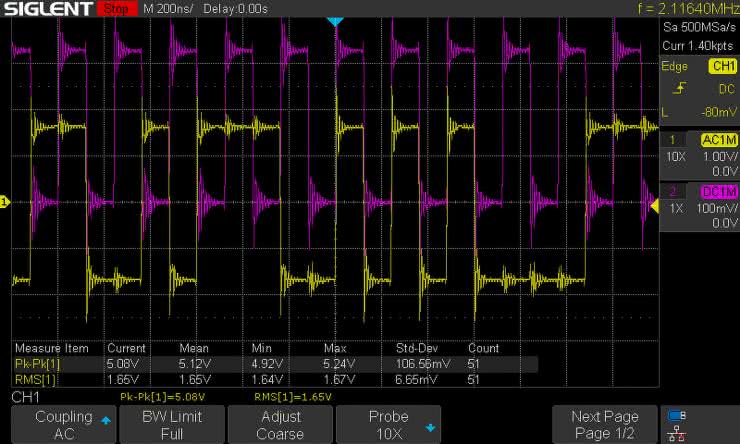

Autor wybrał programowanie do pamięci Flash. Sygnał reset połączony jest z pinem H10 (przycisk S2), sygnał enable – z H11 (przycisk S1), wyjście rejestru – z pinem K1 (pin 2 J3), a wyjście zegara – z K2 (pin 1 J3). S2 zeruje rejestr przesuwny, a S1 aktywuje jego pracę. Rysunek 1 pokazuje zrzut ekranu z oscyloskopu, na którym widać sygnały wyjściowe. Częstotliwość wyjściowa wynosi ok. 5 MHz, kanał 1 to strumień bitów, a kanał 2 to wyjście zegarowe. Znaczne „dzwonienie” na przebiegach wynika ze zbyt długich połączeń masy sond do płytki. Warto zwrócić uwagę na jedną, szczególną cechę układów FPGA: wyjścia zmieniają swój stan jednocześnie. W końcu opisaliśmy fizyczny układ bramek i rejestrów oraz połączeń między nimi, a nie sekwencję zdarzeń. Co ważniejsze, Tang Primer 25k ma wystarczająco dużo elementów logicznych w zastosowanym w nim układzie FPGA, więc można w nim umieścić kilka lub nawet kilkanaście dość skomplikowanych obwodów logicznych, które mogą pracować razem lub niezależnie od siebie, jeśli jest taka potrzeba.

Podsumowanie

Czy zestaw Sipeed Tang Primer 25k jest wart zainteresowania? Tak, gdyż przede wszystkim jest sporo tańszy od innych, porównywalnych zestawów z układami FPGA od głównych graczy na tym rynku. Modułowa budowa zestawu pozwala też wykorzystać moduł FPGA we własnych projektach, jeśli tylko 75 pinów I/O wystarczy do realizacji projektu. Wadą produktu Sipeed jest dokumentacja. O ile otrzymujemy wszystkie schematy, rysunki techniczne, specyfikacje, a nawet modele 3D, to producent nie oferuje niczego w kategorii „dla początkujących”. Nie dostajemy ani poradnika „Jak zacząć”, ani bogatej kolekcji przykładowych projektów. Gowin Semiconductor oferuje nieco więcej materiałów, w tym opisy modułów z IP Generatora, czy wskazówki odnośnie kodowania. Doświadczony programista układów FPGA nie będzie miał zatem żadnych problemów z płytką Tang Primer 25k, ale początkujący hobbysta, do którego ten zestaw jest raczej kierowany, będzie skonfundowany i zagubiony. Bez podręcznika (lub dobrego kursu, jak te publikowane na łamach EP) do VHDL lub Verilog się nie obejdzie. Autor zamierza kontynuować swoją przygodę z FPGA i zestawem Tang Primer 25k.

Paweł Kowalczyk, EP

Zaloguj

Zaloguj