Każdy programista systemów embedded doskonale wie, że wbudowane bloki peryferyjne mikrokontrolerów pozwalają zmniejszyć zużycie energii, podnieść wydajność obliczeniową, a także istotnie zredukować objętość kodu maszynowego. W zależności od modelu uC do dyspozycji projektantów są m.in. wzmacniacze operacyjne, ulepszone przetworniki analogowo-cyfrowe (ADC) czy też uniwersalne timery (UTMR) oraz sprzętowe generatory sygnałów PWM. Jednym z najciekawszych rodzajów bloków peryferyjnych są te, które pozwalają implementować logikę dyskretną oraz bezpośrednio łączyć ze sobą różne peryferia procesora. W tym artykule omówione zostaną rozwiązania takie, jak: konfigurowalne komórki logiczne (Configurable Logic Cell, CLC oraz Configurable Custom Logic, CCL), system obsługi zdarzeń (Event System, EVSYS), a także blok łączenia sygnałów (Signal Routing, SR). Pokażemy także sposoby ich praktycznego wykorzystania w określonych aplikacjach.

CLC/CCL

Bloki peryferyjne, określane mianem CLC i CCL, to programowalne tablice typu Look-up-Table (LUT), z których każda stanowi w istocie odpowiednik pojedynczej komórki układu FPGA. Funkcja logiczna, skonfigurowana wewnątrz każdej instancji takiego peryferium, jest definiowana „w locie”. CLC/CCL może działać niezależnie od procesora, co pozwala efektywnie zastąpić zewnętrzne układy logiczne. Pomiędzy CLC i CCL istnieją drobne różnice w implementacji - CLC jest specyficzne dla mikrokontrolerów z rodziny PIC, podczas gdy komórki CCL są dostępne w procesorach AVR. Podstawowe działanie każdego z wymienionych bloków pozostaje jednak takie samo.

Tłumienie drgań styków

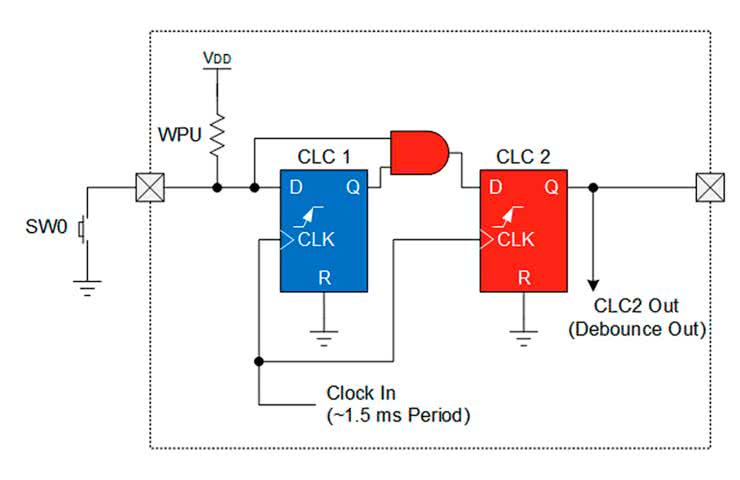

Jednym z najczęstszych zastosowań CLC/CCL jest sprzętowa implementacja tłumienia drgań styków przy użyciu timera/oscylatora. W nocie aplikacyjnej AN2805 można znaleźć aż trzy sposoby implementacji tłumienia tych niepożądanych sygnałów przy użyciu CLC.

Aby zaimplementować filtr drgań styków, należy jedną z komórek (CLC 1 na schemacie wg rysunku 1) skonfigurować jako przerzutnik typu D, zatrzaskujący stan z wejścia GPIO, podłączonego do przycisku lub przełącznika. Blok CLC 2 wykonuje natomiast operację iloczynu logicznego (AND) sygnału wyjściowego przerzutnika CLC 1 oraz aktualnego stanu wejścia cyfrowego, a następnie zatrzaskuje wartość wynikową we własnym przerzutniku. Źródłem sygnału taktującego dla obu przerzutników jest wyjście timera lub oscylatora, pracującego z częstotliwością około 0,67 kHz.

Przy zastosowaniu bloków CCL, dostępnych w mikrokontrolerach AVR, to samo zadanie jest jeszcze prostsze - komórki CCL oferują bowiem funkcję filtracji sygnału wejściowego, która skutecznie wykonuje tę samą dwutaktową operację. CCL mogą być taktowane za pomocą oscylatora 1 kHz, co jest w zupełności wystarczające do realizacji tłumienia drgań styków.

Dekodowanie sygnałów kwadraturowych

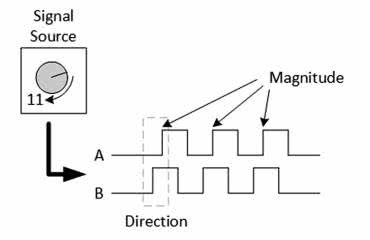

Innym przypadkiem użycia CLC jest implementacja dekodera kwadraturowego. Inkrementalne enkodery z wyjściem kwadraturowym generują dwa przebiegi prostokątne (A i B), przesunięte w fazie o 90°. Prędkość obrotowa jest reprezentowana przez liczbę przebiegów, natomiast znak różnicy fazy pozwala określić kierunek obrotów (rysunek 2).

Aby zdekodować parę sygnałów kwadraturowych, komórki CLC przekształcają ten przebieg na dwa wyjścia, reprezentujące impulsy odpowiadające za obrót w kierunku zgodnym lub przeciwnym do ruchu wskazówek zegara. Dalej jest już bardzo łatwo - dwa timery sprzętowe mikrokontrolera niezależnie zliczają odebrane impulsy, zaś program - na podstawie wyników zliczania w obu kanałach - może wyliczyć zarówno prędkość, jak i kierunek obrotów osi enkodera.

System zdarzeń

System zdarzeń (EVSYS) przeznaczony jest do wybierania sygnału wyjściowego z jednego peryferium i kierowania go do innych bloków, znajdujących się wewnątrz mikrokontrolera. Ta łączność może odbywać się bez udziału rdzenia procesora, co oszczędza energię w trybie uśpienia lub bezczynności i znacząco poprawia wydajność. Należy przy tym pamiętać, że EVSYS występuje tylko w mikrokontrolerach AVR.

Port SR

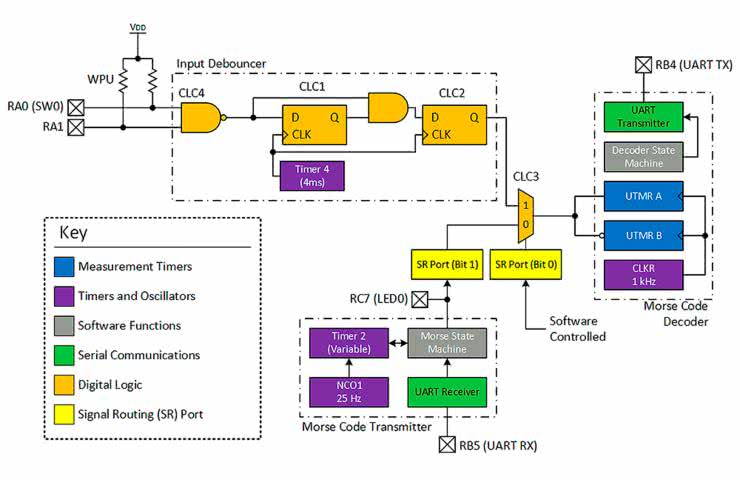

W mikrokontrolerach PIC dostępne jest natomiast peryferium określane mianem portu SR (ang. Signal Routing Port). Ma ono strukturę przypominającą standardowy port I/O, ale bez wyprowadzenia na fizyczny pin w obudowie mikrokontrolera. Bity portu SR można ustawiać i kasować programowo, ale w tym przypadku użytkownik ma także do dyspozycji sygnały wyjściowe urządzeń peryferyjnych, a nawet funkcjonalność rejestru przesuwnego. Port SR współpracuje również z funkcją Peripheral Pin Select (PPS), którą można znaleźć także w mikrokontrolerach PIC. PPS zapewnia projektantowi elastyczność w przydzielaniu wejść/wyjść, umożliwiając przenoszenie cyfrowych sygnałów do różnych pinów mikrokontrolera oraz zapewniając innym blokom peryferyjnym możliwość indywidualnego wyboru bitów portu SR jako wejść. Pozwala to na konstruowanie zaawansowanych maszyn stanu i kontrolowanie ich za pomocą tego peryferium.

Wybór sygnału wewnętrznego

Jednym z ciekawszych przypadków użycia portu SR oraz komórki CLC jest implementacja multipleksera do wybierania sygnałów wewnętrznych mikrokontrolera. Można to wykorzystać do realizacji wewnętrznego autotestu lub do wybierania jednego z N sygnałów do dalszego przetwarzania. Aby zaimplementować multiplekser 2:1, należy zastosować komórkę CLC - w przypadku topologii 4:1 potrzebne są już trzy bloki CLC i dwa bity z portu SR. Sterowanie multiplekserem odbywa się przy użyciu bitu portu SR, pełniącego funkcję linii wyboru. Schemat omawianego bloku można zobaczyć na rysunku 3.

Jedną z zalet tej implementacji w porównaniu z PPS jest szybkość i elastyczność. PPS można zablokować, aby zapobiec przypadkowym zmianom stanu w czasie wykonywania programu. Dodatkowo użytkownik możne ustawić bit konfiguracyjny, aby mieć pewność, że PPS będzie można odblokować tylko raz.

Implementacja multipleksera przy użyciu CLC umożliwia programowi zmianę wejść w dowolnym momencie bez konieczności wykonywania za każdym razem sekwencji odblokowania. Ten scenariusz użycia został użyty w programie demonstracyjnym prostego nadajnika i odbiornika alfabetu Morse’a, wykonanego na bazie mikrokontrolera z rodziny PIC18F56Q71 firmy Microchip - multiplekser służy tutaj do wyboru pomiędzy wyjściem nadajnika a zewnętrznym sygnałem wejściowym (odbiorczym) - schemat takiej implementacji można zobaczyć na rysunku 4.

Obliczanie parzystości ze wspomaganiem sprzętowym

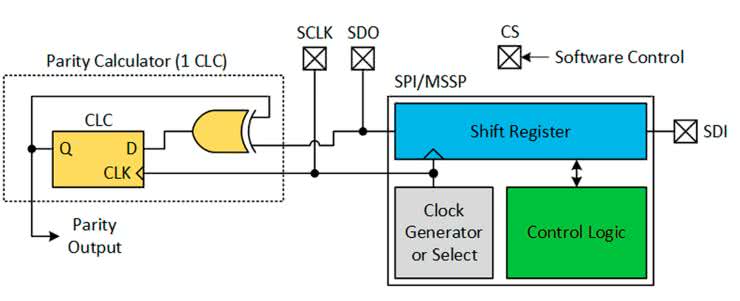

W niektórych przypadkach konieczne jest wygenerowanie bitu parzystości do nadania lub odbioru danych. Obliczanie parzystości w oprogramowaniu jest trywialne, ale zajmuje dodatkowy czas procesora - znacznie efektywniejsze jest zatem wykonanie tego zadania na drodze sprzętowej. Schemat przykładowej implementacji pokazano na rysunku 5. W tym przypadku badany wzorzec jest przechowywany w pamięci globalnej.

Aby przyspieszyć obliczenia bitu parzystości, można użyć sprzętowego interfejsu SPI w połączeniu z CLC. Blok SPI zawiera szeregowy rejestr przesuwny do przesyłania i odbierania danych. Wyjście rejestru oraz sygnał zegarowy SPI można wprowadzić do CLC, zaś na wyjściu przerzutnika zastosowanej komórki logicznej dostępna będzie informacja o parzystości słowa, znajdującego się w rejestrze.

Podsumowanie

Sprzętowe peryferia mikrokontrolerów pełnią fundamentalną funkcję w systemach wbudowanych. Dzięki nim znacząco rośnie wydajność obliczeniowa mikrokontrolerów, spada także zapotrzebowanie na pamięć oraz energię, pobieraną z systemu zasilania. Konfigurowalne bloki logiczne są szczególnie cennymi narzędziami do obsługi prostych zadań, takich jak usuwanie drgań styków czy też dekodowanie kwadraturowe. Kreatywne wykorzystanie peryferiów sprzętowych udoskonala projekty i przesuwa granice możliwości mikrokontrolera.

Robert Perkel

Improving Embedded Systems with Logic and Flexibility Hardware Peripherals

Zaloguj

Zaloguj