Współczesne procesy produkcji urządzeń elektronicznych są szczególnie podatne na wpływ licznych czynników technologicznych i logistycznych: wyraźnie oddziałują one na całkowity budżet wytworzenia danego produktu. Co ważne, zależności te są widoczne nie tylko w masowej produkcji (nietrudno oszacować, jak nawet najmniejszy dodatkowy rezystor bądź kondensator przekłada się na koszt serii urządzeń produkowanych w setkach tysięcy czy milionach egzemplarzy) – nawet w niewielkiej skali brak optymalizacji projektu oraz błędy ogólnej logistyki procesu produkcyjnego mogą przełożyć się na niepożądany wzrost wydatków na zaopatrzenie, a jednocześnie na opóźnienia w realizacji zamówień.

Problem nadmiarowych kosztów generowanych przez zastosowanie w projekcie dodatkowych (niewymaganych przez oczekiwaną funkcjonalność i/lub wymogi bezpieczeństwa bądź kompatybilności elektromagnetycznej) elementów to zaledwie czubek przysłowiowej góry lodowej. W równym stopniu na straty producenta może wpłynąć zastosowanie komponentów zbyt drogich czy też mających nieodpowiedni status rynkowy. Do tej pory projektanci mogli wybierać komponenty, kierując się czy to polityką danego producenta (wielu potentatów rynku półprzewodników wprowadziło programy product longevity, zapewniając dostępność danego procesora bądź innego układu scalonego przez określony czas liczony w latach od daty wprowadzenia na rynek), czy to aktualnym statusem handlowym [1].

W dobie krzemowego krachu, wywołanego m.in. przez pandemię covid-19, problem ten stał się znacznie bardziej palący, gdyż wiele (jeżeli nie większość) komponentów znikała i wciąż znika z magazynów w niespotykanym wcześniej tempie, zaś planowane terminy kolejnych dostaw są odległe o kilkadziesiąt tygodni, a nierzadko nawet o kilka lat.

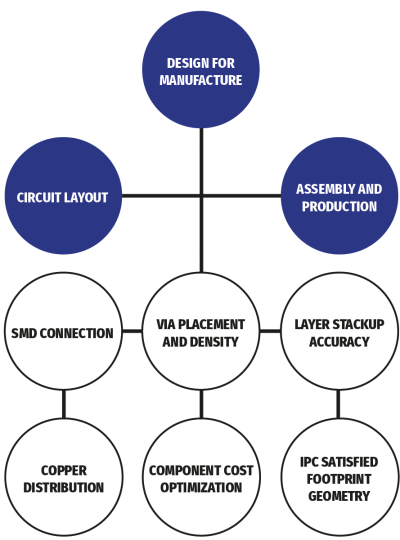

DFM – design for manufacturing

Remedium zarówno na opisane wyżej problemy, jak i na wiele innych zagrożeń czyhających na kieszenie wytwórców elektroniki jest zastosowanie zasad oraz technik projektowania zorientowanego na wytwarzanie (DFM).

Metodologia ta obejmuje bardzo wiele zagadnień (rysunek 1), a wśród nich warto wymienić m.in.:

- optymalizację ułożenia elementów na PCB z uwzględnieniem tak samego lutowania płytki drukowanej, jak i jej kooperacji z mechaniką urządzenia,

- właściwe zarządzanie parametrami ścieżek i pól miedzi,

- zastosowanie norm i wytycznych dot. geometrii i rozmiaru padów montażowych,

- wybór ułożenia oraz technologii wykonywania przelotek,

- sposób przyłączania komponentów SMD,

- optymalizację BOM projektu,

- uwzględnienie tolerancji wykonawczych stosu warstw PCB,

- przygotowanie markerów optycznych dla systemów wizyjnych.

Tematyka DFM jest niezwykle szeroka i w kompleksowym ujęciu obejmuje swoim zasięgiem praktycznie cały proces tworzenia produktu, od schematu ideowego czy też wyboru komponentów, aż po kwestie montażu kompletnego urządzenia (włącznie z wewnętrznym okablowaniem, umieszczeniem urządzenia w obudowie czy też „uzbrojeniem” panelu czołowego, złączy oraz montażem podsystemów mechanicznych). W tym artykule skupimy się na najważniejszych aspektach ściśle powiązanych z projektowaniem obwodów drukowanych.

Optymalizacja na poziomie BOM

Właściwy dobór elementów do danego projektu pozwala uniknąć szeregu problemów, które mogłyby pojawić się na późniejszych etapach pracy z urządzeniem. Wcześniej wspomnieliśmy już o konieczności zwracania uwagi na aktualny status komponentów (active, obsolete, end of life, not recommended for new designs), teraz natomiast rozszerzymy wątek o kolejne zagadnienia praktyczne.

Unifikacja typów i wartości elementów – każda dodatkowa pozycja na liście BOM urządzenia sprawia, że konieczne jest wykonanie dodatkowych czynności, zarówno w procesie kompletacji podzespołów, jak też późniejszego montażu. Zbyt duże zróżnicowanie drobnych, ale licznych elementów (np. rezystorów) wydłuża proces zamawiania dostaw, a dodatkowo utrudnia zarządzanie zmianami (np. doborem zamienników) w przypadku wystąpienia braków magazynowych. Warto jednak dodać, że także na etapie montażu automatycznego i ręcznego spora liczba różnych komponentów stanowi pewne utrudnienie. W przypadku maszyn pick & place wiąże się to z koniecznością użycia dodatkowych podajników, co wydłuża proces uzbrajania maszyny przed montażem oraz (teoretycznie) zwiększa ryzyko błędów obsługowych, a dodatkowo utrudnia montaż z użyciem mniejszych automatów o ograniczonej liczebności zasobników. Montaż ręczny także ulega w takiej sytuacji wydłużeniu – znacznie łatwiej i szybciej można bowiem wmontować serię np. 5 takich samych rezystorów na jednej płytce drukowanej, niż po wlutowaniu każdego z nich sięgać po element o innej wartości. Unifikacja elementów w zakresie danego obwodu nie oznacza rzecz jasna, że należy naginać projekt kosztem parametrów funkcjonalnych bądź kultury pracy pod względem EMC – chodzi jedynie o uniknięcie niepotrzebnego zróżnicowania BOM tam, gdzie wartości elementów nie są krytyczne.

Optymalizacja rodzaju złączy – wielu elektroników jest przyzwyczajonych do stosowania „znanych i lubianych” komponentów, nie starając się – o ile nie jest to wyraźnie konieczne lub narzucone z góry – zastępować ich podzespołami zoptymalizowanymi dla danego projektu. Tymczasem nawet pozornie niewielkie zmiany z nawiązką odpłacą się podczas produkcji i to zarówno wielko-, jak i małoseryjnej. Przykładem mogą być złącza, stosowane do połączenia pomiędzy dwiema płytkami drukowanymi (modułami) urządzenia. Nierzadko wybór pada od razu na popularne złącza szpilkowe (goldpiny). Choć trudno odmówić im uniwersalności i wygody w zastosowaniach prototypowych, to w przypadku wytwarzania wielkoseryjnego konieczność ręcznego pozycjonowania (a często także lutowania) złączy przewlekanych może znacząco wydłużyć proces produkcji oraz wymusić dodatkowe koszty (związane np. z zatrudnieniem pracowników do montażu manualnego). Zmiana klasycznych złączy THT na ich wersje do montażu powierzchniowego (fotografia 1) umożliwia zlecenie pozycjonowania złączy odpowiedniemu robotowi montażowemu, co pozwala na zautomatyzowanie całego procesu montażu, od umieszczenia całkowicie nieobsadzonego panelu płytek drukowanych, aż do odbioru gotowych do programowania/testowania płytek.

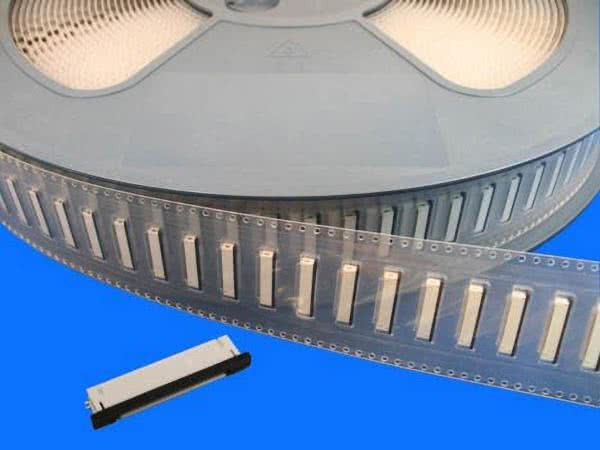

Innym, doskonałym przykładem będą w tym miejscu złącza rastrowe z kluczem. O ile w wielu przypadkach ich użycie będzie uzasadnione funkcjonalnie (np. z uwagi na dużą obciążalność prądową), to z punktu widzenia całościowego procesu produkcyjnego spowoduje ono konieczność wyprodukowania odpowiednich wiązek kablowych (docinanie przewodów, zaciskanie pinów, składanie złączy oraz zakładanie osłon, opasek zaciskowych, itp.). W przypadku łączenia relatywnie niskomocowych modułów na niewielkich odległościach wewnątrz obudowy urządzenia, nieporównanie bardziej efektywne może okazać się zastosowanie złączy ZIF oraz taśm FFC – złącza zostaną zamontowane na PCB bez większego problemu przez niemal dowolny automat pick & place (dzięki opakowaniu w standaryzowanej taśmie kompatybilnej z podajnikami – fotografia 2), zaś przewody płaskie nie będą już wymagały praktycznie żadnych dodatkowych czynności.

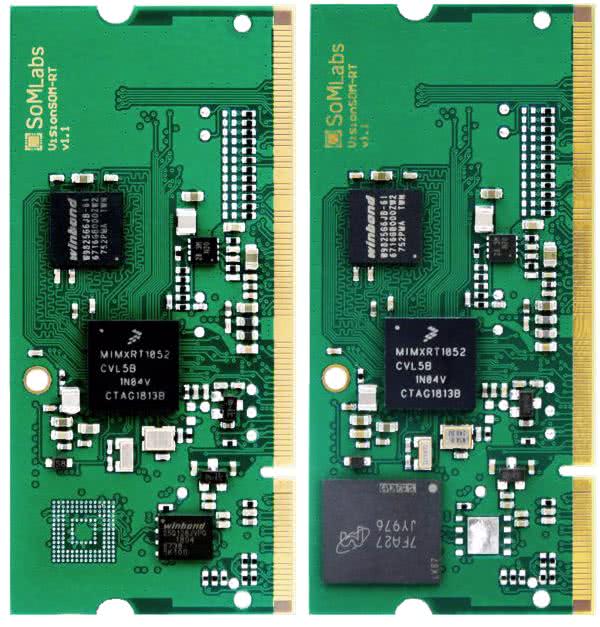

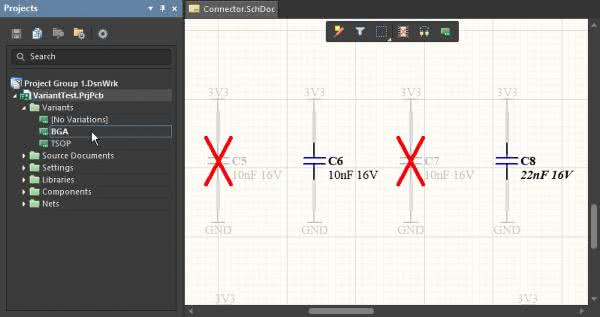

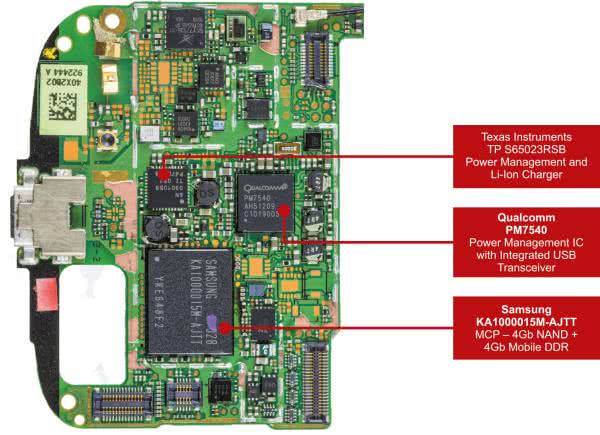

- Zastosowanie wariantów montażowych – nie jest tajemnicą, że na płytkach drukowanych przeważającej większości urządzeń elektronicznych dostępnych na rynku istnieje wiele nieobsadzonych pól lutowniczych, zarówno dla prostych elementów dyskretnych, jak i układów scalonych. W niektórych sytuacjach mogą to być pozostałości po wersjach rozwojowych produktów, innym razem dodatkowe footprinty zostały przewidziane jako „zapasowe”, np. na wypadek ewentualnej kalibracji. Bardzo często jednak zabieg taki służy ograniczeniu funkcjonalności danych linii produktowych, gdy ten sam projekt PCB jest wykorzystywany zarówno w „pełnowymiarowych” urządzeniach, jak i tańszych, ograniczonych wersjach „lite” – powszechnie spotykanym przykładem takiej dywersyfikacji są wersje minikomputerów SBC różniące się ilością, a nawet rodzajem dostępnej „na pokładzie” pamięci (fotografia 3). Znaczne ułatwienie dla projektantów stanowią tu gotowe narzędzia wspomagające zarządzanie wariantami montażowymi – przykładowo, środowiska takie jak Altium Designer (rysunek 2), Autodesk Eagle czy Proteus mają wbudowane zestawy funkcji do obsługi zróżnicowanych wersji montażowych (Assembly Variants), pozwalające m.in. na definiowanie obecności elementów, ich wersji (np. komponenty pasywne o różnych wartościach), a nawet… zamienników.

Zastosowanie norm IPC

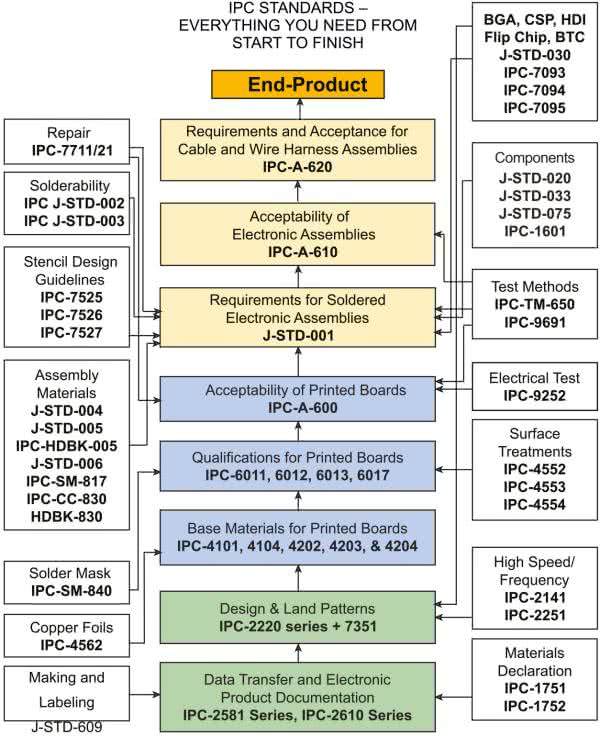

Dobre praktyki inżynierskie to nie tylko sprawne wykorzystanie zdobywanych przez lata doświadczeń praktycznych – równie ważne jest stosowanie w codziennej pracy aktualnych norm branżowych, które istotnie poprawiają jakość produktów i przyczyniają się do zwiększenia powtarzalności serii produkcyjnych. W przypadku wytwarzania elektroniki norm mających zastosowanie do konkretnego produktu jest naprawdę wiele – te, które obowiązują w niemal wszystkich gałęziach przemysłu elektronicznego, pokazano schematycznie na rysunku 3.

Do najważniejszych i najczęściej wykorzystywanych należą normy:

- IPC-7351B – footprinty dla najpopularniejszych typów obudów SMD,

- IPC-2221B – ogólne standardy dot. projektowania PCB,

- IPC-2222B – wymagania dot. obwodów drukowanych na podłożach sztywnych.

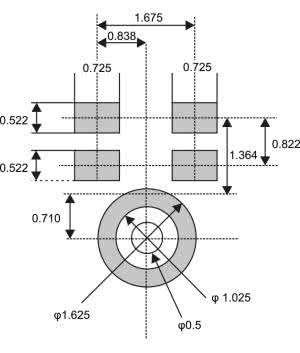

Co ważne, choć zastosowanie wytycznych norm podczas projektowania danego urządzenia jest wysoce pożądane (ale zwykle nieobowiązkowe), to dla wielu elementów o niestandardowych obudowach – z oczywistych przyczyn – niemożliwe będzie bezpośrednie użycie równań i zaleceń opracowanych przez IPC. Doskonałym przykładem mogą być tutaj footprinty niektórych mikrofonów MEMS, czujników ciśnienia, itp. – w takich przypadkach należy podążać za wytycznymi udostępnionymi przez producenta w notach katalogowych (rysunek 4).

W przypadku opisanych przez normę IPC-7351B zaleceń dot. rozmiaru i geometrii padów dla określonych grup elementów, celem stosowania standardu jest zwiększenie niezawodności połączeń, a także optymalizacja pod kątem spodziewanego sposobu montażu. Jak w przypadku każdej normy technologicznej, wytyczne IPC-7351 powstały na bazie wnikliwej obserwacji i badań połączeń lutowanych, dzięki czemu możliwe jest uniknięcie najczęstszych problemów podczas montażu – np. powstawania zwarć pomiędzy sąsiadującymi padami i/lub wyprowadzeniami elementów (co może wystąpić w przypadku zbyt małych odstępów pomiędzy krawędziami padów, przy braku separacji w postaci soldermaski, etc.).

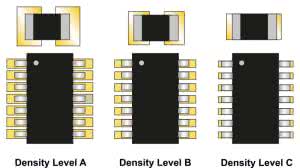

Odpowiedni balans pomiędzy łatwością lutowania ręcznego komponentów (w przypadku których jest to możliwe, np. elementów pasywnych, układów w obudowach SOIC, SOT czy TQFP), odpornością na wibracje oraz gęstością upakowania elementów określają zdefiniowane przez normę poziomy gęstości (IPC Density Levels – rysunek 5):

- Poziom A – pady elementów są wydłużone i poszerzone oraz w większym stopniu wystają poza obrys komponentu. Powstałe dzięki temu połączenia są bardziej odporne na wstrząsy i wibracje, łatwiej też można je serwisować lub montować ręcznie (fotografia 4). W przypadku części elementów (wyposażonych w wyprowadzenia wysunięte poza obrys obudowy) możliwe jest zastosowanie procesu lutowania na fali. Zwiększona odporność mechaniczna stanowi natomiast gwarancję niezawodności w aplikacjach szczególnie narażonych na drgania – np. w branży motoryzacyjnej, militarnej bądź przemysłowej.

- Poziom B – pady elementów mają rozmiary „nominalne”, jest to zatem złoty środek pomiędzy dużą gęstością upakowania a odpornością mechaniczną. Poziom ten dobrze nadaje się do większości „typowych” zastosowań (np. elektroniki konsumenckiej niewymagającej silnej miniaturyzacji).

- Poziom C – footprinty są pomniejszone praktycznie do granic możliwości, co znacząco przesuwa granicę gęstości upakowania elementów w stronę urządzeń silnie zminiaturyzowanych (fotografia 5). Znacznie mniejsza ilość lutowia łączącego pady z wyprowadzeniami elementów zmniejsza jednak odporność na powtarzalne narażenia mechaniczne.

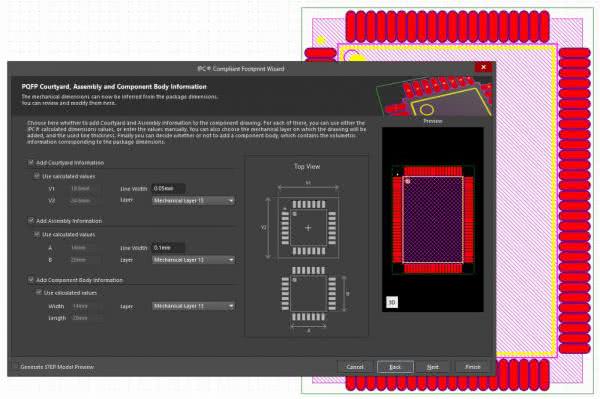

Niebywałą pomocą dla inżynierów są gotowe generatory standardowych footprintów, dostępne w bardziej zaawansowanych środowiskach EDA. Przykład – generator IPC Compliant Footprint Wizard dostępny w pakiecie Altium Designer został pokazany na rysunku 6.

Zadaniem projektanta jest jedynie wprowadzenie najważniejszych danych z noty katalogowej (typu obudowy, liczby i układu wyprowadzeń, obecności i ew. wymiarów padu/padów termicznych, granicznych wymiarów korpusu, długości oraz rozstawu wyprowadzeń, etc.), zaś program automatycznie zastosuje równania z odpowiedniej części normy IPC i – uwzględniając dopuszczalną tolerancję pozycjonowania automatu pick & place – wygeneruje footprint idealnie dostosowany do potrzeb projektanta. Dodatkową zaletą korzystania z generatorów bibliotecznych jest automatyczne centrowanie śladów PCB dla tworzonych elementów, co – w połączeniu z ogromną precyzją najnowocześniejszych maszyn pick & place (przykładowo, roboty z serii YSM10 marki Yamaha dostępne w firmie RENEX – fotografia 6, pracują z dokładnością pozycjonowania ±0,035 mm, czyli niecałe 1,4 mils!) – pozwala osiągnąć praktycznie idealne wyniki układania komponentów na powierzchni płytki drukowanej.

Optymalizacja na poziomie ułożenia elementów (placement)

Kolejnym niezwykle istotnym i szerokim zagadnieniem związanym z projektowaniem DFM jest optymalizacja PCB pod względem ułożenia elementów. Choć temat ten pozostaje równie ważny z uwagi na kompatybilność elektromagnetyczną, jakość sygnałów analogowych i cyfrowych (przesłuchy, propagacja szumów z układu zasilania, sprzężenia pomiędzy podsystemami, etc.) czy też warunki bezpieczeństwa elektrycznego, to ogólne rozmieszczenie komponentów na powierzchni PCB powinno uwzględniać także łatwość montażu oraz operacji pomontażowych (testy, programowanie, montaż mechaniczny, integracja z okablowaniem wewnętrznym, etc.). Co więcej – nawet na poziomie otoczenia poszczególnych elementów, wzajemne odstępy i orientacje zyskują niebagatelne znaczenie, a to z uwagi na zjawiska rozpływu ciepła oraz różnice w pojemności cieplnej podczas lutowania. Poniżej zebraliśmy szereg praktycznych uwag dotyczących rozmieszczania elementów na wstępnym etapie projektowania PCB.

- Unifikacja orientacji elementów – ustawienie powtarzalnych – w obrębie danej płyty – elementów pasywnych i dyskretnych półprzewodników (rezystorów, kondensatorów, filtrów drabinkowych na równoległych szynach danych, tranzystorów, etc.) umożliwia zmniejszenie liczby obrotów głowicy pick & place, co w dłuższej perspektywie przekłada się na pewną oszczędność czasu pracy automatu montażowego. Zalecenie to nie może jednak warunkować ułożenia komponentów w sposób naruszający inne, zwykle ważniejsze zasady projektowania PCB – przykładowo, w przypadku gęstych macierzy BGA o dużej liczbie kondensatorów odsprzęgających konieczne będzie zwykle zastosowanie dwóch wzajemnie ortogonalnych orientacji, jednak nawet w takim przypadku warto zadbać o „sensowne” ułożenie elementów (przykład na fotografii 7).

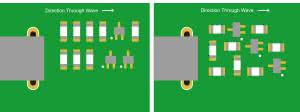

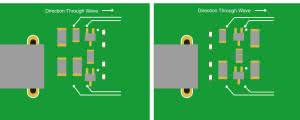

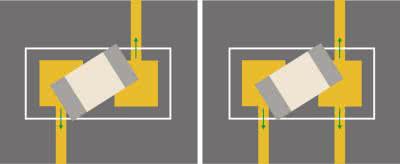

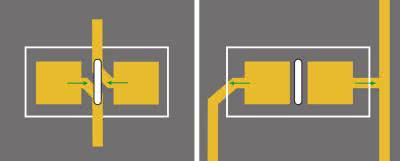

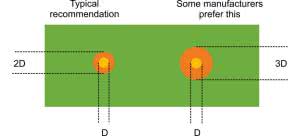

- Optymalizacja pod kątem montażu na fali – jeżeli z jakichś względów część elementów SMD musi być lutowana na fali, koniecznością staje się ustawienie komponentów w taki sposób, by zapewnić jak najlepsze warunki przejazdu PCB nad grzbietem fali lutowia. Do fundamentalnych zasad należy m.in. umieszczanie elementów dwuwyprowadzeniowych (np. R, L, C) w miarę możliwości w kierunku prostopadłym do kierunku ruchu PCB podczas lutowania (rysunek 7). Przeciwna zasada dotyczy ułożenia układów w obudowach typu SOIC i podobnych (oś długa układu powinna być równoległa do kierunku ruchu). Należy także unikać przesłaniania drobnych komponentów przez duże elementy (rysunek 8), gdyż to także grozi powstaniem niepewnych połączeń.

- Optymalizacja pod względem dostępów dla operacji manualnych – odpowiednie ustawienie komponentów ma duże znaczenie dla uzyskania odpowiednich dostępów serwisowych i montażowych. Przykładowo umieszczenie danego elementu w „wąwozie” utworzonym przez duże kondensatory, przekaźniki czy też wielkogabarytowe moduły znacząco utrudnia ewentualny serwis lub dokonywanie pomiarów. Problem ten jest również istotny w przypadku złączy, których nieprzemyślane ustawienie może spowodować trudności w podłączeniu wiązek kablowych lub – w skrajnym przypadku – wręcz je uniemożliwić. W silnie zminiaturyzowanych urządzeniach o dużej gęstości upakowania podzespołów w obudowie znaczenie zyskują nie tylko aspekty takie, jak rozmieszczenie podłączonych do PCB podsystemów (np. napędów, innych płytek drukowanych czy zewnętrznych czujników) – istotne mogą okazać się nawet promienie gięcia przewodów. Dobrym wyjściem jest wykorzystanie opcji symulacji 3D, dostępnej w większości liczących się pakietów EDA – połączenie wygenerowanego według projektu PCB trójwymiarowego modelu z modelem mechanicznym reszty urządzenia pozwala z bardzo dużą dokładnością przewidzieć potencjalne kolizje i zaradzić im, jeszcze zanim dokumentacja produkcyjna opuści stację roboczą konstruktora. Dobre ułożenie poszczególnych bloków urządzenia i skorelowanie z nim rozstawienia złączy pozwala zresztą na skrócenie wiązek oraz uproszczenie ich przebiegu, co przynosi kolejne oszczędności.

- Unikanie montażu elementów na dolnej stronie PCB – dobrą praktyką jest rozmieszczanie (w miarę możliwości) wszystkich komponentów na jednej stronie płytki drukowanej. Rozwiązanie takie pozwala uniknąć konieczności nakładania kleju, co wiązałoby się z przejazdem płytki przez kolejną maszynę (dyspenser automatyczny) i wydłużyłoby proces montażu. Rzecz jasna, uniknięcie rozmieszczania elementów na stronie bottom często jest niemożliwe – przykładem mogą być wspomniane wcześniej odprowadzenia padów BGA (fan-outs).

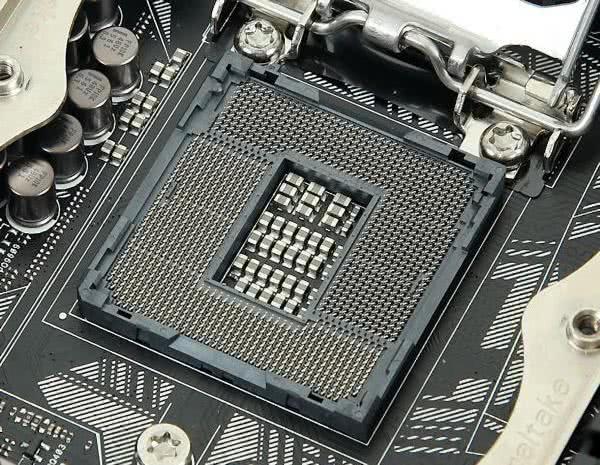

- Unikanie umieszczania komponentów pod innymi podzespołami – w niektórych sytuacjach sensowne (z punktu widzenia oszczędności miejsca na PCB) wydaje się umieszczenie drobnych elementów pod większym modułem. Warto jednak pamiętać, że rozwiązanie takie powoduje znaczne utrudnienie montażu, inspekcji czy też napraw serwisowych, o ile moduł (lub układ scalony) jest trwale zamocowany na płytce drukowanej – wyjątkiem są np. płyty główne komputerów. Bateria kondensatorów odsprzęgających jest często umiejscowiona w środkowym wycięciu podstawki ZIF, w którą wkładany jest procesor (fotografia 8).

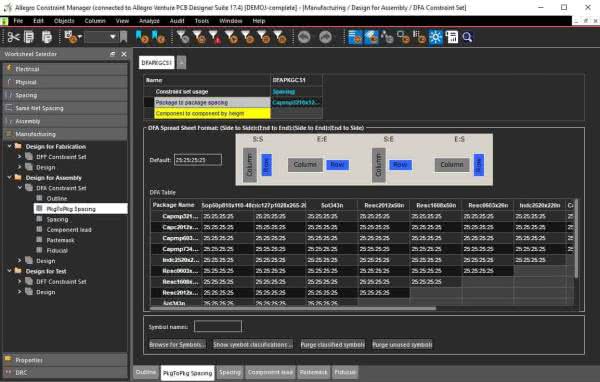

- Ustalenie reguł odstępów dla określonych konstelacji elementów – niektóre pakiety EDA umożliwiają ustalenie reguł projektowych w zakresie odstępów pomiędzy poszczególnymi elementami, umieszczonymi w różnych konstelacjach (równolegle bok do boku, współliniowo lub prostopadle) – przykład okna ustawień z programu Allegro PCB Designer marki Cadence pokazano na rysunku 9. Rozwiązanie to ułatwia utrzymanie użytecznych odstępów, niezbędnych np. z uwagi na zachowanie wygodnych dostępów montażowych w przypadku serwisu lub lutowania manualnego.

- Zwiększenie odstępu komponentów od krawędzi PCB – choć w wielu przypadkach umiejscowienie komponentów tuż przy krawędzi PCB (a nawet częściowo poza nią) jest wymagane przez mechanikę projektu (taka sytuacja ma przecież miejsce w przypadku wielu złączy), to w miarę możliwości należy unikać montowania komponentów SMD w bezpośredniej bliskości brzegów płytki drukowanej. Zasada taka ułatwia depanelizację automatyczną (a częściowo także ręczną) – nie należy zapominać, że stosowane do tego celu piły, gilotyny lub frezy mają pewną określoną szerokość i drobne elementy znajdujące się tuż obok krawędzi cięcia mogą wejść w kolizję z separatorem, co niechybnie spowoduje ich uszkodzenie. Problem dotyczy także systemów transportu PCB wewnątrz automatów produkcyjnych (np. pieców reflow), gdyż w skrajnych przypadkach komponenty na brzegach PCB mogą kolidować z elementami mechanizmu maszyny.

- Placement z uwzględnieniem konieczności nakładania powłok – w przypadku urządzeń wymagających nakładania powłok żelowych lub konformalnych konieczne jest uwzględnienie odstępów pomiędzy większymi (a szczególnie – wyższymi) elementami w taki sposób, by umożliwić zastosowanie pokryć natryskiwanych lub dozowanych za pomocą automatycznych dyspenserów. Warto dodać, że znaczną pomoc dla przedsiębiorstw montażu kontraktowego stanowią dokładne roboty lakierujące, umożliwiające precyzyjne dozowanie natryskiwanego lakieru za pomocą specjalnych zaworów i selektywną pracę ze sterowaniem poprzez system wizyjny – jako przykład warto wymienić roboty lakierujące Reeco dostępne w firmie RENEX (fotografia 9).

- Unifikacja pojemności cieplnej – umieszczenie drobnych elementów dwuwyprowadzeniowych (np. R, L, C) w taki sposób, że po jednej stronie znajdują się inne komponenty o niewielkich rozmiarach, a po drugiej – duże podzespoły o sporej pojemności termicznej, może ułatwiać powstawanie efektu nagrobkowania (tombstoning), polegającego na uniesieniu jednej z końcówek do góry, podczas gdy druga pozostaje przylutowana do płytki drukowanej (rysunek 10). Warto zatem ustawiać elementy w sposób równoległy do granicy obszarów o zróżnicowanej pojemności cieplnej.

Zagadnienia związane z prowadzeniem ścieżek i pól masy oraz wykonywaniem odwiertów

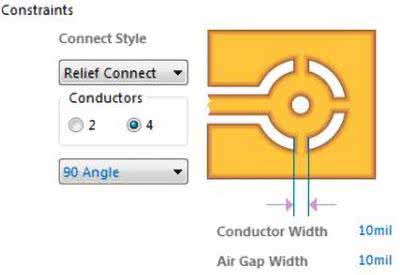

- Stosowanie odstępów termicznych (thermal reliefs) – współczesne pakiety oprogramowania EDA umożliwiają dodanie odstępów termicznych (thermal reliefs, thermals) niemal do każdego obiektu – padu SMD, THT lub przelotki (rysunek 11). O ile w przypadku tych ostatnich stosowanie odstępów w znakomitej większości (poza pewnymi specjalnymi sytuacjami) okazuje się całkowicie niepotrzebne, to w kwestii padów lutowniczych sytuacja wygląda diametralnie inaczej. Odstępy umożliwiają bowiem ograniczenie transferu ciepła z końcówek elementów przewlekanych do dużych pól miedzi (polygonów lub płaszczyzn zasilania/masy), co znakomicie ułatwia lutowanie końcówek elementów. Szczególne zasługi oddają opisywane odstępy termiczne w przypadku dużych kondensatorów elektrolitycznych, złączy wyposażonych w solidne ekranowanie czy też terminali śrubowych. Co ważne, te same wymagania w zakresie „thermali” dotyczą zarówno ręcznego montażu punktowego, jak i zautomatyzowanego lutowania THT za pomocą robotów lutowniczych (fotografia 10). Należy także pamiętać, że na łatwość lutowania punktowego i jakość uzyskiwanych efektów wpływa nie tylko projekt PCB, lecz także rozmiar grota oraz konstrukcja zastosowanej lutownicy. W przypadku wysokiej klasy stacji lutowniczych – np. serii CDE marki JBC (fotografia 11) – oprócz ergonomicznej rączki lutowniczej na kulturę pracy wpływ ma także doskonały transfer ciepła z elementu grzejnego do grota (oba te elementy są ze sobą nierozłącznie zintegrowane). Omawiana seria stacji lutowniczych ma zresztą dodatkową funkcjonalność – pomiar energii dostarczanej do spoiny w czasie lutowania, co pozwala monitorować proces montażu i niweluje ryzyko przegrzania, nawet w odniesieniu do wyjątkowo trudnych połączeń. Jeśli chodzi o komponenty SMD, zastosowanie odstępów umożliwia natomiast przeciwdziałanie opisanemu wcześniej zjawisku tombstoningu poprzez uzyskanie lepszej kontroli nad separacją termiczną.

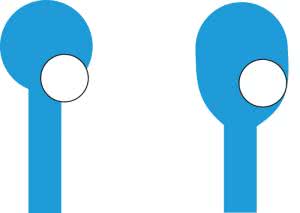

- Zachowanie symetrii doprowadzeń ścieżek do padów – w przypadku lekkich, dwukońcówkowych elementów RLC, diod krzemowych i LED czy też małych fotoelementów niewłaściwe doprowadzenie ścieżek do padów może spowodować niekontrolowane obracanie elementów, spowodowane powstawaniem podczas lutowania rozpływowego niewielkiego momentu siły, będącego wynikową napięć powierzchniowych „ściągających” końce elementu w przeciwnych kierunkach wokół jego środka (rysunek 12). Znacznie lepszym wyjściem jest doprowadzenie ścieżek z dwóch stron w osi długiej elementu lub prostopadle do niej, ale z wejściami znajdującymi się na sąsiadujących krawędziach padów pod komponentem (rysunek 13).

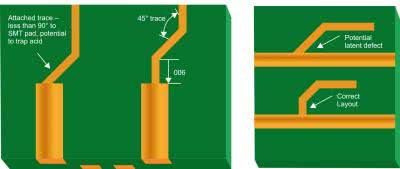

- Przeciwdziałanie powstawaniu „pułapek kwasowych” (acid traps) – choć współczesne procesy trawienia mozaik PCB wykorzystują precyzyjną kontrolę parametrów i wysokiej jakości wytrawiacze, to nadal można spotkać się z zaleceniami dotyczącymi przeciwdziałania tzw. pułapkom kwasowym. Pojęcie to odnosi się do newralgicznych miejsc, powstających w przypadku odejścia ścieżek od padów pod kątem innym niż 90° – kąt ostry, tworzony przez dwa odcinki ścieżki lub ścieżkę i krawędź padu, są narażone na powstawanie podtrawień (rysunek 14). Dziś pułapki kwasowe powszechnie uważane są za relikt technologicznej przeszłości, ale kątowego wyprowadzania ścieżek z padów warto unikać – i to nie tylko ze względów estetycznych, gdyż w przypadku zlecania produkcji PCB niedrogim fabrykom o niższym stopniu zaawansowania takie problemy (oraz – niestety – wiele innych) nadal się pojawiają. Wymogu ustawiania ścieżek pod kątem 90° nie należy rzecz jasna mylić ze – z gruntu błędnym – prowadzeniem ich zagięć pod kątem prostym, co jak wiadomo, prowadzi do pogorszenia integralności sygnałów o wysokiej częstotliwości.

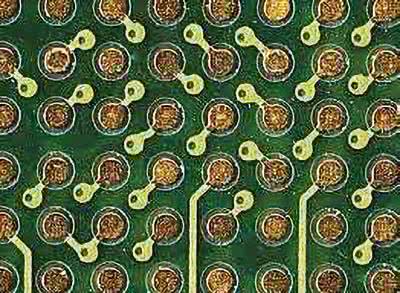

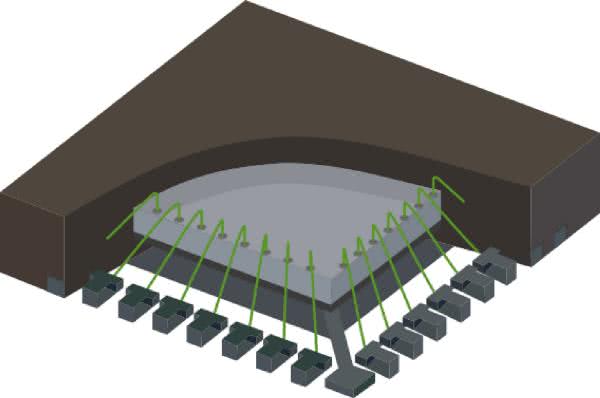

- Przelotki w padach lutowniczych – tematyka umieszczania przelotek pod układami BGA oraz bezpośrednio w padach rozmaitych komponentów jest szeroka i jako taka mogłaby stanowić materiał na osobny artykuł. Warto zatem jedynie zaznaczyć, że choć w wielu układach BGA można zastosować fan-out typu dog-bone (fotografia 12), w którym pokryte soldermaską przelotki są umieszczone pomiędzy padami BGA i połączone z nimi za pomocą krótkich ścieżek, to najbardziej gęste układy wyprowadzeń powodują konieczność umieszczania przelotek bezpośrednio (centralnie) w środku padów. Bez odpowiedniego zabezpieczenia otworów prowadziłoby to uciekania pasty lutowniczej na drugą stronę PCB, stąd w praktyce stosuje się różnego rodzaju techniki zamykania przelotek korkami, wykonanymi m.in. ze specjalnych żywic epoksydowych z domieszkami proszków metalicznych (np. miedzianych w otoczce srebrowej – fotografia 13). Rozwiązanie takie, oprócz znacznej poprawy warunków lutowania poprzez zabezpieczenie przed powstawaniem luk w objętości lutowia pod układem BGA, umożliwia ponadto znaczną poprawę odbioru ciepła z układu scalonego, co ma znaczenie dla komponentów wymagających intensywnego chłodzenia przez strukturę PCB. Co więcej – przelotki tego typu mogą być z powodzeniem stosowane także pod innymi układami, wyposażonymi w pady termiczne (np. QFN).

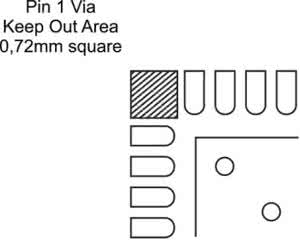

- Unikanie przelotek w obszarze pierwszego pinu obudów QFN – w przypadku obudów typu QFN (choć nie tylko) część metalowego podłoża nośnego układu scalonego jest wyprowadzona na zewnątrz obudowy, w rejonie pinu nr 1 (rysunek 15). Jeżeli w tym obszarze płytki drukowanej umieszczona będzie przelotka, to w pewnych warunkach istnieje ryzyko jej zlutowania (zwarcia) z podłożem układu. Dlatego też można spotkać się z zaleceniem pozostawienia niewielkiego obszaru zastrzeżonego (keep-out – rysunek 16), w którym nie należy umieszczać przelotek niepokrytych soldermaską. Gwoli ścisłości warto dodać, że podobne „styki” są też czasem widoczne w pozostałych rogach wielu obudów QFN, jak również w innych rodzajach obudów – np. LFCSP.

- Odstęp pól miedzi od krawędzi PCB – warto pamiętać, że pola masy (polygons) – choć mają szereg zalet i w znacznej części urządzeń oddają nieocenione zasługi pod kątem kompatybilności elektromagnetycznej oraz poprawy warunków zasilania – nie powinny być dociągane do samego brzegu PCB – pozostawienie odsłoniętych krawędzi warstwy miedzi podczas frezowania brzegów oraz depanelizacji naraża je na szybszą korozję (z uwagi na brak pokrycia soldermaską) a dodatkowo stwarza ryzyko oderwania cienkich resztek miedzi, które „wędrując” w losowe miejsce PCB, mogą doprowadzić w skrajnym przypadku do powstania zwarcia. Dodatkowo, ostre krawędzie pogarszają estetykę produktu i stwarzają ryzyko skaleczenia dla montażystów bądź serwisantów.

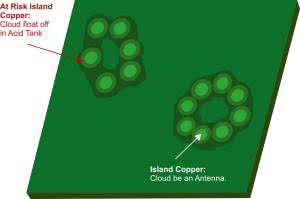

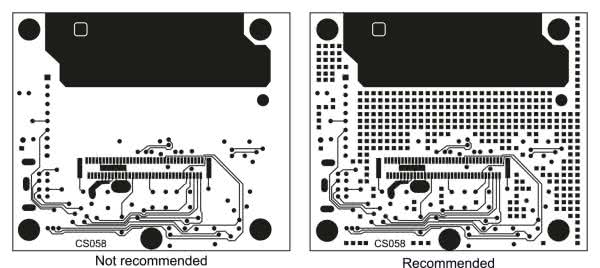

- Unikanie izolowanych wysp miedzi – pozostawienie w projekcie PCB niewielkich, odizolowanych (niepodłączonych) pól miedzi, otoczonych np. przez ścieżki, gęsto ułożone pady lub przelotki, może doprowadzić do podtrawienia i oderwania się takiego fragmentu folii miedzianej z oryginalnego położenia, zaś po „przewędrowaniu” w inne miejsce PCB kawałek folii może doprowadzić do uszkodzeń PCB (rysunek 17). Wyjątek stanowią specjalne wypełnienia dużych, pustych obszarów obwodu drukowanego, zrealizowane w postaci macierzy niepodłączonych padów, których celem jest ujednolicenie przepływu prądu podczas wykonywania pokryć (galwanizacji) ścieżek. Przykład zastosowania tej techniki, określanej jako copper balancing lub thieving, pokazano na rysunku 18. Warto dodać, że metoda ta jest wykorzystywana także do poprawy właściwości termicznych PCB (ochrona przed wypaczaniem w procesie lutowania).

- Markery optyczne (fiducials) – współczesne automaty pick & place muszą zapewnić dokładność pozycjonowania, umożliwiającą współpracę z najmniejszymi dostępnymi na rynku elementami. Zaawansowane maszyny do układania komponentów wykorzystują automatyczne systemy wizyjne do dokładnego, powtarzalnego i niezawodnego określania pozycji PCB względem środka układu współrzędnych przestrzeni roboczej. W produkcji seryjnej należy zatem przewidzieć zastosowanie znaczników (markerów) optycznych, które mają zwykle postać okrągłego pola o średnicy od 1 do 3 mm, pozbawionego soldermaski i wyposażonego w okrągły, niewiercony pad o średnicy dostosowanej proporcjonalnie do wymiarów markera (rysunek 19). Rozwiązanie takie znacząco zwiększa dokładność pozycjonowania, choć niektóre maszyny są w stanie poradzić sobie z określeniem współrzędnych tylko i wyłącznie na podstawie obrazu mozaiki PCB jako takiej.

- Poszerzanie ścieżek przy wejściu do padów – technika ta, zwana popularnie teardrops, polega na (zwykle automatycznym) dodawaniu segmentów linii lub łuków do ścieżek w taki sposób, że ścieżka w miejscu połączenia z padem lub przelotką łagodnie się poszerza. Oprócz mechanicznego wzmocnienia (co ma znaczenie przy podłączaniu cienkich ścieżek do relatywnie dużych padów) rozwiązanie to pozwala zwiększyć odporność na powstawanie pułapek kwasowych, ale przede wszystkim zmniejsza prawdopodobieństwo powstania nieakceptowalnych uszkodzeń ścieżek w przypadku niezbyt dokładnego trafienia wiertłem w środek padu/przelotki (rysunek 20).

Wymogi techniczne producentów PCB

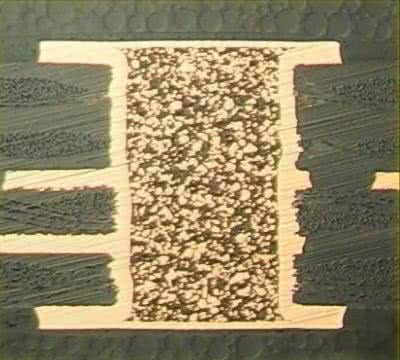

Niezwykle ważnym czynnikiem wpływającym na zgodność projektu PCB z wymogami podejścia DFM jest zweryfikowanie zgodności reguł projektowych, ustawionych w środowisku EDA, z możliwościami technologicznymi współpracującej z przedsiębiorstwem fabryki PCB. Właściwe ustalenie minimalnych rozmiarów pierścieni oraz średnicy wierceń padów THT i przelotek jest konieczne z uwagi na ograniczoną dokładność wiercenia. Otwór w żadnym przypadku nie powinien wykraczać poza krawędź padu znajdującego się na jednej z zewnętrznych powierzchni płytki drukowanej bądź na którejkolwiek z warstw wewnętrznych – ani nawet być nazbyt do niej zbliżony. Choć wymogi minimalnych średnic otworów i pierścieni padów/przelotek, określane przez zaawansowanych producentów, dotyczą innych aspektów technologii produkcji PCB, to w przypadku firm dysponujących mniej dokładnym wyposażeniem nadal można spotkać się z przypadkami, w których otwór jest wyraźnie przesunięty względem środka padu. Możliwości technologiczne limitują także osiągalne odstępy izolacyjne, minimalne szerokości ścieżek czy też odstępy otwór/otwór oraz otwór/krawędź PCB. Podobnie od jakości procesu nakładania soldermaski zależy minimalna jej szerokość i powtarzalność w newralgicznych miejscach płytki – głównie pomiędzy wyprowadzeniami układów scalonych. W każdym przypadku należy zatem – jeszcze przed oficjalnym zleceniem produkcji – dwukrotnie upewnić się, że dokumentacja wysyłana do producenta mieści się w zakresie wykonalności danej fabryki.

Podsumowanie

Zaprezentowane w artykule wytyczne stanowią zbiór praktycznych porad dla projektantów elektroniki – mamy nadzieję, że pozwolą one usystematyzować posiadaną wiedzę w zakresie DFM, a także ułatwią zwrócenie uwagi na najczęściej występujące problemy. Każdy inżynier powinien jednak samodzielnie skompletować własną checklistę, obejmującą – oprócz aspektów wymienionych w artykule – także szereg innych zagadnień, charakterystycznych dla danej branży, sposobu współpracy biura projektowego z producentami kontraktowymi czy też unikalnych doświadczeń pozyskanych z poprzednich projektów.

inż. Przemysław Musz, EP

[1] Przykładowe oznaczenia, na jakie można trafić w bazach dostawców i producentów elementów elektronicznych, to NRND (not recommended for new designs), OBS (obsolete) czy też EOL (end of life).

Zaloguj

Zaloguj