Silniki krokowe są coraz chętniej stosowanymi podzespołami. Ich pierwszorzędne zalety to możliwość uzyskiwania dowolnie małych prędkości obrotowych wału oraz precyzja ustawiania jego położenia.

Istotną wadą jest skomplikowane zasilanie ich cewek. Częściej wykorzystywane są silniki tzw. bipolarne, ponieważ pozwalają na zwiększenie uzyskiwanego momentu obrotowego o ok. 30...40% w stosunku do silników unipolarnych o tych samych gabarytach, które są za to prostsze w sterowaniu.

Prezentowane urządzenie realizuje podstawową funkcję kontrolera, jaką jest odpowiednie sterowanie wejściami układów wykonawczych. Tymi układami są mostki H (lub układy spełniające podobną rolę), ponieważ w procesie komutacji konieczna jest okresowa zmiana polaryzacji cewek silnika (stąd nazwa: bipolarny).

Zasada działania

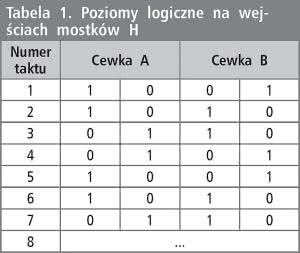

Analizując kierunki przepływu prądu w cewkach silnika można zauważyć, jakie są konieczne poziomy logiczne na wejściach mostków H, wymagane do prawidłowego zasilenia cewek bipolarnego silnika krokowego, a jednocześnie niepowodujące zbędnej komplikacji układu sterowania. Poziomy te zawiera tabela 1.

Wynika z niej, że potrzebne są dwa przebiegi prostokątne o tym samym okresie, ale przesunięte względem siebie o 90°. Do wykonania owego przesunięcia zostały zaprzęgnięte dwa przerzutniki typu D - łącznie, układ może się znaleźć w czterech możliwych stanach, zatem dwa jednobitowe elementy pamiętające są tutaj wystarczające. Po czterech okresach sygnału zegarowego, układ powraca do stanu wyjściowego i rozpoczyna pracę od nowa. Elementy kombinacyjne, okalające przerzutniki, mają na celu wprowadzenie dodatkowych funkcji: umożliwianie zmiany kierunku obrotów wirnika oraz jednoczesną dezaktywację wszystkich wyjść.

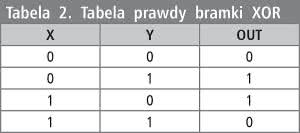

Tabela 2 jest tablicą prawdy bramki logicznej typu XOR. Jeżeli na jedno z wejść zostanie podane logiczne "0", wówczas wyjście jest kopią stanu logicznego drugiego wejścia. W drugim przypadku, po podaniu na stałe logicznej "1", wyjście jest negacją drugiego wejścia. Bramka ta zostanie wykorzystana jako "sterowany negator", służący zmianie kierunku obrotów. Dokładniej rzecz ujmując, za jej pomocą zostaje zmieniony znak fazy określającej przesunięcie między dwoma sekwencjami sygnałów sterujących: z +90° na -90°.

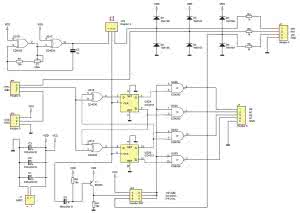

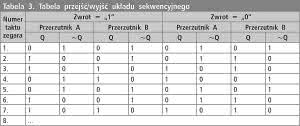

Dodatkowo, wiedząc, iż rolą przerzutnika typu D jest powtarzanie na wyjściu Q poziomu logicznego, który w momencie nadejścia zbocza sygnału zegarowego znajdował się na wejściu D, można prześledzić obieg stanów logicznych w tym układzie. Tabela 3 zawiera taki przykład - polecam samodzielną analizę na podstawie schematu ideowego z rysunku 1.

Opis układu

Schemat ideowy można podzielić na następujące bloki:

- układ sekwencyjny generujący ciągi bitów,

- lokalny generator sygnału zegarowego,

- układ sterowania zasilaniem cewek,

- bufory wyjściowe,

- obwody zabezpieczające wejścia sygnałów sterujących.

Działanie tego nieskomplikowanego układu sekwencyjnego polega na wytwarzaniu czterobitowych ciągów podawanych na wyjścia sterujące cewkami i zostało szczegółowo omówione we wstępie teoretycznym. Dodać należy, że został on zbudowany na przerzutnikach zawartych w układzie CD4013. Wynika z tego, iż ich zadziałanie odbywa się na narastającym zboczu sygnału zegarowego, co ma znaczenie przy podawaniu zewnętrznego sygnału taktującego. Bramki XOR pochodzą z układu CD4030.

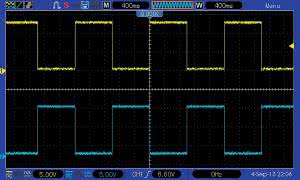

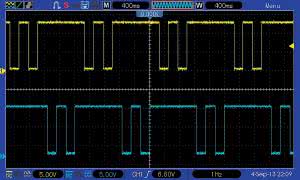

Rysunek 2. Przebiegi napięć na wyjściu sterującym jedną cewką silnika przy uaktywnionym wyłączaniu cewek

Lokalny generator sygnału zegarowego oferuje możliwość wprawienia silnika w ruch w sytuacji, gdy nie zachodzi konieczność taktowania go z zewnętrznego, dokładnego źródła. Taka sytuacja może mieć miejsce np. w czasie testów. Wykonano go z dwóch pozostałych bramek XOR pełniących rolę negatorów. Zakres częstotliwości generowanego sygnału zegarowego zawiera się w przedziale od ok. 1 Hz do ok. 29 Hz przy zasilaniu napięciem 12 V. Regulacji dokonuje się potencjometrem P1. Rezystor R1 ustala górną częstotliwość, a rezystancja ścieżki P1 - dolną.

W roli buforów wyjściowych zastosowano bramki NAND z układu CD4093. Jedno wejście każdej z nich jest sterowane przez wyjście przerzutnika, zaś drugie wejście umożliwia sterowaniem przepływu sygnałów sterujących.

Analiza tabeli 4, będącej tabelą prawdy bramki NAND, potwierdza taką możliwość. Została ona tak ułożona, aby była widoczna rola wejścia X. Gdy jest ono ustawione, wówczas na wyjściu występuje zanegowany stan wejścia Y. Jeżeli jednak wejście X zostanie wyzerowane, wtedy wyjściu bramki występuje poziom wysoki, niezależnie od stanu logicznego na wejściu Y.

Właśnie tę cechę wykorzystano do wyłączania uzwojeń silnika: podanie "0" na wejścia wszystkich bramek skutkuje ustawieniem ich wyjść. Mostki H, które zasilają cewki silnika, podadzą na obydwa zaciski tych cewek jednakowy potencjał - nie jest ważne, czy będzie on zbliżony do dodatniego, czy do ujemnego bieguna zasilania.

Dzięki temu, na cewce nie występuje różnica potencjałów, co doprowadza do braku przepływu prądu. Z drugiej zaś strony, nie ma możliwości pojawienia się stanu nieustalonego na wejściu mostka H, jak mogłoby to mieć miejsce w przypadku zastosowania np. kluczy analogowych.

Ten sterownik wyposażono również w bardzo prosty układ sterujący zasilaniem cewek silnika krokowego. W przypadkach, gdy nie jest potrzebny pełny moment obrotowy, za to jest pożądana redukcja pobieranej mocy i wydzielanego w uzwojeniach ciepła, można wyłączać owe uzwojenia. Zrealizowany został na tranzystorze T1 i kilku elementach biernych wokół niego.

Kondensator C4 i rezystor R2 tworzą obwód różniczkujący sygnał taktujący przerzutniki. Jednocześnie rezystor R2 służy do polaryzacji bazy tranzystora tak, aby był on normalnie w stanie wyłączonym, dzięki czemu poziom logiczny wyjścia jest niski i zmienia się na wysoki w momencie nadejścia zbocza opadającego oraz utrzymuje się niedługo po nim.

Wpływ takiego rodzaju sterowania jest widoczny na rysunku 2, który pokazuje przebiegi napięć sterujących jednym mostkiem H po zastosowaniu tej prostej metody redukcji poboru prądu: przez większość czasu cewka jest wyłączona (takie same poziomy logiczne na wyjściach) i załączana jest w momencie wykrycia kolejnego okresu sygnału zegarowego. Rysunek 3 obrazuje, dla porównania, to samo wyjście, lecz bez "przerywacza", z cewkami stale uruchomionymi. Oscylogramy zostały rozsunięte w pionie, aby nie nakładały się na siebie.

Sterownik pozwala na sterowanie silnika za pomocą sygnałów zewnętrznych, które należy doprowadzić do złącza J2. Wymagane sygnały to:

- sygnał zegarowy (doprowadzenie takt),

- sygnału zmieniającego kierunek obrotów silnika (doprowadzenie kier),

- sygnału załączającego cewki (doprowadzenie ster).

Aby nie dopuścić do uszkodzenia układów CMOS, wejścia te zostały zabezpieczone diodami D1...D6. W przypadku zbyt wysokiego napięcia (przekraczającego poziom napięcia zasilania), przewodzi dioda dołączona katodą do szyny zasilającej. Z kolei, w przypadku przypadkowego podania napięcia ujemnego względem masy, przewodzi dioda włączona anodą do masy. Rezystory R4...R6 ograniczają prąd płynący przez diody.

Należy pamiętać, że wejścia układów CMOS mają bardzo dużą impedancję wejściową. Z tego powodu należy zadbać, aby żadne z nich nie było niepodłączone, ponieważ gromadzących się na wejściu ładunek wywołuje nieznany poziom logiczny.

Wykaz elementówRezystory: Kondensatory: Półprzewodniki: Inne: |

Montaż i uruchomienie

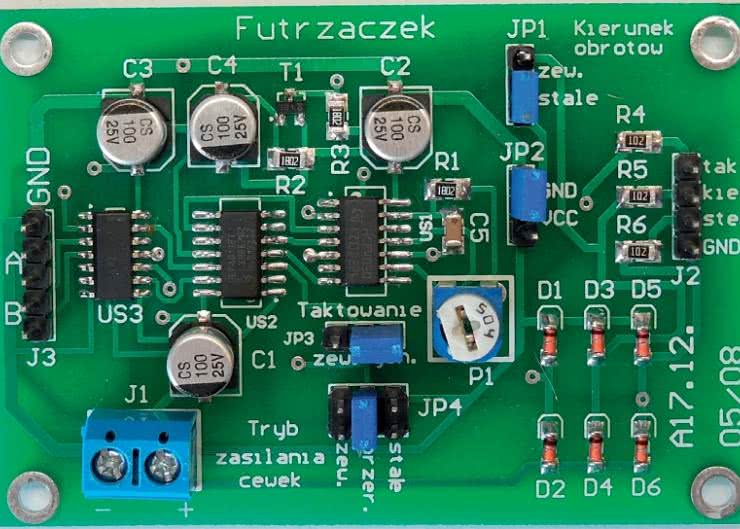

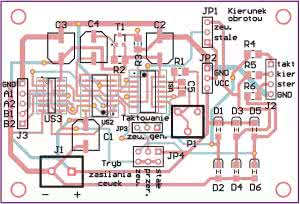

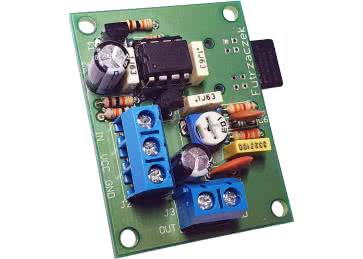

Układ został zmontowany na dwustronnej płytce drukowanej o wymiarach 7,5 cm×5 cm. Jej schemat montażowy pokazano na rysunku 4. Wszystkie elementy, poza potencjometrem i złączami, lutowane są powierzchniowo na górnej warstwie. Warstwa dolna zawiera jedynie ścieżki, nie znajdują się na niej żadne opisy ani podzespoły.

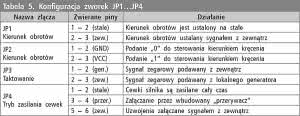

Prawidłowo polutowany układ jest od razu gotowy do pracy i nie wymaga żadnych regulacji. Jedyną czynnością przygotowawczą jest nałożenie czterech zworek na złącza JP1...JP4 zgodnie z tabelą 5.

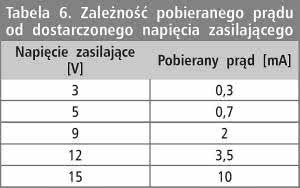

Sterownik należy zasilić napięciem stałym, dobrze filtrowanym, najlepiej stabilizowanym, z przedziału akceptowalnego przez układy CMOS rodziny 4xxx. Zależność poboru prądu przez układ modelowy od napięcia zasilania przedstawia tabela 6. Wartości te zostały zmierzone przy taktowaniu wewnętrznym generatorem z największą częstotliwością oraz przy braku jakichkolwiek doprowadzeń z zewnątrz.

Dwa słowa należą się również mostkom H, które będą działały z tym sterownikiem. Powinny one akceptować na swoich wejściach wszystkie możliwe stany logiczne (00, 01, 10, 11), bez ryzyka wystąpienia jakiegokolwiek uszkodzenia. W niektórych konfiguracjach mostków budowanych z elementów dyskretnych, zabronione jest jednoczesne załączanie dwóch wejść - nie można ich stosować z tym sterownikiem. Mostki wykonane jako układy scalone (np. L293, L298) są na to odporne.

Michał Kurzela, EP

Zaloguj

Zaloguj