Rekomendacje: użyteczny przyrząd, który przyda się w niejednym warsztacie domowym lub może być bazą dla podobnych konstrukcji.

Urządzenia dostępne w handlu przeważnie dysponują znacznie większą funkcjonalnością niż jest mi potrzebna na co dzień. Nie chciałem płacić za "nadmiarowe" funkcje, więc zdecydowałem się na samodzielne zbudowanie generatora korzystając z dostępnych rozwiązań układowych.

Zasada działania generatora DDS

Dość szybko okazało się, że jedynym słusznym rozwiązaniem sprzętowym w dzisiejszych czasach będzie zastosowanie specjalizowanego układu scalonego, który do generowania przebiegów wyjściowych używa techniki bezpośredniej syntezy cyfrowej DDS (Direct Digital Synthesis). Jest to dość prosta w założeniach metoda generowania przebiegów okresowych w sposób całkowicie cyfrowy (w zasadzie bez udziału elementów dyskretnych), która do tego celu wykorzystuje pamięć przechowującą wzorzec przebiegu sinusoidalnego, generator taktujący służący do taktowania licznika adresującego kolejne próbki sygnału oraz przetwornik C/A, który przesyłany ciąg próbek zamienia na analogowy sygnał wyjściowy. Uproszczony schemat blokowy generatora DDS pokazano na rysunku 1.

W tak nieskomplikowanym układzie generatora DDS wejściowy sygnał zegarowy o częstotliwości fWE "napędza" w sposób bezpośredni licznik adresowy, którego wyjścia adresują z kolei pamięć próbek sygnału wyjściowego. Wartości kolejnych próbek podawane są wejście przetwornika C/A, który zamienia je na wyjściowy sygnał analogowy. Sygnał ten, po odfiltrowaniu składowych harmonicznych, których obecność wynika z procesu przetwarzania cyfrowo-analogowego, może być wykorzystany jako "normalny" sygnał analogowy. W układzie takim częstotliwość wyjściowego sygnału analogowego fWY obliczyć możemy na podstawie zależności:

fWY = fWE/2n

gdzie n jest liczbą bitów licznika adresującego, czyli de facto jego rozdzielczością.

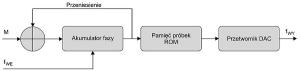

Łatwo zauważyć, że przedstawiona zależność znacznie ogranicza funkcjonalność tego typu konstrukcji, gdyż trudno jest uzyskać dokładną, żądaną częstotliwość przebiegu wyjściowego bez możliwości precyzyjnej regulacji częstotliwości źródła sygnału taktującego, co niejako niweczy sens budowania tego typu układu. Aby wyeliminować niedoskonałość takiego układu wprowadzono rozwiązanie, w którym licznik adresowy zastąpiono specjalnym modułem nazywanym akumulatorem fazy, dzięki czemu powstał generator, którego poglądowy schemat blokowy pokazano na rysunku 2.

Akumulator fazy, zastosowany w tym rozwiązaniu, jest pewną modyfikacją licznika adresowego, który wyposażono w mechanizm uwzględniający wartość kroku inkrementacji. Akumulator taki zlicza impulsy generatora taktującego, lecz za każdym razem, gdy wystawia na swoim wyjściu nową wartość adresu, uwzględnia specjalną wartość liczbową nazywaną słowem przestrajającym (tunning word) dodając ją do poprzednio wystawionej wartości adresu.

Innymi słowy, akumulator fazy pozwala na automatyczne pomijanie adresów próbek, które nie są wielokrotnością słowa przestrajającego, co jak łatwo zauważyć, przełoży się na wykres przebiegu wyjściowego sygnału analogowego zmieniając jego częstotliwość. W takim razie, dysponując akumulatorem fazy o dużej rozdzielczości (w układach dostępnych na rynku, minimum kilkadziesiąt bitów) jak i generatorem taktującym o częstotliwości kilkudziesięciu MHz, możemy uzyskać wyjściowy przebieg analogowy, którego częstotliwość regulować będzie można z dokładnością rzędu miliherców. W tego typu układzie częstotliwość tą możemy wyznaczyć wedłu wzoru:

fWY = M×fWE/2N

gdzie:

- N jest liczbą bitów rejestru akumulatora fazy, czyli de facto jego rozdzielczością,

- M jest wartością słowa przestrajającego.

W układach tego typu maksymalna, możliwa do uzyskania częstotliwość sygnału wyjściowego równa jest połowie częstotliwości sygnału generatora taktującego, zaś minimalna (dla M=1) wynika z ilorazu częstotliwości sygnału taktującego i rozdzielczości akumulatora fazy.

Jak widać, ta niewielka modyfikacja niesie za sobą ogromne możliwości, co skrzętnie wykorzystali producenci półprzewodników oferując szereg gotowych rozwiązań układowych w postaci scalonych generatorów DDS. Bodajże największą paletę scalonych generatorów tego typu udostępnia firma Analog Devices, w której asortymencie znajdują się rozwiązania różniące się zarówno rozdzielczością akumulatora fazy, rozdzielczością samej pamięci próbek, maksymalną wartością częstotliwości sygnału taktującego jak i dostępnymi typami wyjściowych przebiegów analogowych.

Dzięki takiej polityce, tego znanego producenta półprzewodników, możemy wybrać element, który w 100% spełnia wymagania docelowej aplikacji jak i uprości jej budowę. Jako, że nasze urządzenie w założeniu dysponować ma ograniczoną funkcjonalnością i charakteryzować się prostotą obsługi i implementacji, do jego budowy wybrano scalony generator DDS o symbolu AD9850.

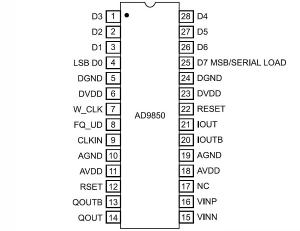

Jest to dość popularny element, który umożliwia zbudowanie generatora sygnałowego przebiegu sinusoidalnego i prostokątnego o maksymalnej częstotliwości rzędu 60 MHz, cechujący się ogromną prostotą implementacji. Ponadto, co nie jest bez znaczenia, gotowe moduły wyposażone we wspomniany układ jak i scalony generator kwarcowy o częstotliwości wyjściowej 125 MHz, bez problemu można nabyć na portalach aukcyjnych w bardzo przystępnej cenie, częstokroć kilkukrotnie niższej aniżeli cena samego układu scalonego kupowanego u dystrybutora półprzewodników, co w zasadzie trudno logicznie wytłumaczyć. Układ AD9850 charakteryzuje się następującymi, wybranymi cechami funkcjonalnymi:

- Maksymalna częstotliwość sygnału taktującego 125 MHz.

- Rozdzielczość regulacji 0,0291 Hz (@125 MHz).

- 32-bitowe słowo przestrajające.

- Wbudowany, wysokiej jakości, 10-bitowy przetwornik C/A z możliwością regulacji maksymalnej wartości prądu wyjściowego (wyposażony w wyjście prądowe).

- Wbudowany, szybki komparator dający możliwość generowania sygnału prostokątnego o regulowanym wypełnieniu.

- Możliwość regulacji fazy sygnału sinusoidalnego z krokiem 11,25°.

- Prosty, równoległy i szeregowy interfejs sterujący.

- Szeroki zakres napięcia zasilającego (3.3...5 V).

- Tryb o niskim poborze mocy Power-down.

Na rysunku 3 przedstawiono wygląd obudowy układu AD9850 wraz z rozmieszczeniem wyprowadzeń, zaś w tabeli 1 umieszczono pełnione przez nie funkcje.

Układ AD9850 z łatwością spełnia założenia budowy prostego generatora DDS charakteryzując się przy tym niezmierną prostotą aplikacji. Jako, że jego zasada działania jest zgodna z przedstawioną na rysunku 2 budową generatora DDS z akumulatorem fazy, nie będę powracał do podanych wcześniej informacji, a skupię się na zagadnieniach programowych, charakterystycznych dla tego elementu.

Jak wspomniano, chip AD9850 wyposażono w dwa interfejsy sterujące zapewniające możliwość komunikacji: równoległy i szeregowy. Z uwagi na fakt, iż sprzęg szeregowy wymaga zaangażowania wyłącznie 2 wyprowadzeń mikrokontrolera do nawiązania komunikacji (danych - w tym przypadku D7 i sygnału zegarowego - w tym przypadku W_CLK), właśnie ten interfejs wybrano jako medium współpracy ze sterownikiem nadrzędnym.

Aby to jednak było możliwe, producent układu wymaga zastosowania odpowiedniego rozwiązania sprzętowego: wyprowadzenia nr 3 i 4 układu AD9850 (D1 i D0) należy dołączyć do napięcia zasilającego, zaś wyprowadzenie nr 2 (D2) do masy, jak również zastosować należy specjalną sekwencję sygnałów sterujących (W_CLK i FQ_UD), dzięki czemu możliwa stanie się komunikacja we wspomniany wcześniej sposób. Sekwencję sygnałów sterujących niezbędną do aktywacji szeregowego interfejsu danych układu AD9850 przedstawiono na rysunku 4.

Po wstępnej inicjalizacji interfejsu sterującego, układ AD9850 gotowy jest na przyjęcie danych zmieniających jego stan pracy, a więc danych odpowiedzialnych za częstotliwość i fazę wyjściowego sygnału analogowego jak i kilku właściwości konfiguracyjnych. Wszystkie wspomniane wartości powinny zostać wysłane do naszego peryferium w takt sygnału zegarowego (W_CLK) szeregowej magistrali danych zgodnej ze znanym choćby ze świata mikrokontrolerów standardem zwanym SPI jako 40-bitowa ramka danych o konstrukcji pokazanej na rysunku 5.

Jak widać, samo przesłanie niezbędnej ramki danych sterujących do układu AD9850, nie zmienia parametrów wyjściowego sygnału analogowego wbudowanego przetwornika DAC do czasu wystąpienia rosnącego zbocza sygnału na wejściu aktualizacji słowa przestrajającego akumulatora fazy oznaczonym jako FQ_UD. Dopiero rosnące zbocze tego sygnału powoduje przepisanie przesłanej ramki danych do rejestrów układu DDS i odpowiednią zmianę parametrów sygnału wyjściowego. Na listingach 1 i listing 2 przedstawiono ciała funkcji odpowiedzialnych za inicjalizację szeregowej magistrali danych układu AD9850 jak i zmianę częstotliwości analogowego sygnału wyjściowego.

Warto podkreślić, iż dopuszczalna częstość aktualizacji częstotliwości wyjściowego sygnału analogowego układu AD9850 może sięgać nawet kilku milionów na sekundę, przez co można go z powodzeniem stosować w aplikacjach wymagających przemiatania pasma częstotliwościowego lub generowania modulowanych częstotliwościowo sygnałów analogowych o wysokich częstotliwościach nośnej.

Listing 1. Listing funkcji odpowiedzialnej za inicjalizację szeregowej magistrali danych układu AD9850

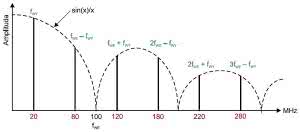

Za każdym razem należy mieć jednak na uwadze pewną właściwość układów tego typu, w których to sygnał analogowy jest generowany w sposób cyfrowy. Otóż, zgodnie z prawem Nyquista, w widmie sygnału utworzonego w ten sposób pojawią się również częstotliwości różne od oczekiwanej, tzw. aliasy, o całkiem pokaźnej amplitudzie, co niesie za sobą konieczność stosowania na wyjściu takich układów skutecznych filtrów dolnoprzepustowych eliminujących lub co najmniej ograniczających to niekorzystne zjawisko.

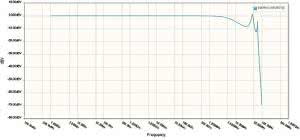

Częstotliwość tych niepożądanych sygnałów jest równa sumie i różnicy wielokrotności częstotliwości zegara taktującego akumulator fazy i częstotliwości sygnału wyjściowego, zaś ich amplituda wynika z przebiegu funkcji sin(x)/x. Poglądowy rysunek zależności amplitudy sygnału wyjściowego poszczególnych aliasów w funkcji ich częstotliwości dla częstotliwości wyjściowej fWY=20 MHz i częstotliwości generatora taktującego fWE=100 MHz pokazano na rysunku 6.

Rysunek 6. Poglądowy rysunek zależności amplitudy sygnału wyjściowego poszczególnych aliasów w funkcji ich częstotliwości

Wartość częstotliwości pierwszego aliasu równa fWE-fWY znajduje się dość blisko pożądanej częstotliwości wyjściowej i w krytycznych warunkach, gdy częstotliwość wyjściowa osiąga swoje maksimum, może się do niej bardzo zbliżyć, zaś jego amplituda może być tylko 3 dB niższa od amplitudy przebiegu o częstotliwości pożądanej. Wynika stąd potrzeba stosowania skutecznych filtrów dolnoprzepustowych jak i praktyczne ograniczenie maksymalnej częstotliwości wyjściowej tego typu generatorów do 1/3 częstotliwości zegara taktującego generator (fWE). Na tym zakończę tą część artykułu, gdyż w tej chwili dysponujemy już całą, niezbędną wiedzą by przejść do praktycznej realizacji generatora DDS.

Budowa

Listing 2. Listing funkcji odpowiedzialnej za zmianę częstotliwości analogowego sygnału wyjściowego układu AD9850

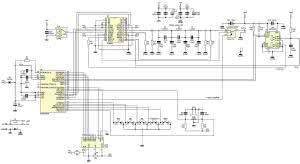

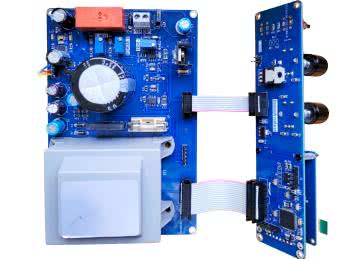

Schemat opisywanego generatora DDS pokazano na rysunku 7. Jest to nieskomplikowany system mikroprocesorowy, którego "sercem" jest nowoczesny mikrokontroler ATmega88, który za pomocą programowego interfejsu SPI (i dodatkowych sygnałów FQ_UD i RESET) steruje pracą generatora AD9850, zaś przy udziale sprzętowego interfejsu TWI steruje pracą scalonego, podwójnego potencjometru cyfrowego MCP4651 realizującego regulację wypełnienia wyjściowego sygnału prostokątnego oraz regulację amplitudy wyjściowego sygnału sinusoidalnego.

Mikrokontroler jest odpowiedzialny również za obsługę interfejsu użytkownika zbudowanego z użyciem kilku przycisków typu microswitch, enkodera obrotowego i alfanumerycznego wyświetlacza LCD o organizacji 2×16 znaków, jak również obsługę wysokiej jakości scalonego multipleksera 2 1 o oznaczeniu ADG719. Układ generatora AD9850 użyty tutaj został w swojej typowej aplikacji, w której sterowany przez mikrokontroler aktualizuje parametry sinusoidalnego przebiegu wyjściowego dostępnego na jego wyjściu oznaczonym IOUT.

Sygnał prądowy z tego wyjścia podlega zamianie na sygnał napięciowy (rezystor R7) i jest doprowadzony do dolnoprzepustowego filtru eliptycznego 5-tego rzędu zbudowanego z elementów dyskretnych. Ten filtr zapewnia odpowiednie tłumienie sygnałów niepożądanych - jego charakterystykę częstotliwościową zamieszczono na rysunku 8.

Po odfiltrowaniu sygnału użytecznego, trafia on na jedno z wejść multipleksera analogowego ADG719 i jednocześnie (poprzez rezystor R9) na nieodwracające wejście wbudowanego w strukturę układu AD9850 komparatora analogowego. Wejście odwracające tegoż komparatora podłączono z kolei do rezystancyjnego dzielnika napięcia zbudowanego z rezystora R12 i jednego ze scalonych, cyfrowych potencjometrów liniowych znajdujących się w strukturze układu MCP4651.

W ten prosty sposób, na wyjściu komparatora (QOUT) wbudowanego w strukturę naszego generatora DDS otrzymujemy przebieg prostokątny o regulowanym - przez stosunek wartości wspomnianych rezystorów - wypełnieniu. Wyjście komparatora trafia na drugie z wejść multipleksera analogowego, co pozwala na wybór rodzaju sygnału, który wystąpi na wyjściu urządzenia (sinusoidalny/ prostokątny).

Drugi z wbudowanych w strukturę układu MCP4651 scalonych potencjometrów cyfrowych wykorzystano (w szereg z rezystorem R5) do regulacji maksymalnej amplitudy prądu wyjściowego układu AD9850 (podłączony do wejścia RESET), co przekłada się na regulację maksymalnej amplitudy napięcia wyjściowego sygnału sinusoidalnego. Dla poprawienia parametrów elektrycznych urządzenia i zminimalizowania wpływu części cyfrowej urządzenia na tor analogowy, zdecydowano o rozdzieleniu magistral zasilających poszczególne części jak i odpowiadających im obwodów masy.

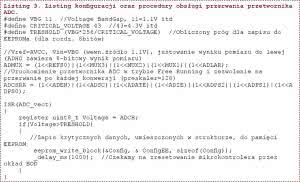

Generatora sDDS zapamiętuje swój stan pracy w nieulotnej pamięci EEPROM mikrokontrolera i po ponownym załączeniu generatora są wprowadzane ostatnio aktywne nastawy. Jako, że sam mechanizm zapewniający skuteczne a zarazem bezpieczne dla pamięci EEPROM mikroprocesora wykonanie tego zadania jest dość ciekawy, na koniec pokrótce go opiszę.

Mikrokontroler ATmega88 dysponuje nieulotną pamięcią EEPROM, jednak pamięć tego typu zapewnia ograniczoną do ok. 100 tysięcy liczbę gwarantowanych cyklów zapisu. Jak i kiedy, w takim razie, dokonywać zapisu niezbędnych wartości, by nie spowodować szybkiego uszkodzenia pamięci?

Odpowiedź wydaje się dość prosta, choć samo rozwiązanie całkiem interesujące. Niezbędne wartości konfiguracyjne "zebrane" w specjalną strukturę danych zapisywane są każdorazowo przy wyłączaniu urządzenia. W celu detekcji momentu wyłączania zastosowano wbudowany w mikrokontroler przetwornik A/C pracujący w trybie Free Running i monitorujący kilka tysięcy razy na sekundę napięcie Vbak, a więc napięcie zasilające wyłącznie mikrokontroler (po zaniku zasilania dioda D1 zapewnia separację zasilania mikrokontrolera od reszty urządzenia, a kondensator C4 zapewnia odpowiedni czas podtrzymania zasilania).

Co ciekawe, na pierwszy "rzut oka", nie wydaje się, by nasz sterownik w jakikolwiek sposób używał przetwornika A/C, gdyż żaden z kanałów wejściowych nie jest prze niego używany w tym celu. To prawda, patrząc na schemat układu i nie mając do dyspozycji listingu programu można by wysnuć taki wniosek. Jest jednak zgoła inaczej.

Przetwornik A/C mierzy specjalne, wewnętrzne napięcie odniesienia VBG=1,1 V (dla mikrokontrolera ATmega88), dzięki temu, iż wewnętrzny, analogowy multiplekser przetwornika może zostać właśnie w ten sposób ustawiony. Napięciem odniesienia jest z kolei napięcie zasilające mikrokontroler, czyli napięcie dostarczane na wyprowadzenie AVCC, czyli nasze Vbak. Spadek tego napięcia, podczas wyłączania zasilania, powoduje wzrost wartości wyniku przetwarzania według wzoru jak niżej (korzystamy z 8-bitowej rozdzielczości przetwornika):

VADC = (VBG×256)/Vbak

Procedura obsługi przerwania przetwornika A/C sprawdza każdorazowo czy nie został przekroczony zdefiniowany wcześniej próg obliczeniowy a jeśli ma to miejsce to inicjuje proces zapisywania danych konfiguracyjnych do wbudowanej pamięci EEPROM, po czym czeka, aż napięcie zasilania spadnie do poziomu wstrzymania pracy mikrokontrolera, które to jest dokonywane przez uruchomiony wcześniej układ BOD (typowo przy wartości 2,7 V).

Wspomniany próg zadziałania ustawiono na wartość 4,3 V, co oznacza, iż czas opadania napięcia zasilającego od 4,3 V do 2,7 V jest czasem, w którym mikrokontroler musi przeprowadzić zapis wszystkich danych konfiguracyjnych - w naszym przypadku 11 bajtów danych. Jak pokazały testy praktyczne, zastosowanie wspomnianego wcześniej rozwiązania sprzętowego (dioda D1 i kondensator C4) i mechanizmów programowych zapewnia 100% skuteczność zapisu danych z bardzo dużym marginesem czasowym. Listing zawierający rozkazy konfiguracji przetwornika A/C oraz procedury obsługi jego przerwania pokazano na listingu 3.

Wykaz elementówRezystory: (SMD 0805) Kondensatory: (SMD 0805) Półprzewodniki: Inne: |

Montaż i uruchomienie

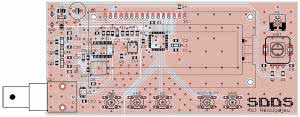

Schemat montażowy układu sDDS pokazano na rysunku 9. Zaprojektowano dla niego płytkę ze zdecydowaną przewagą elementów SMD po to, by całe urządzenie wymiarami swoimi nie przekraczało niezbędnego, minimalnego obszaru dla wykonania interfejsu użytkownika, co czyni je zdecydowanie mobilnym.

Tak jak wspomniano wcześniej, dla zminimalizowania zakłóceń na płytce urządzenia rozdzielono pola masy części cyfrowej i analogowej urządzenia, które to są ze sobą połączone wyłącznie w jednym miejscu obwodu drukowanego za pomocą zwory lutowniczej (poniżej dławika L2). Dla zmniejszenia pojemności pasożytniczych zastosowano szereg przelotek pomiędzy odpowiednimi polami masy po obu stronach obwodu drukowanego.

Z uwagi na zastosowanie elementów SMD, montaż najlepiej jest przeprowadzić z użyciem stacji lutowniczej wyposażonej w grot o niewielkiej średnicy, odpowiedniej jakości topników lutowniczych oraz mając pewne doświadczenie. Jak zwykle, montaż rozpoczynamy od przylutowania wszystkich układów scalonych oraz generatora kwarcowego SMD.

Następnie lutujemy diody, rezystory, kondensatory, pozostałe elementy bierne, gniazdo BNC a na końcu przyciski, enkoder oraz potencjometr do regulacji kontrastu wyświetlacza LCD (P1). Wyświetlacz LCD należy zamocować w odpowiedniej odległości od obwodu drukowanego, najlepiej za pomocą tulei dystansowych, wykorzystując przewidziane w tym celu otwory, zaś same połączenie należy wykonać przy użyciu listwy goldpin (gniazdo-wtyk) lub zwykłej taśmy wieloprzewodowej. Poprawnie zmontowany układ nie wymaga żadnych regulacji i powinien działać po włączeniu zasilania.

Ustawienia ważniejszych Fusbitów:CKSEL3...0: 0010 |

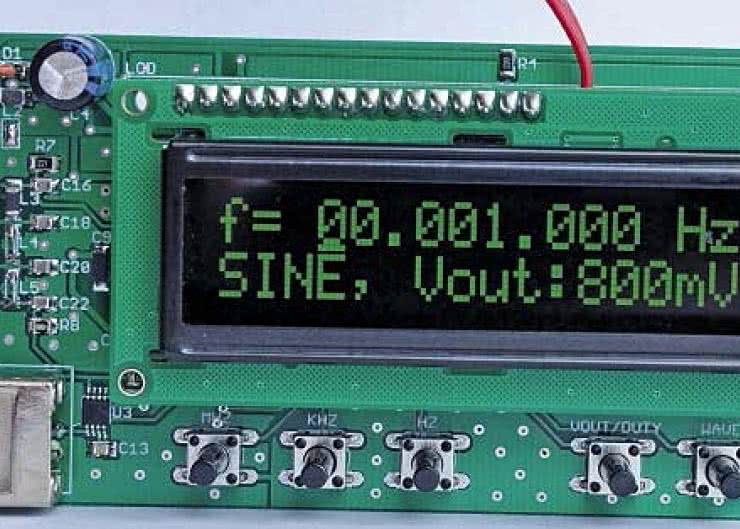

Obsługa

Jako, że generator sDDS jest z założenia przenośnym przyrządem warsztatowym, który może być obsługiwany w nieoptymalnych warunkach rzeczywistych, ergonomia i prostota obsługi układu oraz czytelność interfejsu użytkownika były najważniejszym kryterium przy konstruowaniu stosownych procedur sterujących.

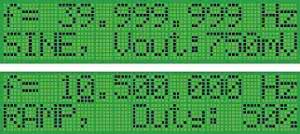

Zgodnie z tymi założeniami podstawowymi, na płytce sterownika przewidziano 5 przycisków sterujących dających bezpośredni dostęp do realizowanej przez nie funkcjonalności. Jak łatwo się domyślić, przyciski umownie oznaczone MHz, kHz i Hz służą do wyboru jednostek częstotliwości wyjściowej poddawanych regulacji, przy czym każdorazowe ich wciśnięcie powoduje przejście do kolejnego zakresu w ramach wybranej jednostki, co jednocześnie sygnalizowane jest przesunięciem kursora na wyświetlaczu LCD na odpowiednią pozycję.

I tak, dla przykładu, pierwsze wciśnięcie przycisku kHz powoduje przejście do regulacji (za pomocą enkodera) setek tysięcy kiloherców, następne, do regulacji dziesiątek tysięcy kiloherców a kolejne do regulacji tysięcy kiloherców itd. Ten sam mechanizm, co oczywiste, tyczy się przycisków MHz i Hz. Z kolei, przycisk VOUT/DUTY służy do regulowania napięcia wyjściowego analogowego sygnału sinusoidalnego, dostępnego na wyjściu urządzenia (w zakresie 0,15V...0,8 V z krokiem 0,05 V) lub do regulowania wypełnienia sygnału prostokątnego (w zakresie 10...90% z krokiem 5%), w zależności od trybu pracy urządzenia.

Przycisk WAVE służy do zmiany rodzaju sygnału wyjściowego (sinusoidalny/prostokątny), co jest sygnalizowane odpowiednim opisem na wyświetlaczu LCD. Na rysunku 10 pokazano wygląd interfejsu użytkownika układu sDDS w obu trybach pracy urządzenia.

Należy mieć zawsze na uwadze, że podane powyżej zakresy regulacji są orientacyjne, gdyż przy tego typu konstrukcji urządzenia zależne są w pewnym zakresie od częstotliwości wyjściowej, zwłaszcza w przypadku przebiegów o częstotliwościach powyżej 10 MHz. Jest to spowodowane faktem, iż zastosowany na wyjściu urządzenia pasywny filtr dolnoprzepustowy wprowadza tłumienie zależne od częstotliwości wyjściowej (co pokazano na rysunku 8), w związku z czym powoduje zaniżanie maksymalnego napięcia wyjściowego dla przebiegu sinusoidalnego.

Z drugiej strony, jako, że przebieg ten jest z kolei żródłem odniesienia dla komparatora "wytwarzającego" przebieg prostokątny, dla którego drugą z porównywanych wartości jest "sztywna" wartość napięcia z rezystancyjnego dzielnika napięcia, to również dla przebiegów prostokątnych o wysokich częstotliwościach zakres regulacji wypełnienia ulega ograniczeniu.

Dodatkowo, w przypadku przebiegów prostokątnych o częstotliwościach większych niż około 10 MHz, zniekształceniu ulegają zbocza sygnału, co jest spowodowane zarówno parametrami zastosowanego komparatora, jak i - a może przede wszystkim - projektem obwodu drukowanego, który w tego rodzaju układach powinien być wielowarstwowy, co jest jednym z zaleceń producenta układu. Mimo tych niedoskonałości, uważam, że przedstawiony generator sygnałowy z powodzeniem może być stosowany w pracy elektronika-amatora, jak również może stanowić bazę do udoskonaleń dla osób, które znacznie lepiej ode mnie poruszają się w arkanach techniki wysokich częstotliwości.

Robert Wołgajew, EP

Zaloguj

Zaloguj