Firma Analog Devices ma w ofercie wiele procesorów sygnałowych, a wśród nich jest bardzo interesująca rodzina Sigma DSP. Charakterystyczną cechą i jednocześnie ważną zaletą tej rodziny jest udostępniane za darmo oprogramowanie narzędziowe Sigma Studio (aktualnie wersja 3.9). Jest to środowisko graficzne, w którym "rysujemy" schemat z gotowych, parametryzowanych bloków funkcjonalnych. Zwalnia to z konieczności opanowywania języka programowania i zagłębiania się w tony dokumentacji. Dzięki niewielkiemu nakładowi sił potrzebnych na opanowanie "programowania" w Sigma DSP, możliwa jest realizacja nawet złożonych jednostkowych projektów w bardzo krótkim czasie, co do tej pory nie było możliwe, a procesory DSP przeznaczone były tylko dla wybranych.

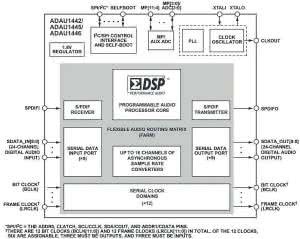

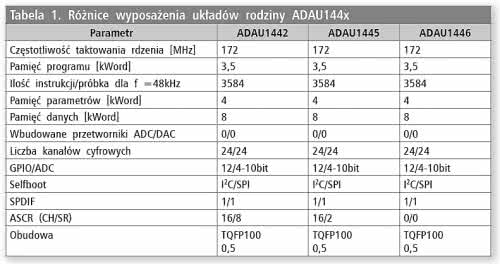

Rodzina ADAU144x składa się z trzech układów zgodnych ze sobą obudowami i wyprowadzeniami. Schemat blokowy układów ADAU144x przedstawia rysunku 1, różnice charakteryzujące układy zestawiono w tabeli 1.

W przeciwieństwie do ADAU1701 rodzina ADAU144x jest pozbawiona przetworników analogowo-cyfrowych i cyfrowo-analogowych. W zamian za to otrzymujemy rdzeń taktowany przebiegiem o częstotliwości 192 MHz i 24 kanały cyfrowe zdolne obrabiać sygnał 24-bitowy/192 kHz.

Układy mają trzy kanały wejściowe (SDATA IN0…2), trzy wyjściowe (SDATA OUT 0...2) oraz sześć dwukierunkowych (SDATA IN/OUT 3...8) umożliwiających współpracę z sygnałami I2S/TDM.

Układ ADAU144x ma wbudowany odbiornik i nadajnik pracujący w standardzie SPDIF, programowany generator sygnału zegarowego MCLK oraz rozbudowany interfejs GPIO z przetwornikiem A/C o 10-bitowej rozdzielczości.

Różnice pomiędzy układami ADAU1442, ADAU1445 i ADAU1446 polegają na uproszczeniu bloku ASRC (asynchroniczny konwerter częstotliwości próbkowania). Wbudowana krosownica sygnału FARM umożliwia elastyczne konfigurowanie sygnałów o różnych domenach zegarowych. Każdy z układów umożliwia współpracę z procesorem sterującym za pomocą interfejsu I2C czy SPI lub pracę samodzielną z pamięcią EEPROM w trybie SELFBOOT.

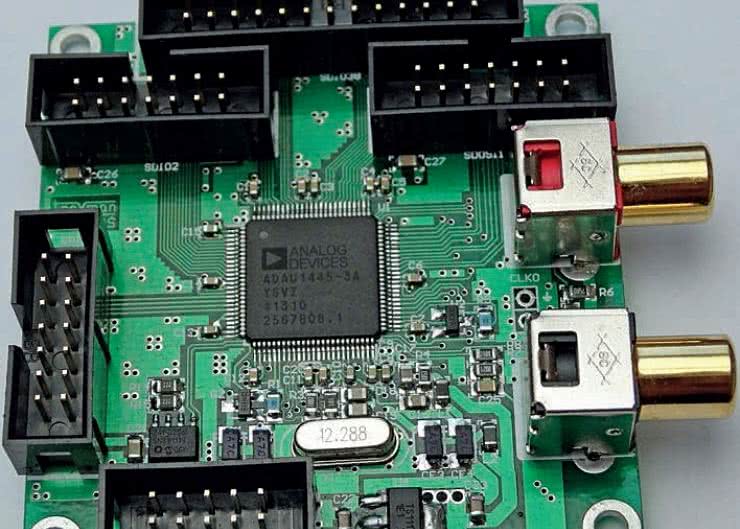

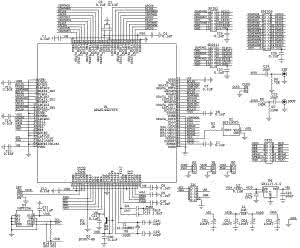

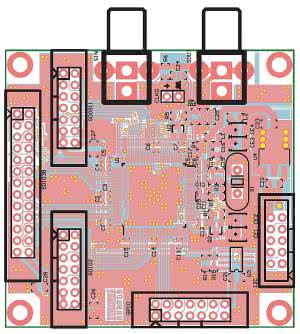

Schemat płytki Mega DSP pokazano na rysunku 2. Jej wyposażenie - ze względu na różnorodność aplikacji - zostało ograniczone do minimum. Płytka zapewnia zasilanie procesora DSP ze złącza programatora USBi (I2C): stabilizowane jest napięcie 3,3 V dla zasilania interfejsów IO-DSP (U4 i elementy towarzyszące) i 1,8 V (Q1/R1) dla zasilania rdzenia DSP. Obwody generatora i PLL mają w obwodzie zasilania dodatkowe filtry LC.

Ze względu na wysoką częstotliwość taktowania krytyczne jest odpowiednie filtrowanie zasilania. Firma Analog Devices zaleca stosowanie kondensatorów 0,1 µF przyłączonego do każdego doprowadzenia zasilania ADAU144x oraz 10 µF na szynach zasilania. W zaleceniach projektowych jest proponowane stosowanie płytki 4-warstwowej z wydzielonymi płaszczyznami masy i zasilania. Ze względu na wysoki koszt płytki wielowarstwowej, płytka zestawu została zaprojektowana jako dwustronna, ze szczególnym zwróceniem uwagi na sposób prowadzenia masy, filtrowanie zasilania i długość ścieżek, aby nie doprowadzić do znaczącego pogorszenia parametrów układu.

Zwora SBT umożliwia wprowadzenie ADAU144x w tryb SELFBOOT (SBT=3,3 V, 1-2), w którym konfiguracja i parametry są pobierane z pamięci EEPROM. W przeciwieństwie do ADAU1701, nie ma możliwości zapisu zwrotnego (WriteBack), więc wszystkie dane zapisane przez użytkownika zostają utracone po wyłączeniu zasilania. Możliwa jest też współpraca z zewnętrznym procesorem poprzez interfejs I2C (SBT=GND, 2-3).

Układ U2 zapewnia poprawne zerowanie po włączeniu zasilania. Sygnały kanałów cyfrowych doprowadzone są do złącz SDI02 (wejściowe), SDO911 (wyjściowe) oraz SDIO38 (dwukierunkowe). Interfejs jest zgodny ze standardem CMOS 3,3 V. Do złącz SIN/SOUT typu RCA, poprzez obwody terminujące, doprowadzone są sygnały wbudowanego odbiornika/nadajnika SPDIF.

Na złącze GPIO wyprowadzone są sygnały interfejsu użytkownika. Układ jest taktowany za pomocą oscylatora 12,288 MHz dla częstotliwości próbkowania 48 kHz lub 11,2896 MHz dla 44,1 kHz (fs×256). Przebieg o częstotliwości kwarcu, pochodzący z wewnętrznego generatora, jest dostępny na złączu CLK0 i może być wykorzystany np. do taktowania zewnętrznych przetworników C/A.

Zwory M0/M1/M2 umożliwiają wybór mnożnika fs dla wewnętrznego układu PLL zgodnie z tabelą 2. (256×fs jest ustawione domyślnie). Przy tej częstotliwości taktowania, na jedną próbkę sygnału cyfrowego przypada 3584 możliwych do wykonania instrukcji programowych.

Rdzeń ADAU144x umożliwia pracę z podwójną lub poczwórną częstotliwością oscylatora, jednak wtedy proporcjonalnie zmniejsza się liczba instrukcji możliwych do wykonania podczas jednej próbki sygnału (dokładne opisy w karcie katalogowej).

Montaż

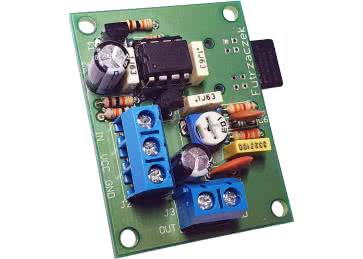

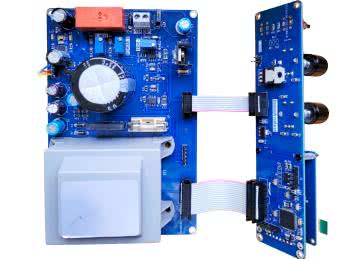

Płytka STK_ADAU144x "Mega DSP" jest zmontowany na niewielkiej, dwustronnej płytce drukowanej. Wszystkie sygnały GPIO oraz dla/z przetwornika są wyprowadzone na złącza szpilkowe umożliwiające wykorzystanie modułu jako "gotowego klocka DSP" we własnych projektach. Rozmieszczenie elementów przedstawia rysunek 3.

Sposób montażu jest klasyczny i nie wymaga opisu, należy tylko sprawdzić jego poprawność.

Bardzo istotne jest poprawne przylutowanie padu termicznego ADAU1442.

Przed uruchomieniem należy wybrać kwarc w zależności od częstotliwości próbkowania, skonfigurować układ taktowania DSP zworami M0…M2, (GND/V33/GND) oraz ustalić tryb pracy ADAU144x zworą SBT (V33 Selfboot), w zależności od aplikacji.

Moduł wymaga zasilania ze źródła o wydajności 5 V/500 mA doprowadzonego do złącza I2C (z zasilacza zewnętrznego w docelowej aplikacji lub z programatora USBi podczas testowania oprogramowania).

Po poprawnym montażu należy sprawdzić obecność napięć zasilających 3,3 V i 1,8 V oraz obecność sygnału zegarowego na złączu CLKO. Jeżeli wszystko jest w porządku można przejść do uruchomienia Sigma Studio w celu przygotowania aplikacji testowej.

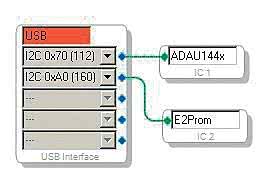

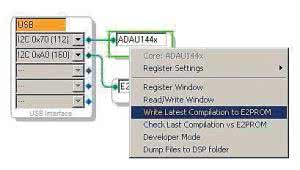

Do zaprogramowania ADAU144x konieczny jest interfejs USBi lub programator pamięci EEPROM (tylko w trybie Selfboot, rozwiązanie niewygodne, ale najtańsze). Po uruchomieniu środowiska w okienku konfiguracji, w obszar roboczy musimy przeciągnąć, połączyć i skonfigurować elementy USB, ADAU144x oraz E2PROM, zgodnie z rysunkiem 4.

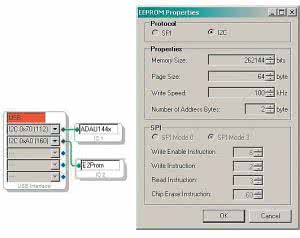

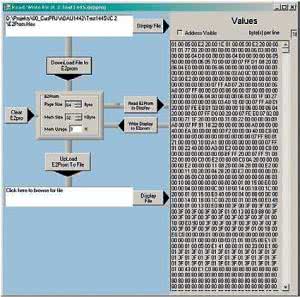

W zależności od zastosowanej pamięci EEPROM (w modelu 24FC/LC256), jest konieczne określenie jej wewnętrznej konfiguracji za pomocą zakładki IC2-E2Prom/Properties (rysunek 5).

Należy określić wielkości pamięci, rozmiaru bloku oraz częstotliwości magistrali I2C (dostępne od wersji 3.9 Sigma Studio), w przeciwnym wypadku programowanie EEPROM może być niemożliwe lub nieprawidłowe.

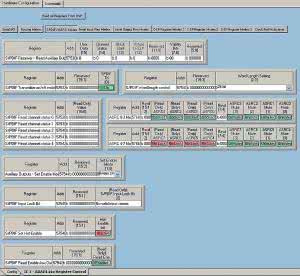

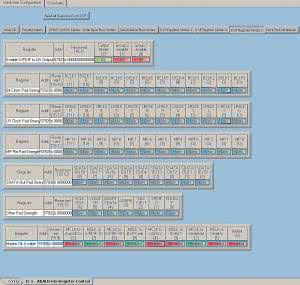

W roli aplikacji testowej wykorzystamy generator sygnału sinusoidalnego 1 kHz, ale wykorzystujący jako wyjście interfejs SPDIF (jest to blok niewystępujący w ADAU1701). Schemat blokowy aplikacji przedstawia rysunek 6. Konieczne jest ustawienie częstotliwości próbkowania na 44,1 kHz (kwarc 11,2896 MHz, fs×256). Teraz jest wymagane skonfigurowanie zegarów oraz interfejsu SPDIF procesora ADAU1442 (w modelu zastosowano tańszy ADAU1445, lecz nie ma to wpływu na działanie aplikacji testowej) zgodnie z rysunkiem 7 i rysunkiem 8.

Po zapisaniu i skompilowaniu projekt jest gotowy do zaprogramowania pamięci EEPROM (plik *.hex w katalogu IC2 projektu), sprawdzenia w czasie rzeczywistym za pomocą USBi lub zaprogramowania pamięci EEPROM poprzez USBi (rysunek 9 i rysunek 10).

Poprawność zaprogramowaniu warto sprawdzić za pomocą opcji "Check last compilation vs E2PROM", Po wyłączeniu zasilania można układ podłączyć do zewnętrznego przetwornika C/A, a jego wyjścia audio - uwaga na poziom sygnału, koniecznie należy wyciszyć wzmacniacz przed testem - do wzmacniacza. Po włączeniu zasilania powinien być słyszalny sinus 1 kHz w obu kanałach C/A. A skoro wszystko działa, to MEGA DSP można poddać znacznie bardziej wymagającym testom...

Adam Tatuś, EP

Zaloguj

Zaloguj