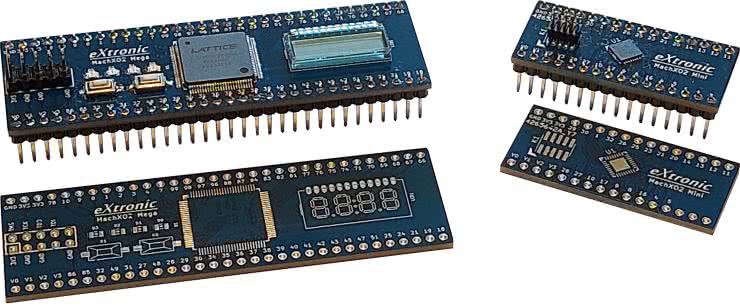

- moduł Mini z układem typu MachXO2-256 zmontowany na płytce w formacie obudowy DIL32 (600 milsów),

- moduł Mega z układem typu MachXO2-1200 zmontowany na płytce w formacie szerokiej obudowy DIL64 (900 milsów),

- zintegrowane wszystkie elementy niezbędne do działania zastosowanych układów FPGA,

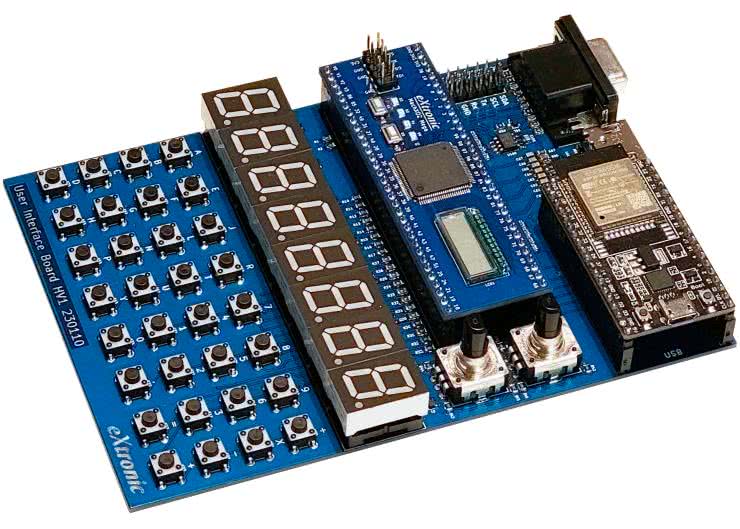

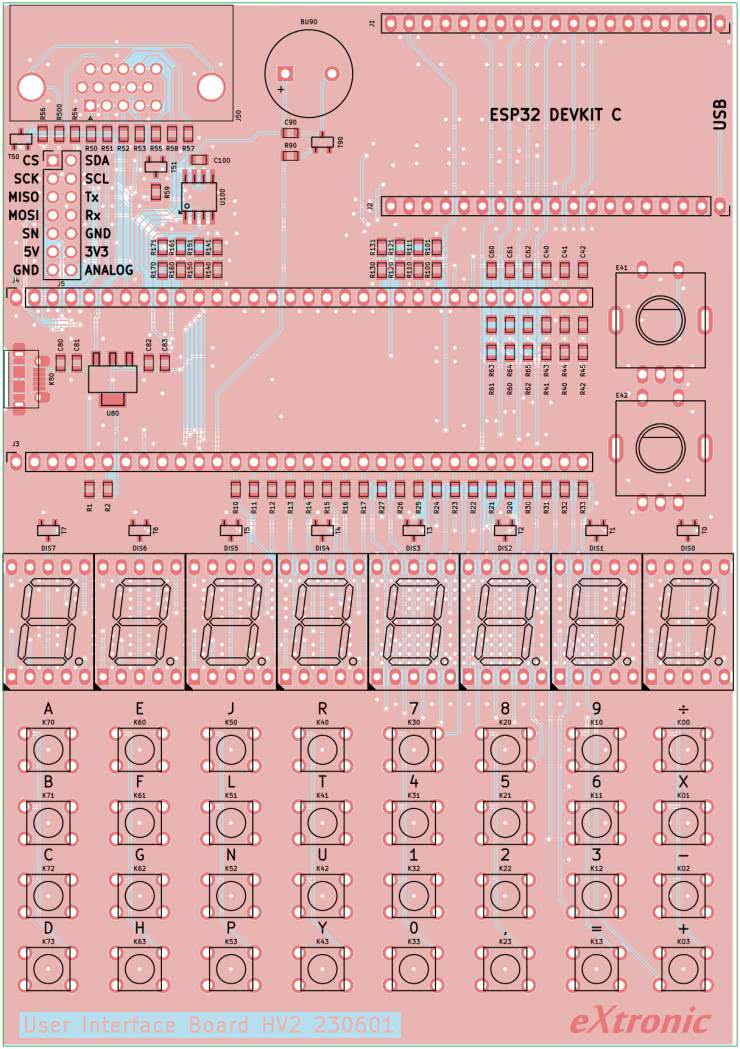

- moduł User Interface ułatwia podłączenie różnych peryferiów – przycisków, wyświetlaczy, enkoderów, modułu z ESP32 do płytki Mega.

MachXO2 Mini

Jest to nieskomplikowany moduł zawierający układ typu MachXO2-256 – najmniejszy, najprostszy i najtańszy układ FPGA z rodziny MachXO2. Choć jego zasoby są nieduże, może znaleźć zastosowanie w wielu prostych projektach. Dodatkowym plusem jest to, że występuje w łatwej do przylutowania obudowie QFN32. Ponadto układ zawiera wbudowaną pamięć Flash oraz generator sygnału zegarowego, a żeby rozpocząć pracę potrzebuje jedynie zasilania i niczego więcej.

Istnieje możliwość, by w module zastosować układ MachXO2-1200, który jest dostępny również w tej niewielkiej obudowie QFN32 i jest kompatybilny pod względem wyprowadzeń. Dzięki temu zyskamy dużo więcej zasobów logicznych.

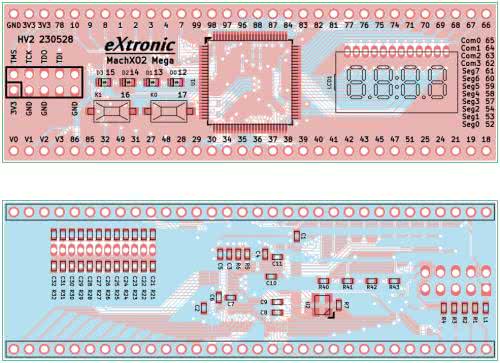

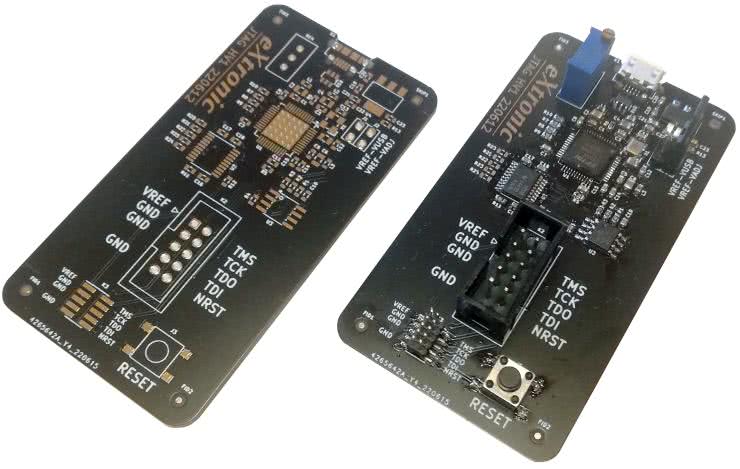

Zmontowany moduł Mini (wraz z omawianym w dalszej części artykułu modułem Mega) pokazano na fotografii 1.

Kształt i wymiary modułu odpowiadają obudowie DIL32. Dzięki temu możemy moduł łatwo połączyć z innymi elementami, umieszczając go na płytce stykowej lub na innej płytce z użyciem niedrogiej i łatwo dostępnej podstawki DIL32 o szerokości 600 milsów. W ten sposób moduł MachXO2 Mini da się łatwo podłączyć oraz wyciągnąć z układu bez konieczności lutowania/rozlutowywania – zupełnie tak, jak układ scalony w obudowie DIL32.

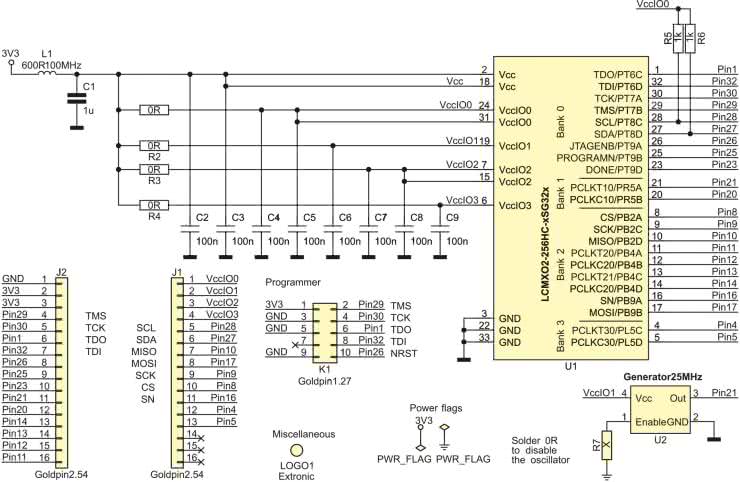

Budowa i działanie

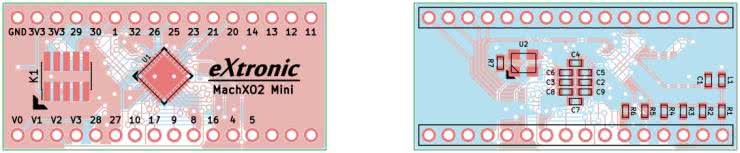

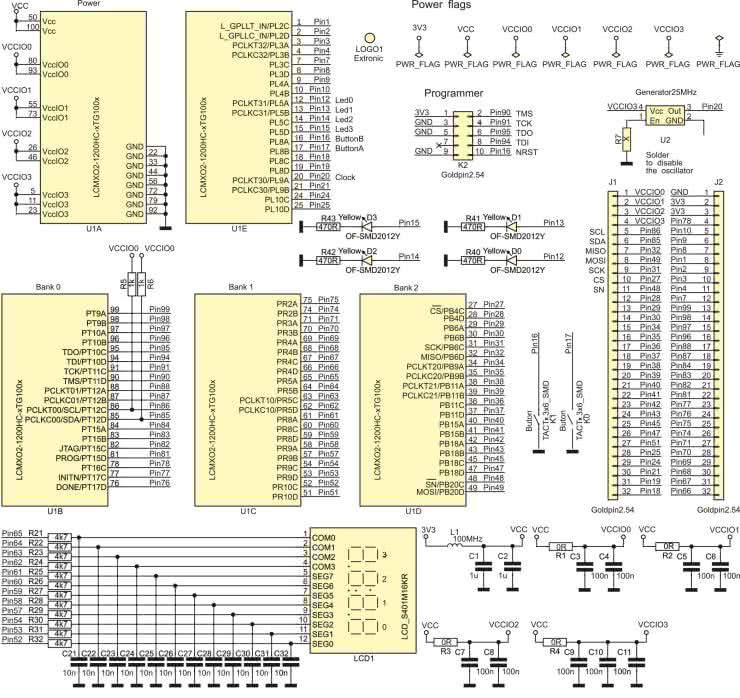

Schemat modułu Mini został pokazany na rysunku 1, natomiast schemat obwodu PCB pokazano na rysunku 2. Jest on niezwykle prosty. Zasilanie może być doprowadzone z programatora przy pomocy złącza K1 lub poprzez wyprowadzenia przeznaczone do zasilania dostępne na złączach krawędziowych J1 oraz J2.

Układy rodziny MachXO2 można zasilać na różne sposoby. Wyprowadzenia Vcc dostarczają zasilanie do rdzenia układu FPGA. W układach wersji HC (taka została zastosowana w module Mini) napięcie Vcc powinno wynosić 3,3 V lub 2,5 V. Wyprowadzenia VccIOn (gdzie n jest liczbą od 0 do 3) dostarczają napięcie do czterech banków wyprowadzeń IO. Każdy z tych banków może być zasilany napięciem o wartości od 1,14 V do 3,6 V. Dzięki takiemu rozwiązaniu, układ FPGA może pracować z peryferiami działającymi z różnymi napięciami zasilania i może funkcjonować jako translator napięć.

W module Mini domyślnie wszystkie wyprowadzenia Vcc oraz VccIOn połączone są ze sobą, czyli zasilane są tym samym napięciem. Jeżeli chcemy skorzystać z możliwości zasilania różnymi napięciami, należy odlutować rezystory o zerowej rezystancji R1...R4, aby odłączyć wybrane wyprowadzenie VccIO od Vcc, a następnie żądane napięcie należy dostarczyć poprzez wyprowadzenia 1...4 na złączu J1.

Koralik ferrytowy L1 oraz kondensatory C1...C9 pełnią funkcję filtrów zasilania. Rezystory R5 i R6 to pull-upy dla interfejsu I²C, który jest dostępny na pinach 27 i 28. Mowa tu o interfejsie I²C, który jest wbudowany w strukturę FPGA i pozwala oszczędzać uniwersalne zasoby logiczne. Oczywiście możemy napisać swój własny interfejs I²C w Verilogu lub VHDL i wtedy można korzystać z dowolnych wyprowadzeń.

Generator sygnału zegarowego wybudowany w strukturę FPGA ma niewielką dokładność. Można go stosować z powodzeniem do zadań, które nie wymagają precyzyjnego sygnału zegarowego, takich jak na przykład multipleksacja wyświetlaczy LED czy LCD. W przypadku bardziej wymagających aplikacji należy zastosować generator kwarcowy. Na płytce dostępny jest generator sygnału zegarowego o częstotliwości 25 MHz. Jeżeli ta częstotliwość nie odpowiada wymaganiom, można ją pomnożyć lub podzielić przy pomocy bloku PLL wbudowanego w FPGA. Generator jest cały czas włączony i dostarcza sygnał zegarowy do pinu 21. Jeżeli chcemy to wyprowadzenie użyć do innego celu, należy w miejscu R7 przylutować rezystor o zerowej rezystancji (lub drucik).

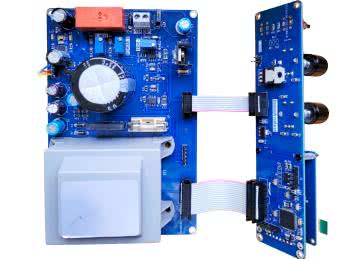

Mach XO2 Mega

Moduł Mega znajdzie zastosowanie w nieco bardziej zaawansowanych aplikacjach, gdzie płytka Mini nie jest wystarczająca. Schemat modułu Mega został pokazany na rysunku 3, a na rysunku 4 znajduje się schemat obwodu PCB. Kształt płytki odpowiada obudowie DIL64 o szerokości 900 milsów.

Budowa i działanie

Schemat jest dość podobny do schematu płytki Mini, więc omówimy tylko różnice między mini. Zastosowano układ FPGA to MachXO2-1200 w obudowie TQFP100. Jest on wyposażony w dużo więcej zasobów logicznych niż maluszek z poprzedniej płytki, a także ma zdecydowanie więcej wyprowadzeń.

W module znalazły się cztery diody LED oraz dwa przyciski. Jeden z nich podłączony jest do linii resetującej NRST połączonej do gniazda programatora. Ponadto płytka została wyposażona w mały wyświetlacz LCD, umożliwiający wyświetlanie czterech cyfr. Obsługa wyświetlacza LCD znacząco różni się od multipleksowanego wyświetlacza LED. Ten temat będzie omówiony dokładnie w 13 odcinku kursu.

User Interface Board

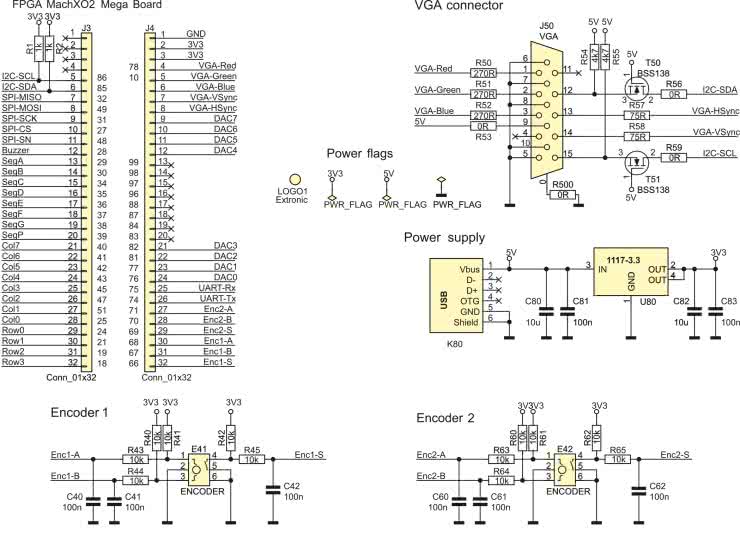

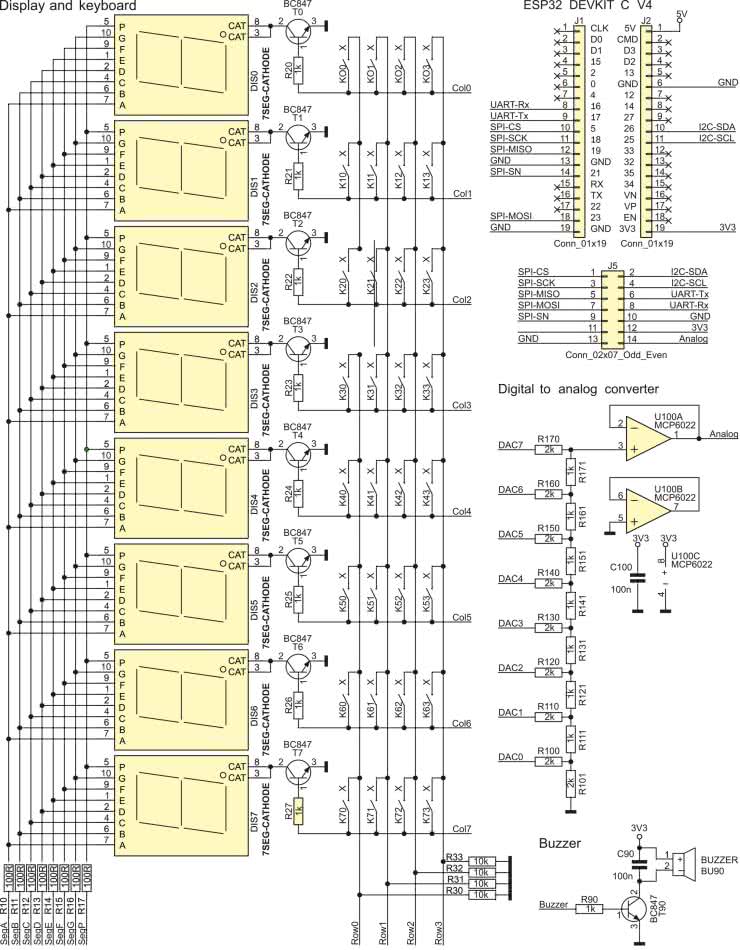

Moduł User Interface powstał, aby ułatwić podłączenie różnych peryferiów do płytki Mega – wystarczy ją umieścić w gnieździe J3 i J4 w taki sposób, jak pokazano na fotografii tytułowej. Korzystając z tej płytki można łatwo wykonać ćwiczenia opisane w kursie od odcinka 9. Płytka zawiera szereg różnych peryferiów, które będą omawiane w wielu odcinkach kursu.

Budowa i działanie

Schemat płytki User Interface pokazano na rysunku 5, a schemat obwodu PCB na rysunku 6. W centralnej części płytki umieszczono duży i czytelny wyświetlacz LED multipleksowany. Składa się z ośmiu wyświetlaczy 7-segmentowych ze wspólną katodą o szerokości 600 mils – czyli tych najbardziej popularnych, które są dostępne we wszystkich kolorach. Obsługa wyświetlacza tego typu została omówiona w 9 odcinku kursu.

Nieco poniżej widzimy klawiaturę matrycową, składającą się z 32 przycisków. Temat klawiatury został omówiony w 10 odcinku kursu. Połączenie wyświetlacza multipleksowanego z klawiaturą matrycową sprawia, że korzystając z zaledwie 20 wyprowadzeń FPGA możemy obsługiwać 8-cyfrowy wyświetlacz i 32 przyciski.

W lewym dolnym rogu schematu widzimy głośniczek BU90, sterowany poprzez tranzystor T90. Sposób generowania sygnałów dźwiękowych zostanie omówiony w 14 odcinku kursu.

Płytkę wyposażono w dwa enkodery obrotowe E41 oraz E42, które omówimy dokładnie w 15 odcinku kursu. Oba enkodery zostały połączone w taki sam sposób – daje to okazję, by utworzyć dwie instancję jednego modułu enkodera opisanego w języku Verilog. Enkoder ma wyjścia A i B, które dostarczają informacji o obracaniu pokrętła. Pokrętło pełni jednocześnie funkcję przycisku – wciśnięcie go powoduje zwarcie wyprowadzenia S do masy.

Rezystory R40, R41, R42 i odpowiednio R60, R61, R62 służą jako pull-upy, które mają zapewnić stan wysoki na wejściach FPGA w momencie, kiedy wewnętrzny mechanizm enkodera nie łączy wyjść A lub B z masą. To samo dotyczy wyjścia S. Pary rezystorów i kondensatorów R43, C40; R44,C41 oraz R45-C42 tworzą filtry dolnoprzepustowe, których zadaniem jest eliminacja drgań styków. Oczywiście wszystkie te rezystory i kondensatory można by pominąć, a zamiast nich zastosować wewnętrzne pull-upy wbudowane w FPGA, a drgania styków wyeliminować w taki sposób, jak to omówiono w 6 odcinku kursu – jednak wymagałoby to poświęcenia większej ilości zasobów logicznych układu FPGA.

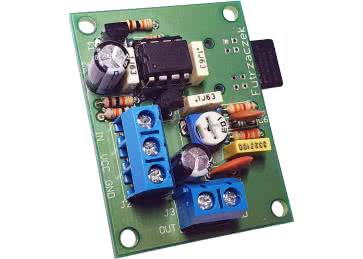

W prawym dolnym rogu schematu znajduje się 8-bitowy przetwornik cyfrowo-analogowy w postaci drabinki rezystorowej R-2R. Umożliwia wygenerowanie dowolnego napięcia od zera do napięcia zasilania 3,3 V z rozdzielczością 1/256, czyli 0,013 V. Wzmacniacz operacyjny U100A pracuje jako wtórnik napięcia. Został zastosowany z tego powodu, że drabinka R-2R ma dużą rezystancję i w rezultacie obciążalność wyjścia drabinki jest bardzo mała. Wtórnik napięcia ma wzmocnienie równe 1, czyli napięcie na jego wejściu i wyjściu jest takie samo, ale umożliwia pobranie dużo większego prądu niż ten, jaki można by pobrać z drabinki. Zastosowano układ MCP6022 – jest to tani wzmacniacz rail-to-rail ogólnego przeznaczenia dostępny w obudowach SO8 oraz DIL8. Wyjście Analog dostępne jest poprzez gniazdo J5 typu goldpin. Można je podłączyć na przykład do oscyloskopu.

W gnieździe J5 znajdziemy jeszcze kilka sygnałów związanych z interfejsami UART, SPI oraz I²C. Są one połączone zarówno do FPGA jak i do devboarda ESP32. Celem tego rozwiązania jest ułatwienie ćwiczeń z tymi interfejsami. Użytkownik może łatwo zaprogramować ESP32 przy pomocy języka C lub Python i komunikować się z FPGA. W gniazdo J5 można podłączyć analizator logiczny lub oscyloskop, aby podsłuchiwać i weryfikować czy komunikacja zachodzi prawidłowo. Alternatywnie, można nie umieszczać devboarda ESP32 i zamiast niego podłączyć kabelkami inną płytkę rozwojową. Ja gorąco polecam moduł ESP32 ponieważ jest tani i ma wielkie możliwości, a przy pomocy MicroPythona można bardzo łatwo i szybko napisać całkiem rozbudowany program.

Ostatnia rzecz wymagająca omówienia to gniazdo VGA. Dzięki niemu będziemy mogli podłączyć monitor. Wydawać się może, że standard VGA obecnie już jest wymarły i odszedł do lamusa. Jest w tym dużo prawdy, ale jest to standard bardzo prosty i świetnie nadaje się na początek zabaw z generowaniem obrazu w FPGA. Poza tym, dobrze jest opanować VGA przed próbą okiełznania HDMI, które jest bardziej skomplikowane.

Ponadto, mamy możliwość użycia pinów 12 i 15 złącza VGA, które zwykle są pomijane przez hobbystów. Pod tymi pinami kryje się interfejs I²C, pozwalający na identyfikację podłączonego monitora. Interfejs I²C w przewodzie VGA działa z napięciem 5 V, a MachXO2 działa przy napięciu 3,3 V. Z tego powodu zastosowano tranzystory MOSFET-N typu BSS138, które funkcjonują jako translatory napięcia. Jeżeli z jakiegoś powodu konieczne będzie odcięcie linii I²C od FPGA, należy wtedy odlutować rezystory zerowe R56 i R59.

To nie wszystko

Płytki Mega oraz Mini mogą być programowane przy pomocy programatora JTAG, który opisałem w EP 2022/09 – fotografia 2.

Zawiera on produkowany przez firmę FTDI układ scalony FT232H, który jest przejściówką USB/JTAG. Współpracuje z Lattice Diamond, Lattice Radiant, a także wieloma innymi rozwiązaniami open source, jak na przykład OpenOCD.

W dalszych planach jest opracowanie dodatkowych płytek, które umożliwiałyby użycie złącza HDMI, wyświetlacza LCD 14-segmentowego, a także płytek z mocniejszymi układami FPGA zgodnymi z User Interface Board.

Dominik Bieczyński

leonow32@gmail.com

https://ep.com.pl/projekty/projekty-ep/15365-niedrogi-programator-jtag-do-ukladow-fpga

Kurs FPGA:

https://ep.com.pl/kursy/15423-kurs-fpga-lattice-1-wstep

https://ep.com.pl/kursy/15444-kurs-fpga-lattice-2-pierwszy-projekt

https://ep.com.pl/kursy/15468-kurs-fpga-lattice-3-podstawy-jezyka-verilog

https://ep.com.pl/kursy/15515-kurs-fpga-lattice-4-generator-dzielnik-i-licznik

https://ep.com.pl/kursy/15555-kurs-fpga-lattice-5-ipexpress-i-inne-gotowce

https://ep.com.pl/kursy/15557-kurs-fpga-lattice-6-parametry-i-cwiczenia

https://ep.com.pl/kursy/15613-kurs-fpga-lattice-7-analizator-logiczny-reveal

https://ep.com.pl/kursy/15685-kurs-fpga-lattice-8-symulacja-w-eda-playground

https://ep.com.pl/kursy/15717-kurs-fpga-lattice-9-wyswietlacz-multipleksowany

https://ep.com.pl/kursy/15759-kurs-fpga-lattice-10-klawiatura-matrycowa-i-maszyna-stanow

Repozytorium modułów wykorzystywanych w kursie:

https://github.com/leonow32/verilog-fpga

- R1...R4: 0 Ω (SMD0603)

- R5, R6: 1 kΩ (SMD0603)

- R7: 0 Ω (SMD0603) – nie montować

- C1: 1 μF (SMD0603)

- C2...C9: 100 nF (SMD0603)

- U1: LCMXO2-256HC-xSG32x (QFN32)

- U2: generator 25 MHz (SMD 3,2×2,5 mm)

- L1: koralik ferrytowy 600 Ω @ 100 MHz (SMD0603)

- J1, J2: listwa goldpin 1×16, raster 2,54 mm

- K1: listwa goldpin SMD 2×5, raster 1,27 mm

- R1...R4: 0 Ω (SMD0603)

- R5, R6: 1 kΩ (SMD0603)

- R7: 0 Ω (SMD0603) – nie montować

- R21...R32: 4,7 kΩ (SMD0603)

- R40...R43: 470 Ω (SMD0603)

- C1, C2: 1 μF (SMD0603)

- C3...C11: 100 nF (SMD0603)

- C21...C32: 10 nF (SMD0603)

- D0...D3: dioda LED (SMD0805)

- U1: LCMXO2-1200HC-xTG100x (QFP100)

- U2: generator 25 MHz (SMD 3,2×2,5 mm)

- L1: koralik ferrytowy 600 Ω @ 100 MHz (SMD0603)

- LCD1: wyświetlacz LCD typu S401M16KR

- J1, J2: listwa goldpin 1×32, raster 2,54 mm

- K0, K1: mikroswitch SMD 3×6 mm

- K2: listwa goldpin SMD 2×5, raster 2,54 mm

- R1, R2, R20...R27, R90, R111, R121, R131, R141, R151, R161, R171: 1 kΩ (SMD0805)

- R10...R17: 100 Ω (SMD0805)

- R30...R33, R40...R45, R60...R65: 10 kΩ (SMD0805)

- R50, R51, R52: 270 Ω (SMD0805)

- R53, R56, R59, R500: 0 Ω (SMD0805)

- R54, R55: 4,7 kΩ (SMD0805)

- R57, R58: 75 Ω (SMD0805)

- R100, R101, R110, R120, R130, R140, R150, R160, R170: 2 kΩ (SMD0805)

- C40...C42, C60...C62, C81, C83, C90, C100: 100 nF (SMD0805)

- C80, C82: 10 μF (SMD0805)

- DISP0...DISP7: wyświetlacz 7-seg, 600 milsów ze wspólną katodą

- T0...T7, T90: BC847 (SOT23)

- T50...T51: BSS138 (SOT23)

- U80: stabilizator 1117-3,3 (SOT223)

- U100: MCP6022 (SO8)

- K10...K13, K20...K23, K30...K33, K40...K43, K50...K53, K60...K63, K70...K73, KO0...KO3 mikroswitch 6×6 mm

- E41, E42: enkoder obrotowy z przyciskiem

- K80: gniazdo micro USB

- J1, J2: gniazdo goldpin 1×19, raster 2,54 mm

- J3, J4: gniazdo goldpin 1×32, raster 2,54 mm

- J5: goldpin 2×5, raster 2,54 mm

- J50: złącze VGA kątowe

- BU90: głośniczek piezzo

Zaloguj

Zaloguj