- dwa tryby pracy: generator lub wobuloskop,

- wyjście sygnału sinusoidalnego i prostokątnego,

- regulacja częstotliwości w zakresie od 1 Hz do 40 MHz, z krokiem od 1 Hz do 1 MHz,

- regulacja poziomu wyjściowego sygnału sinusoidalnego za pomocą potencjometru,

- możliwość zastosowania jednego z dwóch dostępnych na rynku, gotowych modułów generatorów DDS z chipem AD9850.

Właściwości urządzenia

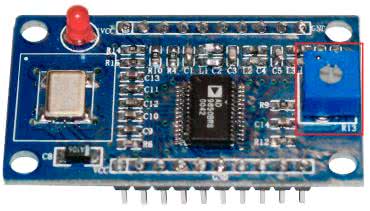

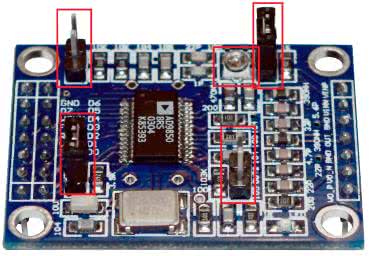

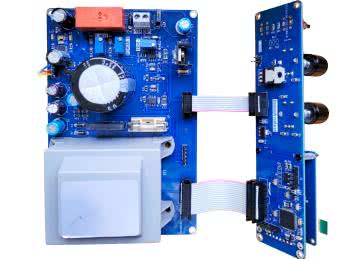

Opisany projekt generatora bazuje na gotowych modułach z popularnym układem scalonego syntezera DDS typu AD9850 produkcji Analog Devices (fotografie 1 i 2). Moduły te są taktowane zegarem 125 MHz, pochodzącym ze stabilizowanego termicznie generatora kwarcowego OCXO, umieszczonego na module. Znaczącym atutem tego właśnie projektu jest możliwość alternatywnego zastosowania jednego z dwóch wymienionych modułów DDS.

Urządzenie wyposażono we wzmacniacz szerokopasmowy dla analogowego sygnału sinusoidalnego, o wzmocnieniu napięciowym Ku=12 dB w 3-decybelowym paśmie przynajmniej do 30 MHz i impedancji wyjściowej 50 Ω. Także wyprowadzenie sygnału cyfrowego o poziomach logicznych 0/5 V ma bufor o impedancji wyjściowej 50 Ω. Bufor ten można programowo wyłączyć w celu obniżenia poziomu zakłóceń tła sygnału analogowego (sinusoidalnego). Zastosowanie zestandaryzowanej impedancji wyjściowej 50 Ω jest wygodne we współpracy z innymi urządzeniami (głównie radiokomunikacyjnymi) a także umożliwia poprawne przekazywanie sygnałów na zewnątrz urządzenia z użyciem przewodów koncentrycznych o tej samej impedancji falowej.

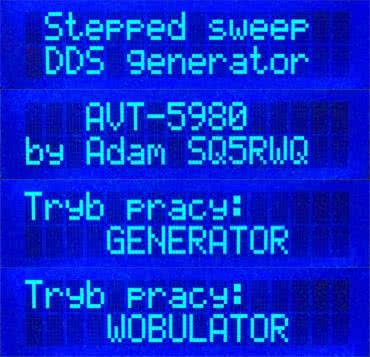

Po przejściu przez ekrany inicjujące pracę urządzenia (fotografia 3) przechodzimy do wyboru jednego z dwóch trybów jego pracy. Pierwszy z nich to zwykły tryb generatora. Częstotliwość roboczą Fg synchronicznych sygnałów: sinusoidalnego i prostokątnego, można regulować w zakresie od 1 Hz do 40 MHz z minimalnym krokiem dFg=1 Hz, przy czym dostępne kroki regulacji to: 1 Hz, 2 Hz, 5 Hz, 10 Hz, 20 Hz, 50 Hz, 100 Hz, 200 Hz, 500 Hz, 1 kHz, 2 kHz, 5 kHz, 10 kHz, 20 kHz, 50 kHz, 100 kHz, 200 kHz, 500 kHz oraz 1 MHz. Natomiast poziom wyjściowy sygnału sinusoidalnego można płynnie regulować za pomocą potencjometru obrotowego, umieszczonego na przednim panelu urządzenia. Jego wartość Vout (w jednostkach [Vp-p]) jest prezentowana na ekranie LCD 16×2, poniżej nastawionej częstotliwości pracy Fg.

Krok strojenia dFg można zmieniać na drugim ekranie obsługi generatora, dostępnym (cyklicznie) po naciśnięciu wbudowanego przycisku enkodera. Drugi tryb pracy urządzenia to tryb wobulatora. W tym trybie można ustawiać cztery parametry pracy:

- częstotliwość minimalną Fl,

- częstotliwość maksymalną Fh,

- krok strojenia (regulacji częstotliwości) dFg,

- szybkość (częstotliwość) wobulacji Fw,

- amplitudę sinusoidalnego napięcia wyjściowego Vout.

Częstotliwości graniczne oraz krok ich regulacji mogą przyjmować wartości analogiczne, jak w przypadku generatora, natomiast szybkość (częstotliwość) wobulacji Fw można regulować w zakresie od 4 do 10 Hz z krokiem 2 Hz. Wobulator pracuje poprzez cykliczne generowanie liniowo narastających 256 wartości częstotliwości z przedziału od Fl do Fh. Towarzyszy temu wytwarzanie narastającego liniowo, piłokształtnego sygnału odchylania poziomego dla oscyloskopu z wejściami i trybem pracy "X/Y". Sygnał ten może być używany także do wyzwalania (opadającym zboczem) procesu kreślenia przebiegu "Y" w oscyloskopach pozbawionych opcji pracy "X/Y". Częstotliwość Fw jest parametrem o tyle istotnym, że determinuje zarówno częstotliwość odświeżania kreślonej charakterystyki Y=f(X), jak i tempo pobudzania wejścia i skanowania wyjścia badanego układu. Ma to ogromne znaczenie, ponieważ czas ustalania odpowiedzi częstotliwościowej niektórych układów może być znaczny i - w związku z tym - wymagać bardzo powolnego skanowania wyjścia (podobne zagadnienie dotyczy sond analizujących poziom sygnału wyjściowego badanego układu). Sposób realizacji układowej i programowej oraz praktyczną obsługę zarówno generatora, jak i wobulatora opisano szczegółowo w dalszej części artykułu.

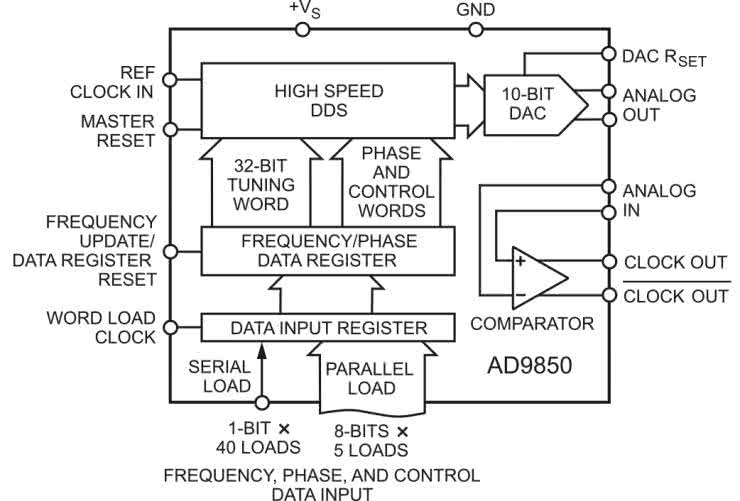

Syntezer DDS AD9850

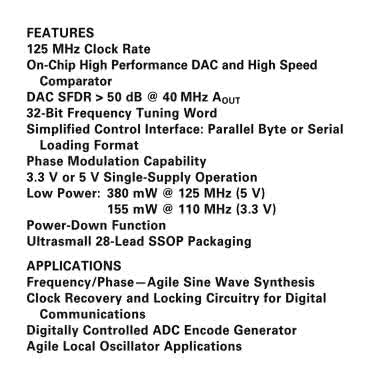

Podstawowe właściwości scalonego syntezera DDS (Direct Digital Synthesis) typu AD9850 prod. firmy Analog Devices zestawiono na rysunku 1 w formie listy zaczerpniętej z noty katalogowej tego układu. Jest on powszechnie stosowany od wielu lat m.in. w urządzeniach radiokomunikacyjnych, a swoją obecną popularność zawdzięcza głównie zastosowaniu w dwóch łatwo dostępnych modułach generatorów (fotografie 1 i 2), stosunkowo prostych do implementacji w przewlekanej technologii montażu THT.

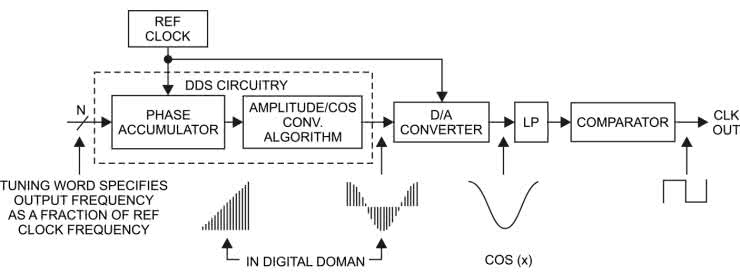

Chip działa w oparciu o zasadę odtwarzania próbek sygnału, pobieranych z predefiniowanej tablicy wartości sygnału sinusoidalnego, przez 10-bitowy przetwornik cyfrowo-analogowy DAC (Digital-to-Analog Converter). Przetwornik jest taktowany ze stałą częstotliwością, wytwarzaną przez umieszczony we wspomnianych modułach stabilizowany termicznie generator kwarcowy OCXO (Oven Controlled Crystal Oscillator), natomiast wartości próbek są wybierane na podstawie adresu wyliczanego w cyklicznie zwiększanym rejestrze, zwanym akumulatorem fazy. Układ scalony AD9850 może pracować z napięciami zasilania Vdd od 3,3 do 5 V, przy czym maksymalne częstotliwości taktowania Fs oraz wydzielane moce strat cieplnych Ptot wynoszą wtedy odpowiednio: 155 mW przy 110 MHz oraz 380 mW przy 125 MHz (wyczuwa się wówczas lekkie grzanie pracującego układu).

Deklarowana przez producenta wartość parametru SFDR (Spurious-Free Dynamic Range), oznaczającego stosunek amplitudy użytecznego sygnału wyjściowego do najsilniejszego sygnału zakłócającego (miara dokładności odwzorowania sygnału przez przetwornik DAC), przy częstotliwości generowanego sygnału sinusoidalnego równej Fc=40 MHz, jest lepsza od 50 dB, co należy uznać za wartość zadowalającą w większości zastosowań radioamatorskich. Trzeba tu jednak wyraźnie podkreślić, że przy tak małym stosunku częstotliwości generowanej Fc=40 MHz do częstotliwości próbkowania Fs=125 MHz, równym 0,32, próbkowanie odbywa się zbyt rzadko, by dokładność odwzorowania sygnału w dziedzinie czasu była wystarczająca dla większości zastosowań. W praktyce, stosując wyłącznie filtry dolnoprzepustowe LC, zaimplementowane we wspomnianych modułach DDS, jesteśmy w stanie uzyskać przebiegi sinusoidalne i prostokątne o jakości niebudzącej zastrzeżeń (przy wizualnej ocenie ich oscylogramów) oznaczającej współczynnik THD<5%, tylko w zakresie do kilkunastu MHz, czyli do około 10% częstotliwości Fs. Przy większych wymaganiach na czystość widmową generowanego przebiegu sinusoidalnego warto jest więc zastosować dodatkowe filtry dolno- lub pasmowo-przepustowe.

Zasadę działania syntezera zilustrowano schematami blokowymi na rysunkach 2 i 3. Częstotliwość wyjściową Fout określa formuła:

Fout = (ΔPhase × Fclk)/(232)

Parametr ΔPhase jest wartością 32-bitowego słowa, o które zwiększana jest wartość akumulatora fazy syntezera w każdym takcie zegara, natomiast Fclk jest wejściową częstotliwością referencyjną, taktującą układ (w tym wypadku jest to 125 MHz) i będącą jednocześnie częstotliwością próbkowania Fs dla przetwornika DAC. Krok fazy sygnału ΔPhase jest w każdym cyklu zegara taktującego dodawany do zawartości 32-bitowego akumulatora, z którego 10 najstarszych bitów jest podawanych na wejście adresowe tablicy LUT (Look-Up Table), odwzorowującej sygnał sinusoidalny, a następnie na wejście przetwornika cyfrowo-analogowego DAC.

Na wyjściu przetwornika DAC w modułach generatorów zaimplementowano eliptyczne filtry dolnoprzepustowe LC 7. rzędu, o paśmie przenoszenia ok. 42 MHz, które znacznie redukują pasożytnicze harmoniczne, pochodzące z próbkowania sygnału sinusoidalnego impulsami prostokątnymi. Należy tu zwrócić uwagę na fakt, że wraz ze wzrostem częstotliwości wyjściowej generatora DDS spada poziom podstawowego sygnału sinusoidalnego a wzrasta poziom zakłóceń harmonicznych.

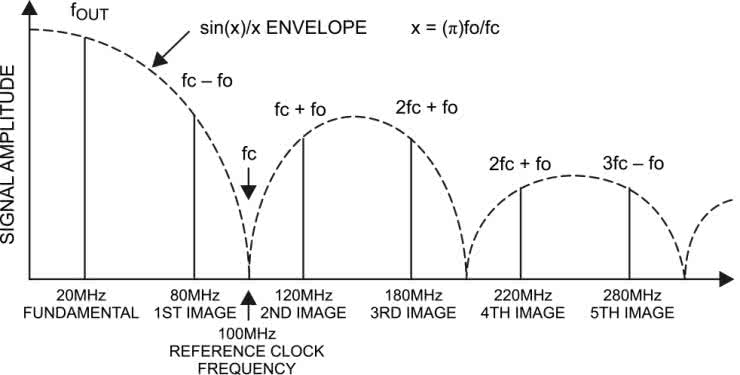

Zaczerpnięty z noty katalogowej układu AD9850 rysunek 4 pokazuje rozkład widmowy sygnału dla przykładowego przypadku syntezy z częstotliwością próbkowania fc=Fs=100 MHz i zaprogramowaną częstotliwością wyjściową fo=Fc=20 MHz. Jak widać, widmo to jest objęte obwiednią odwzorowującą funkcję:

|sinc(x)|=|sin(x)/x|

Taki kształt ma widmo zastosowanego tu próbkującego sygnału prostokątnego i, oprócz podstawowej harmonicznej fo, zawiera także liczne sygnały pasożytnicze o częstotliwościach n*fc±fo=80, 120, 180, 220, 280… MHz (efekt tzw. zjawiska aliasingu). Z wykresu można wywnioskować, że poziom tego sygnału pasożytniczego jest tym większy, im większy jest stosunek częstotliwości fo/fc (czyli Fc/Fs według przyjętych tutaj pierwotnie oznaczeń).

Odfiltrowany dolnoprzepustowo sygnał sinusoidalny jest podawany także na wejście wbudowanego w układ AD9850 komparatora, na którego wyjściu uzyskiwany jest sygnał prostokątny. W zastosowanych w projekcie modułach generatorów na jedno z wejść komparatora podawany jest stały sygnał referencyjny z potencjometru montażowego. Od jego wartości zależy współczynnik wypełnienia impulsów w sygnale prostokątnym.

Programowanie układu AD9850 może odbywać się metodą szeregową lub równoległą. Przy zastosowaniu szybszej metody równoległej aktywnie wykorzystywane są wyprowadzenia D0...D7 (programowanie odbywa się przez przekazanie do układu AD9850 pięciu 8-bitowych słów sterujących), natomiast przy programowaniu szeregowym do przekazania tych samych danych (40 bitów) wykorzystywane są tylko wejścia: W_CLK, FQ_UD, DATA oraz RESET. Przy zastosowaniu układu jako zwykłego generatora, stosunkowo wolno przestrajanego, w zupełności wystarczy powolniejszy transfer szeregowy, wymagający mniejszej liczby połączeń. Jakkolwiek sterowanie równoległe z natury będzie około 8-krotnie szybsze, co może być przydatne wtedy, gdy chcielibyśmy stosować układ DDS np. jako element modemu FSK czy PSK.

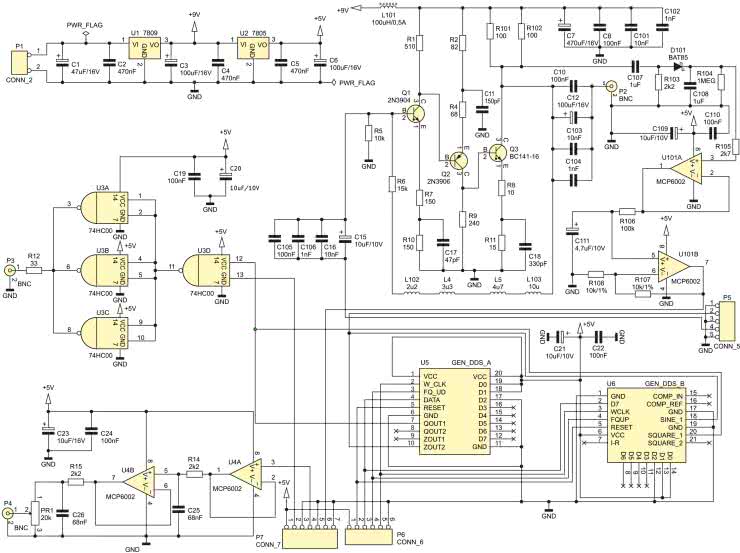

Budowa i działanie

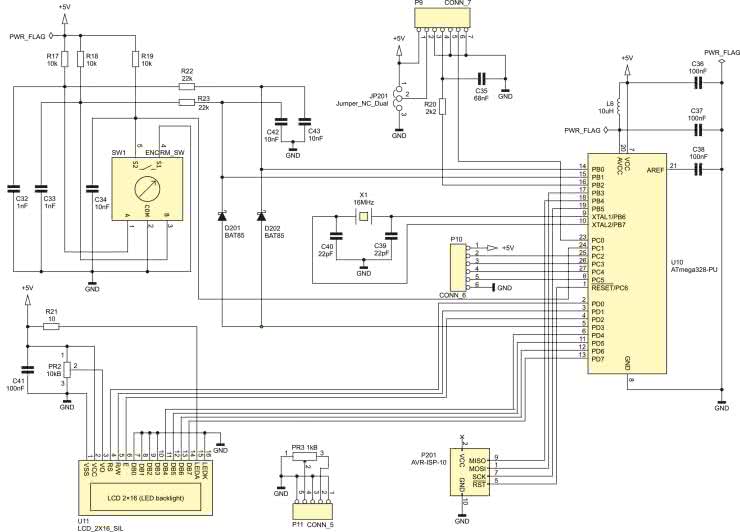

Schemat elektryczny urządzenia zaprezentowano na rysunku 5 (blok sterowania) oraz na rysunku 6 (płyta główna). Na płytce sterowania znajdują się m.in.: mikrokontroler AVR ATmega328-PU (U10), taktowany zegarem 16 MHz, ustalanym przez rezonator kwarcowy X1 z kondensatorami C39 i C40, alfanumeryczny wyświetlacz LCD 16×2 (U11), mechaniczny enkoder obrotowy (SW1) z wbudowanym przyciskiem (przeznaczony do parametryzacji przyrządu) oraz wyprowadzony na złącze P11 potencjometr obrotowy PR3, którym ustalany jest poziom wyjściowego sygnału sinusoidalnego. Rezystor R21 ogranicza prąd podświetlenia wyświetlacza LCD i może zostać zmodyfikowany lub wręcz wyeliminowany - w zależności od typu zastosowanego ekranu. Kondensator C41 redukuje zakłócenia napięcia zasilania wyświetlacza U11 a potencjometr PR2, dla wygody zamontowany od tylnej strony PCB, służy do regulacji kontrastu wyświetlacza.

Elementy: C36, C37, C38 i L6, są odpowiedzialne za filtrację zasilania części cyfrowej i analogowej (przetwornika analogowo-cyfrowego ADC) mikrokontrolera U10. Na port P9 wyprowadzony został odfiltrowany wstępnie przez elementy R20 i C35 sygnał PWM (z pinu 16 układu U10), który po dalszym uformowaniu na płycie głównej przyrządu jest źródłem piłokształtnego sygnału odchylania poziomego "X" w oscyloskopie (praca w trybie wobulatora). Na tym samym porcie zlokalizowano także: wyprowadzenie z jumpera JP201 sygnału kluczującego wyjście sygnału cyfrowego generatora oraz wejście przetwornika ADC0 (pin 23 MCU), przeznaczonego do pomiaru poziomu wyjściowego sygnału sinusoidalnego.

Enkoder obrotowy z przyciskiem SW1, którego styki są polaryzowane przez rezystory R17, R18 i R19, wytwarza sygnały wyjściowe, filtrowane przez kondensatory: C32, C33 i C34. Rezystory R22 i R23 z kondensatorami C42 i C43 formują dodatkowe filtry dolnoprzepustowe RC, których zadaniem jest wygładzanie przebiegów wytwarzanych przez pracujący enkoder. Z kolei sygnały sterujące pracą modułu DDS zostały wyprowadzone na port P10 (wyprowadzenia 25...28 mikrokontrolera U10), skąd dalej są kierowane do modułu wykonawczego (U5 albo U6), zlokalizowanego na głównej płycie przyrządu.

Na rysunku 6 znajduje się schemat głównej (wykonawczej) części przyrządu. W tej części układu znajduje się blok zasilania całego urządzenia z portem P1, stabilizatorami scalonymi: U1 (LM7809) i U2 (LM7805) oraz kondensatorami filtrującymi: C1...C6. Zasilanie +9 V przeznaczone jest dla wzmacniacza wyjściowego sygnału sinusoidalnego, jest też źródłem zasilania dla stabilizatora U2 w połączeniu kaskadowym.

Wzmacniacz-filtr dla sygnału odchylania poziomego oscyloskopu bazuje na podwójnym wzmacniaczu operacyjnym U4A/B (MCP6002), zasilany jest napięciem +5 V filtrowanym dodatkowo przez pojemności C23 i C24. Oba wzmacniacze operacyjne pracują w prostej topologii wtórników napięciowych, zapewniającej prawidłową realizację trójstopniowego filtru RC z elementami: R20/C35 (na omówionej wcześniej płytce sterowania) oraz R14/C25 i R15/C36.

Regulację amplitudy piłokształtnego napięcia wyjściowego, w celu wstępnego dostosowania go do czułości wejścia "X" zastosowanego oscyloskopu, można przeprowadzić za pomocą potencjometru montażowego PR1 - w zakresie od 0 do około 4,5 V. Sygnał ten jest wyprowadzony na port P4 (gniazdo BNC).

Z kolei wygenerowany sygnał sinusoidalny, regulowany i przekazywany poprzez potencjometr liniowy PR3 (montowany na płytce sterowania), po dwukrotnym przejściu przez parę portów: P5-P11 trafia do szerokopasmowego wzmacniacza wyjściowego z tranzystorami Q1...Q3. Wzmacniacz ten jest zasilany napięciem stabilizowanym +9 V poprzez czwórnik separująco-filtrujący z elementami L101, C7, C8, C101 i C102. Ma on rezystancję wyjściową zbliżoną do 50 Ω i wzmocnienie Ku=12 dB w 3-decybelowym paśmie do około 40 MHz (w zależności od jakości zastosowanych tranzystorów).

Wzmacniacz został zaprojektowany z użyciem popularnych i niedrogich tranzystorów bipolarnych (2N3904, 2N3906 i BC141-16). Jego parametry dynamiczne zostały uzyskane na drodze optymalizacji wzmocnień i pasm przenoszenia każdego ze stopni w taki sposób, by finalne pasmo przenoszenia całego układu odpowiadało oczekiwanym założeniom. Pomiędzy poszczególnymi stopniami wzmacniacza zastosowano sprzężenia stałoprądowe, ułatwiające uzyskanie równomiernej charakterystyki przenoszenia także dla niższych częstotliwości pracy. Dodatkowo eliminują one tłumienia, które wprowadzałyby rezystory ustalające punkty pracy poszczególnych tranzystorów. Stałoprądowy punkt pracy bloku wzmacniającego jest ustalany przez globalną pętlę ujemnego sprzężenia zwrotnego z rezystorami R5 i R6 oraz z dławikami L102, L4, L5 i L103.

Głównym zadaniem połączonych szeregowo dławików jest osłabienie globalnego ujemnego sprzężenia zwrotnego wzmacniacza dla wyższych częstotliwości, dla których wzmocnienie tranzystorów Q1...Q3 wyraźnie spada. Zastosowanie szeregowo aż czterech dławików o różnych wartościach indukcyjności miało na celu wyeliminowanie selektywnego przenikania przez nie sygnałów w.cz. z uwagi na równoległe pojemności pasożytnicze różnych typów dławików.

Z kolei kondensatory C11, C17 i C18 dla składowej zmiennej dzielą połączone szeregowo rezystancje R2...R4, R7...R10 oraz R8...R11 w celu kompensacji spadków wzmocnienia poszczególnych stopni tranzystorowych. Sygnał sinusoidalny podawany jest z modułu DDS do wzmacniacza przez połączone równolegle pojemności sprzęgające C15, C16, C105 i C106. Natomiast na jego wyjście (port P2 z gniazdem BNC) trafia przez połączone równolegle kondensatory sprzęgające C10, C12, C103 i C104.

Do wyjścia wzmacniacza sygnału sinusoidalnego dołączony jest także detektor szczytowy z elementami C107, R103, D101, C108 i R104. Jego zadaniem jest wytworzenie napięcia stałego, które z kilkuprocentową dokładnością pozwoli dokonać pomiaru amplitudy wzmocnionego sygnału sinusoidalnego.

Zrezygnowanie z układu w topologii podwajacza napięcia pozwoliło obniżyć detekcję do poziomu około 0,1Vp-p, jednak wymusiło zastosowanie stopni wzmacniających z elementami R105 i U101A (wtórnik napięciowy), R106 i C111 (dolnoprzepustowy filtr wygładzający), U101B, R107, R108 (wzmacniacz napięcia stałego ×2) oraz C109 i C110 (filtracja zasilania U101). Finalnie, pomiar odfiltrowanego i dwukrotnie wzmocnionego napięcia szczytowego sygnału sinusoidalnego odbywa się w przetworniku analogowo-cyfrowym w mikrokontrolerze U10 poprzez jego port ADC0 (wyprowadzenie 23).

Wygenerowany w module DDS prostokątny sygnał cyfrowy jest wyprowadzany z urządzenia poprzez bufor zrealizowany na bramkach NAND układu scalonego U3A...U3D (74HC00) oraz rezystor dopasowujący impedancję R12 na port P3 (BNC). Układ U3 jest zasilany napięciem +5 V, zablokowanym do masy dla zakłóceń impulsowych kondensatorami C19 i C20. Bramka U3D, oprócz funkcji regeneratora kształtu sygnału prostokątnego, pełni także funkcję klucza, za pomocą którego można zablokować wyjście cyfrowe urządzenia poprzez odpowiednie ustawienie jumpera JP201. Takie rozwiązanie zostało podyktowane możliwą potrzebą redukcji zakłóceń impulsowych w przypadku, gdy chcemy pracować wyłącznie z sygnałem sinusoidalnym.

Ostatnie, nieomówione dotychczas bloki, to serce całego urządzenia, czyli moduły DDS: U5 albo U6 z kośćmi AD9850, taktowanymi stabilizowanymi termicznie rezonatorami OCXO. Na płytce głównej przyrządu zlokalizowane zostały gniazda dla dwóch alternatywnie stosowanych modułów U5/U6 (należy użyć tylko jednego z nich). Linie wejściowe (programujące: W_CLK, FQ_UD, DATA oraz RESET) i wyjściowe (analogowy sinus oraz cyfrowy prostokąt) gniazd obu alternatywnych modułów zostały zatem połączone ze sobą bez ryzyka uszkodzenia urządzenia.

Oprogramowanie sterujące oraz montaż urządzenia

Zagadnienia związane z budową i działaniem oprogramowania sterującego pracą urządzenia oraz kluczowe aspekty dotyczące montażu urządzenia zostaną opisane już za miesiąc w kolejnym wydaniu "Elektroniki Praktycznej".

Adam Sobczyk SQ5RWQ

sq5rwq@gmail.com

Zaloguj

Zaloguj