Opisywany generator nie jest urządzeniem dydaktycznym, a pełnoprawnym generatorem przebiegu sinusoidalnego o częstotliwości z zakresu 20 Hz...20 kHz. Sygnał wyjściowy charakteryzuje się małymi zniekształceniami THD+N, wynoszącymi mniej niż 0,15% oraz dobrą stabilnością częstotliwości.

Sygnał sinusoidalny jest generowany w trzech zakresach: 20 Hz...200 Hz, 200 Hz...2 kHz, 2 kHz...20 kHz przy ustalonych częstotliwościach 20/25/32/40/50/63/80/100/125/160/200 i mnożniku 1/10/100. Dodatkowo, generator ma zaimplementowane źródło szumu białego.

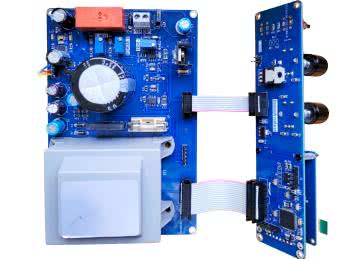

Dzięki zastosowaniu nowoczesnego procesora DSP typu ADAU1701 generator ma niewielkie, kieszonkowe wymiary. Jest zasilany z typowego zasilacza wtyczkowego 5 V/0,5 A lub z niewielkiego Power-Banku poprzez złącze micro USB.

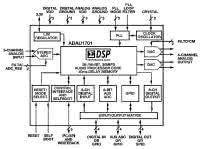

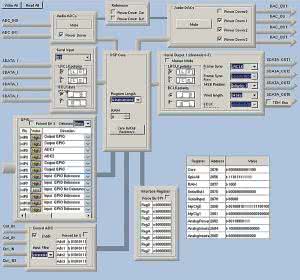

Schemat blokowy procesora ADAU1701 zastosowanego w generatorze pokazano na rysunku 1. Jest to najmniejszy procesor z rodziny SigmaDSP, ale jego zasoby umożliwiają bezproblemową realizację generatora. W aplikacji procesor pracuje z częstotliwością fs=96 kHz.

Sygnał generowany cyfrowo jest doprowadzony do wbudowanego konwertera C/A. Dzięki wyposażeniu DSP w programowany interfejs GPIO nie jest konieczne stosowanie do zmian nastaw zewnętrznego mikroprocesora. Program i dane dla DSP przechowywane są w zewnętrznej pamięci EEPROM.

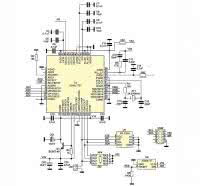

Schemat ideowy bloku DSP generatora zamieszczono na rysunku 2. Procesor DSP (U1) jest taktowany oscylatorem kwarcowym XT1 o częstotliwości 24,576 MHz. Układ ADM811 (U6) jest generatorem sygnału RESET. Tranzystor Q1 i elementy tworzą obwód zasilania rdzenia procesora DSP napięciem 1,8 V. Rezystor R3 oraz kondensatory C12 i C13 są elementami pętli PLL DSP. Pozostałe kondensatory stanowią obwody filtrujące zasilanie DSP.

Wykaz elementówRezystory: (SMD 0805, 1%) Kondensatory: (SMD 0805) Półprzewodniki: Inne: |

Przetwornik A/C, w który jest wyposażony procesor, w tej aplikacji nie ma zastosowania i dla zmniejszenia poboru mocy jest wprowadzony w tryb Power Down. Pamięć EEPROM typu 24LC256 (U5) przechowuje program procesora DSP pracującego w trybie samodzielnym Selfboot. Złącze USBI umożliwia zaprogramowanie pamięci w systemie poprzez programator USBi (przy zwartej zworze WP).

Sygnał wyjściowy z generatora jest dostępny jest na wyprowadzeniu VOUT0. Konieczną filtrowanie i buforowanie sygnału wyjściowego zapewnia podwójny wzmacniacz operacyjny AD8606 (U7). Odfiltrowany sygnał wyjściowy jest doprowadzony do potencjometru VOL służącego do regulacji poziomu napięcia wyjściowego.

Rezystory R10 i R11 polaryzują wejście nieodwracające bufora wyjściowego przy pracy z niesymetrycznym zasilaniem, natomiast kondensator CE4 separuje składową stałą na wyjściu generatora. Sygnał wyjściowy dostępny jest na gnieździe OUT typu RCA.

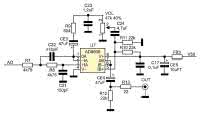

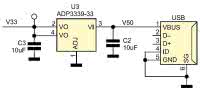

Generator zasilany jest z typowego, niskoszumnego stabilizatora LDO o napięciu wyjściowym 3,3 V. Do jego budowy zastosowano układ ADP3339-3.3 (rysunek 4). Do zasilania filtra i bufora wyjściowego służy napięcie 5 V pochodzące z zasilacza zewnętrznego, filtrowane za pomocą dławika FB3 oraz kondensatorów C17 i CE5.

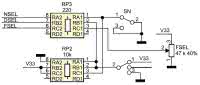

Sterowanie pracą generatora odbywa się poprzez GPIO procesora U4, wg schematu z rysunku 5. Potencjometr FSEL (sygnał FSEL) służy do wyboru generowanej częstotliwości - jego suwak jest doprowadzony do wbudowanego przetwornika A/C. Wybór mnożnika 1/10/100 generatora (sygnał DSEL) odbywa się poprzez przełącznik DSEL, który wraz z rezystorami drabinki RP2 umożliwia doprowadzenie do wbudowanego A/C napięcia: 0, 50%×V33, V33.

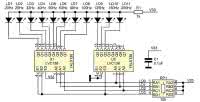

Przełącznik SN (NSEL) służy wyboru rodzaju generowanego sygnału - może to być sygnał o kształcie sinusoidalnym lub biały szum. Położenie przełącznika jest odczytywane za pomocą wejścia GPIO. Dla sygnalizowania aktualnie generowanej częstotliwości służy linijka LED sterowana z multiplekserów kontrolowanych za pomocą wyprowadzeń GPIO procesora DSP. Schemat wskaźnika częstotliwości pokazano na rysunku 6.

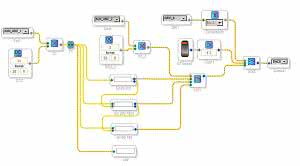

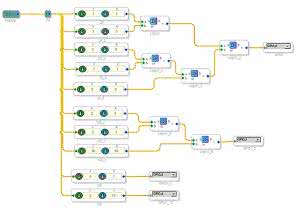

Aplikację sterującą pracą generatora utworzona za pomocą oprogramowania Sigma Studio. Jej schemat blokowy zamieszczono na rysunku 7. Sygnał wejściowy FSEL z bloku ADC1, po konwersji formatu jest doprowadzony do bloków poszczególnych generatorów sinusoidy oraz do bloku wskaźnika częstotliwości LED.

Sygnały wyjściowe doprowadzone są do multipleksera "mnożnika" sterowanego sygnałem DSEL. Sterowanie, podobnie jak w wypadku FSEL, wymaga konwersji formatu i przeliczenia rejestru A/C na trzy poziomy sterujące multiplekserem. Ostatni multiplekser umożliwia wybór pomiędzy funkcją generatora przebiegu sinusoidalnego, a białego szumu (sygnałem NSEL).

W obwód szumu jest wprowadzona korekta wzmocnienia wyrównująca amplitudy sygnałów sinusoidy i szumu na wyjściu generatora. Schematy poszczególnych generatorów przebiegów sinusoidalnych przedstawiają rysunki 8...10.

Aby nie powielać w poszczególnych generatorach częstotliwości 200 Hz i 2 kHz jest ona wyprowadzona z odpowiadającego bloku i doprowadzona do multipleksera poprzedzającego generatora. Takie rozwiązanie zmniejsza liczbę używanych generatorów i umożliwia generowane sygnału z "zakładką" w każdym z pasm.

Ostatnim blokiem programu jest układ sterujący wskaźnikiem częstotliwości. Jego schemat pokazano na rysunku 11. Po konwersji formatu, sygnał FSEL z przetwornika C/A jest doprowadzony jest do bloków Tolerance Analyser pełniących funkcję komparatorów, które mierzą czy sygnał wejściowy zawiera się w określonym przedziale.

Następnie, sygnał za pomocą bramek logicznych jest kodowany binarnie i doprowadzony do wyjść GPIO sterujących demultiplekserami. Ten sposób wybrano pomimo pozornej komplikacji, aby wykorzystać wbudowane GPIO, które niestety nie wystarcza do sterowania wszystkimi LED bezpośrednio, a zmiana procesora na "większy" niepotrzebnie podrożyłaby i skomplikowała układ (np. ADAU1446 ma więcej GPIO, ale nie ma wbudowanego C/A).

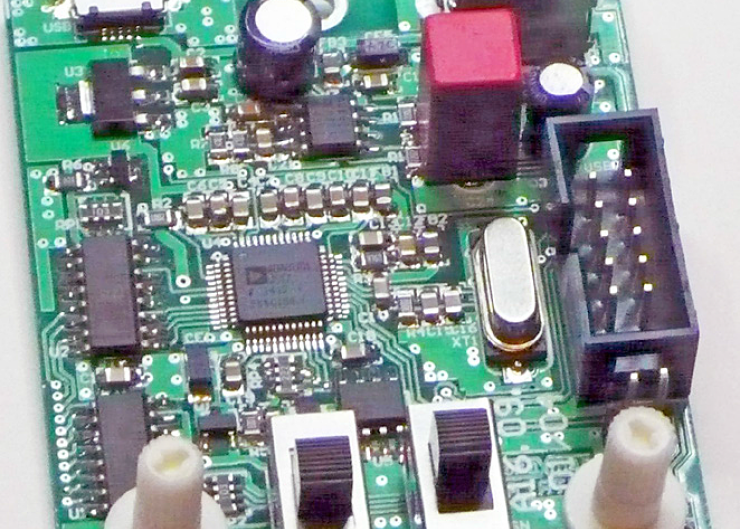

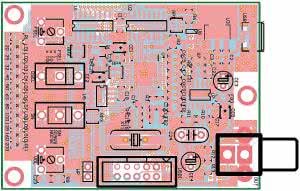

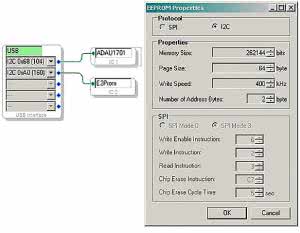

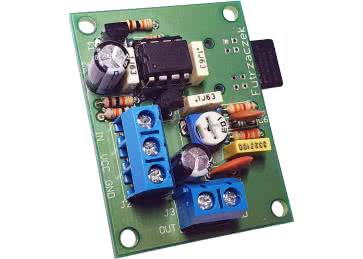

Układ generatora zmontowano na niewielkiej, dwustronnej płytce drukowanej. Jej schemat montażowy pokazano na rysunku 12. Montaż jest typowy i nie wymaga opisu. Po sprawdzeniu poprawności lutowania można przejść do uruchomienia układu. Po dołączeniu zasilania (np. z PC) oraz programatora USBI konieczne jest skonfigurowanie pamięci EEPROM układu według rysunku 13. Kolejnym krokiem jest skonfigurowanie peryferiów DSP wg rysunku 14.

Bloki A/C i niewykorzystane wyjścia C/A są wyciszone i wprowadzone w tryb obniżonego pobory mocy. Po prawidłowej konfiguracji procesora należy załadować skompilowane (Link → Compile → Download, klawisz F7) oprogramowanie do pamięci DSP. Jeżeli nie ma błędów montażowych, układ generatora powinien pracować poprawnie.

Można przetestować funkcję generowania sygnału, działanie przełączników i wskaźników częstotliwości LED. Ostatnim krokiem jest zaprogramowanie pamięci EEPROM do pracy samodzielnej (rysunek 15). W tym celu zakładamy zworę WP i wybieramy opcję Write Latest Compilation to EEPROM. Po zdjeciu zwory urządzenie jest gotowe do pracy.

Adam Tatuś, EP

Zaloguj

Zaloguj