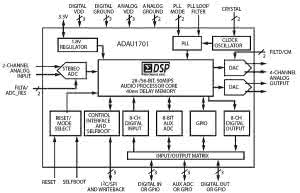

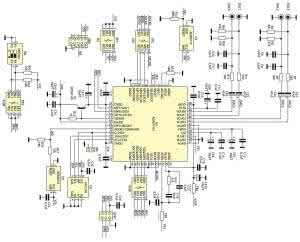

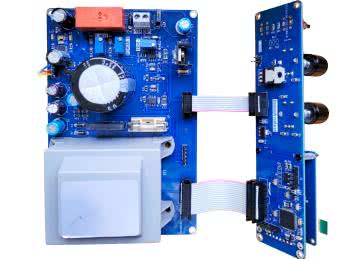

Schemat blokowy SigmaDSP+ pokazano na rysunku 1. Moduł pracuje tylko z cyfrowym sygnałem wejściowym w standardzie S/PDIF. Dzięki zastosowaniu konwertera częstotliwości próbkowania, synchroniczny procesor sygnałowy ADAU1701 (schemat blokowy przedstawiony na rysunku 2) może bez zmian w układzie i oprogramowaniu pracować z sygnałami o fs z zakresu 32...96 kHz.

Obróbka sygnału odbywa się z fs=96 kHz, co odpowiada maksymalnej obsługiwanej przez wbudowane przetworniki C/A częstotliwości próbkowania. Taka konfiguracja umożliwia wykorzystanie układu w charakterze zwrotnicy aktywnej, korektora charakterystyki przenoszenia itp.

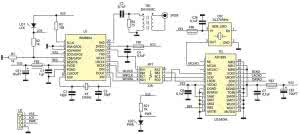

Schemat ideowy Sigma DSP+ jest podzielony na bloki funkcjonalne. Na rysunku 3 pokazano odbiornik/konwerter S/PDIF na I²S z konwerterem częstotliwości próbkowania ASRC. Wejściowy sygnał S/PDIF poprzez transformator separujący TR1 jest doprowadzony do odbiornika/dekodera U1 (WM8804). Układ pracuje w typowej aplikacji, z konfiguracją sprzętową I²S/24 bity.

Dioda świecąca LD1 sygnalizuje prawidłowy odbiór sygnału cyfrowego, natomiast LD2 załączenie napięcia zasilającego. Sygnał wyjściowy I²S o częstotliwości fs z zakresu 32...96 kHz jest doprowadzony do U2 (AD1895) pełniącego rolę konwertera częstotliwości próbkowania.

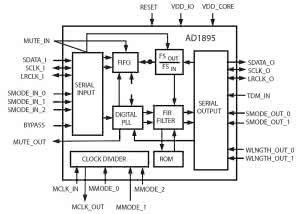

Ze względu na synchroniczną pracę DSP nie jest możliwe obrabianie sygnałów o różnych częstotliwościach fs bez zmian w układzie i oprogramowaniu, co ograniczałoby zastosowania modułu. Układ U2 (AD1895, rysunek 4), przelicza próbki sygnału wejściowego o różnych częstotliwościach próbkowania na jedną fs=96 kHz, z którą pracuje DSP.

Układ AD1895 jest konfigurowany sprzętowo poprzez odpowiednie wymuszenie poziomów na doprowadzeniach konfiguracyjnych. Wyprowadzeniami SMIx jest ustalany format sygnału wejściowego - w prototypie jest to I²S (SMI2...0=001). Wejście BYPASS umożliwia pominięcie bloku ASRC (w prototypie jest on zawsze aktywny).

Wyprowadzeniami SMO1/SMO0 jest ustalany format sygnału wyjściowego (I²S=01), natomiast WLOx - długość słowa wyjściowego (24 bity=00). Wejścia MMx ustawiają tryb master/slave i krotność częstotliwości próbkowania. W modelu U4 jest skonfigurowany do pracy w trybie master - dla sygnału wyjściowego, przy krotności fs=256 (MMx=011).

Dla poprawnej pracy układu ASRC jest wymagany generator sygnału taktującego wykonany w oparciu o lokalny oscylator kwarcowy lub zewnętrzny generator. Maksymalna częstotliwość współpracującego generatora to 30 MHz. Dodatkowym wymogiem jest zapewnianie warunku fosc>138×fs. Zewnętrzny generator o częstotliwości 24,576 MHz spełnia ten warunek z zapasem dla fs=96 kHz będąc jednocześnie źródłem sygnału zegarowego dla ASRC i DSP.

Układ uzupełniają elementy filtrujące zasilanie. Każdy z bloków funkcjonalnych układów U1 i U2 jest zasilany poprzez filtr LC. Na złącze LD są wyprowadzone sygnały sterujące diodami LED.

W wypadku, gdy jest konieczna sygnalizacja stanu pracy, można pominąć diody LD1 oraz LD2 na płytce drukowanej i wyprowadzenie sygnałów np. na front obudowy. Wyjściowy sygnał I²S o ustalonej fs jest doprowadzony wraz z sygnałem zegarowym MCLK do bloku procesora DSP. Schemat DSP pokazano na rysunku 5.

Aplikacja układu ADAU1701 (U3) jest typowa. Pracuje on w trybie samodzielnym SELFBOOT, parametry i program przechowywane są w pamięci EEPROM (U5). Zwora WP służy do wprowadzenia DSP w tryb programowania EEPROM za pomocą programatora USBi. Układ ADM811T (U4) zapewnia restart układów po włączeniu zasilania, natomiast ADM812L (U6) jest odpowiedzialny za generowanie sygnału WB (Writeback) zapisującego do pamięci EEPROM parametry DSP przy zaniku napięcia zasilania.

Układ jest zasilany napięciem 3,3 V. Stabilizator z tranzystorem Q1 zapewnia zasilanie 1,8 V dla rdzenia DSP. Przetworniki C/A procesora DSP pracują z filtrami biernymi RC. Do złącza GPIO doprowadzone są cztery uniwersalne sygnały GPIO przeznaczone do dołączenia zewnętrznych manipulatorów sterujących lub sygnalizujących pracę DSP. Dwa dodatkowe sygnały GPIO doprowadzone są do przełącznika SW umożliwiając np. wybór konfiguracji DSP. Poszczególne bloki DSP zasilane są poprzez filtry LC.

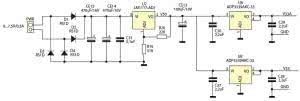

Układ uzupełnia zasilacz, którego schemat zamieszczono na rysunku 6. Jest on zbudowany w oparciu o typowe układy: LM1117 (U7) dostarczający napięcie +5 V oraz dwa niskoszumne stabilizatory ADP3339 (U8 i U9) dostarczające napiecia 3,3 V, osobno dla częsci cyfrowej i analogowej. Moduł jest zasilany z zewnętrznego transformatora 6...7,5 V o mocy minimalnej 4 VA. Układ U7 wymaga zastosowania radiatora.

Wykaz elementówRezystory: (SMD 0805) Kondensatory: Półprzewodniki: Inne: |

Montaż i uruchomienie

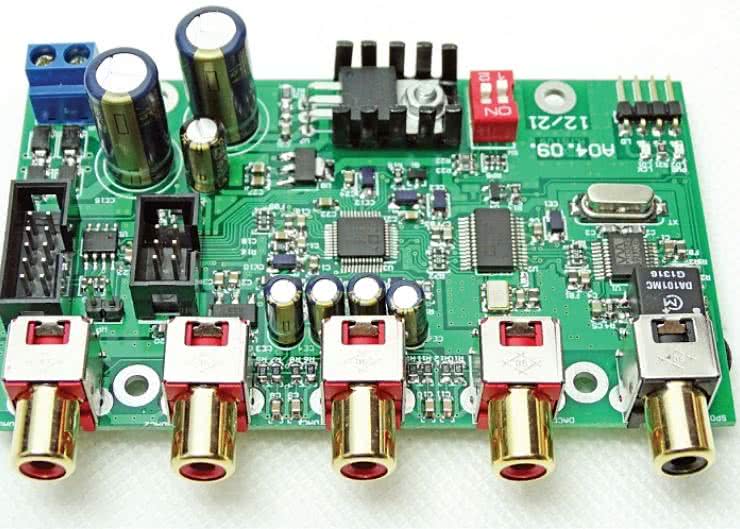

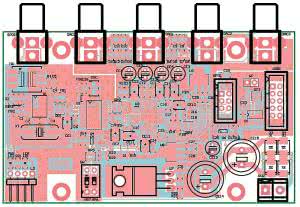

Moduł SigmaDSP+ jest zmontowany na niewielkiej, dwustronnej płytce drukowanej. Jej schemat montażowy pokazano na rysunku 7. Sposób montażu jest typowy i nie wymaga opisu, należy tylko sprawdzić jego poprawność.

Moduł nie wymaga uruchamiania. Konfiguracja i oprogramowanie odbywa się za pomocą graficznego środowiska Sigma Studio i programatora USBi. Konfiguracja sprzętowa modułu jest stała i może zostać wykorzystana jako szablon we własnych aplikacjach.

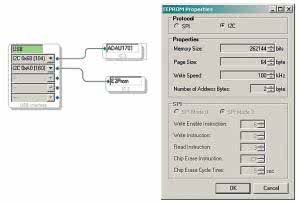

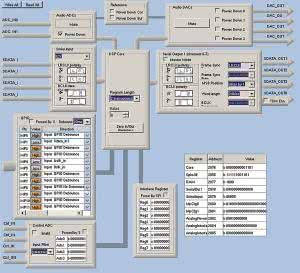

Na rysunku 8 pokazano konfigurację USBi, DSP i pamięci EEPROM. Konfigurację sprzętową DSP przedstawia rysunek 9. Przetwornik A/C niewykorzystany w projekcie jest wyciszony i wyłączony dla obniżenia poboru mocy, podobnie wyjściowy interfejs szeregowy.

Wyprowadzenia MP1, MP4, MP5 skonfigurowane są jako wejściowy interfejs I²S. Wyprowadzenia MP6 i MP7 służą jako wejścia cyfrowe - tych ustawień nie należy zmieniać. Pozostałe piny (MP2, MP3, MP8, MP9) mogą być użyte w dowolny sposób.

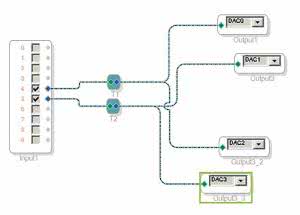

Nieskomplikowaną aplikację testową zamieszczono na rysunku 10. W wypadku tworzenia własnych aplikacji należy pamiętać o zmianie w menu Sigma Studio fs na 96 kHz dla całego projektu (rysunek 11). Sygnał wejściowy z portu szeregowego SDI1 jest doprowadzony bez obróbki do wyjść prztwornika C/A. Umożliwia to szybkie sprawdzenie poprawności działania DSP. Aplikację w trybie symulowania "F7" (zwora WP zdjęta) można sprawdzić po załadowaniu skompilowanego programu do DSP.

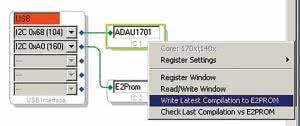

Programowanie pamięci EEPROM do pracy samodzielnej (WriteLatestCompilation to E2PROM) należy wykonać przy założonej zworze WP (rysunek 12).

Pozostaje życzyć powodzenia w tworzeniu własnych projektów! W wypadku problemów pomocne może być forum http://ez.analog.com w dziale Sigma DSP.

Adam Tatuś, EP

Zaloguj

Zaloguj