- odbiornik SDPIF w standardzie optycznym Toslink

- wyjście w standardzie I2S

- pracuje jako master magistrali I2S

- zasilanie 3,3…5 V

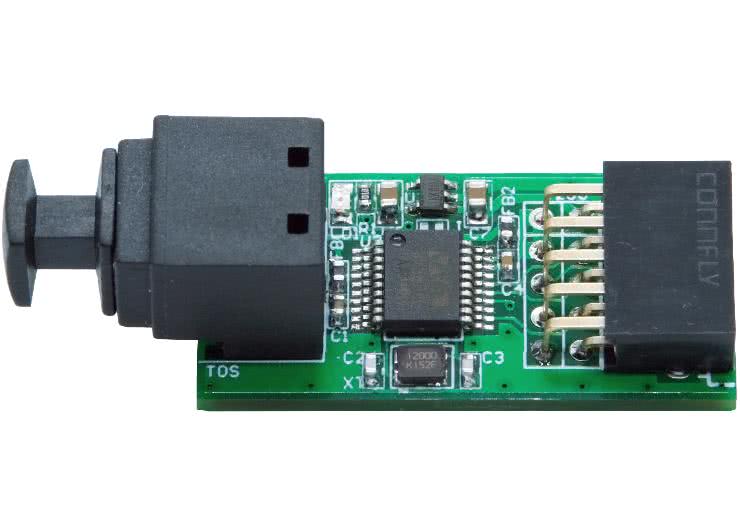

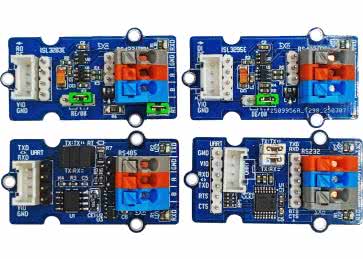

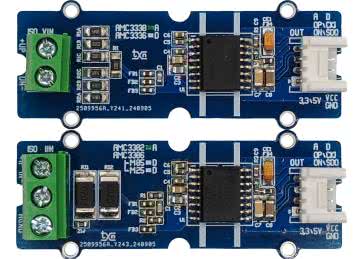

Niewielki rozmiar oraz uniwersalne zasilanie 3,3...5 V pozwalają na zastosowanie modułu z komputerami SBC, STM, Arduino i zestawem AudioDSP. W zależności od wlutowanego złącza może współpracować bezpośrednio z AudioDSP lub ze wszystkimi płytkami uruchomieniowymi wyposażonymi w interfejs Pmod.

Budowa i działanie

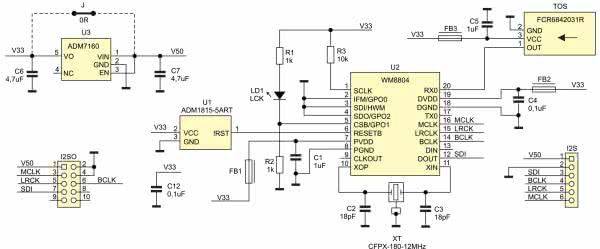

Schemat układu został pokazany na rysunku 1. Moduł umożliwia podłączenie sygnału w standardzie Toslink i konwertuje go na standard magistrali I2S. Jako odbiornik wykorzystano popularny układ typu WM8804 (U2), pracujący w konfiguracji sprzętowej I2S/16 bit. Układ U1 ADM1815 zapewnia poprawny restart odbiornika WM8804 po włączeniu zasilania, dioda LD sygnalizuje odbiór sygnału SPDIF.

Stabilizator U3 zapewnia zasilanie odbiornika. Jeżeli przewidujemy pracę tylko z zasilaniem 3,3 V, można go pominąć i wlutować zworę J. Wszystkie niezbędne sygnały wyprowadzone są na złącze szpilkowe I2S zgodne z PMOD lub złącze I2SO zgodnie z AudioDSP. Standard napięciowy I2S to 3,3 V.

Odbiornik pracuje jako master magistrali I2S, dostarczając także sygnał zegarowy MCLK = 256*fs.

Montaż i uruchomienie

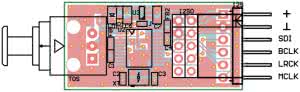

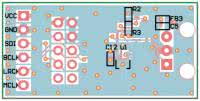

Moduł zmontowany jest na dwustronnej płytce drukowanej, montaż jest klasyczny i nie wymaga dokładnego opisu. Schemat płytki PCB wraz z rozmieszczeniem elementów pokazano na rysunku 2 i rysunku 3.

Rodzaj wlutowanego złącza I2S zależy od współpracującego zestawu uruchomieniowego, dla AudioDSP jest to ZL263-10DG, dla PMOD listwa kątowa SIP6 2,54 mm. Odbiornik FCR6842031R może zostać zastąpiony FCR6842032R. Różnią się one tylko mocowaniem mechanicznym, FCR6842032R nie ma otworu mocującego odbiornik do obudowy urządzenia.

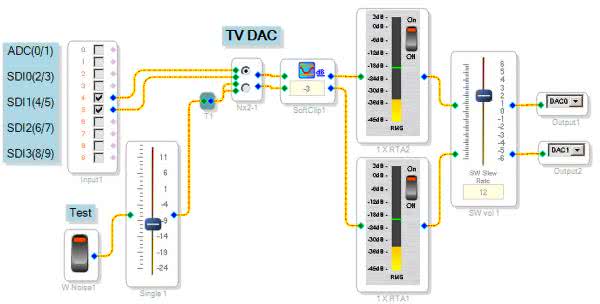

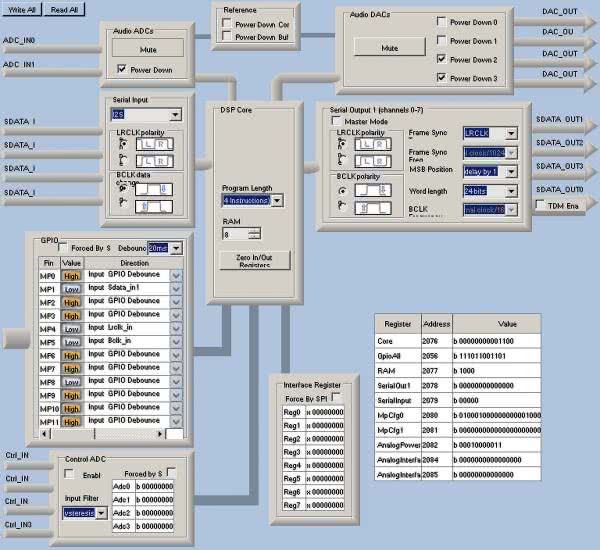

Odbiornik zmontowany ze sprawnych elementów nie wymaga uruchamiania. Przykładową aplikację TVDAC, dla odbiornika Toslink i zestawu AudioDSP, pokazano na rysunku 4. W zestawie AudioDSP należy ustawić zworę XT w położenia MCLK, gdyż procesor DSP taktowany będzie zegarem z odbiornika Toslink. Zdekodowany sygnał z odbiornika w standardzie I2S doprowadzony jest do portu szeregowego SDI1 procesora ADAU1701. Stąd przez multiplekser umożliwiający przełączenie źródła na sygnał testowy białego szumu doprowadzony jest do bloku limitera SoftClip, następnie przez bloki pomiaru i regulator poziomu sygnału do wyjść DAC0/1. Konfigurację sprzętową procesora pokazuje rysunek 5.

Po wgraniu aplikacji do ADAU1701 i podłączeniu źródła sygnału powinna zaświecić się LD1, sygnalizując poprawny odbiór SPDIF, a na wyjściach DAC0/1 pojawi się analogowy sygnał audio.

Adam Tatuś

adam.tatus@ep.com.pl

- R1, R2: 1 kΩ 1% SD0603

- R3: 10 kΩ 1% SD0603

- C1, C5: 1 μF SMD0603

- C2, C3: 18 pF SMD0603

- C4, C12: 0,1 μF SMD0603

- C6, C7: 4,7 μF SMD0805

- LD1: LED zielona SMD0805

- TOS: odbiornik Toslink FCR6842031R (lub FCR6842032R)

- U1: ADM1815-5ART (SOT-23)

- U2: WM8804 (SSOP20_300)

- U3: ADM7160AUJZ-3.3 (SOT-23-5)

- XT: kwarc 12 MHz CFPX-180

- FB1…FB3: dławik ferrytowy 600 V/100 mA SMD 0603

- I2S: złącze SIP6 2.54 kątowe (PMOD)

- I2SO: złącze 2×5 kątowe męskie (DSP)

- J: zwora (opis w tekście) SMD0402

Zaloguj

Zaloguj