Każdy system wbudowany (Embedded System) musi zawierać procesor główny – CPU, pamięć operacyjną – RAM (Random Access Memory) oraz pamięć nieulotną, której zawartość można modyfikować – NVM (Non-Volatile Memory). W ostatnich kilku latach obserwowaliśmy intensywny rozwój w obszarze wszystkich trzech wymienionych grup komponentów. Procesory ARM błyskawicznie przeszły z architektury 32-bitowej na 64-bitową oraz z częstotliwości taktowania mierzonych w MHz do poziomu gigaherców, a dodatkowo standardem stały się układy wielordzeniowe (Multicore Processors). Najsłabszym ogniwem okazały się pamięci, ale producenci tych komponentów szybko nadrobili zaległości.

Pamięci w systemach embedded

Pierwszym w pełni półprzewodnikowym rodzajem pamięci, która umożliwia budowanie złożonych systemów embedded, jest pamięć Flash. Powstała ona z rozwinięcia technologii EEPROM i – w zależności od budowy komórek pamięci oraz ich wzajemnego połączenia – dzieli się na:

- pamięć Flash typu NOR,

- pamięć Flash typu NAND.

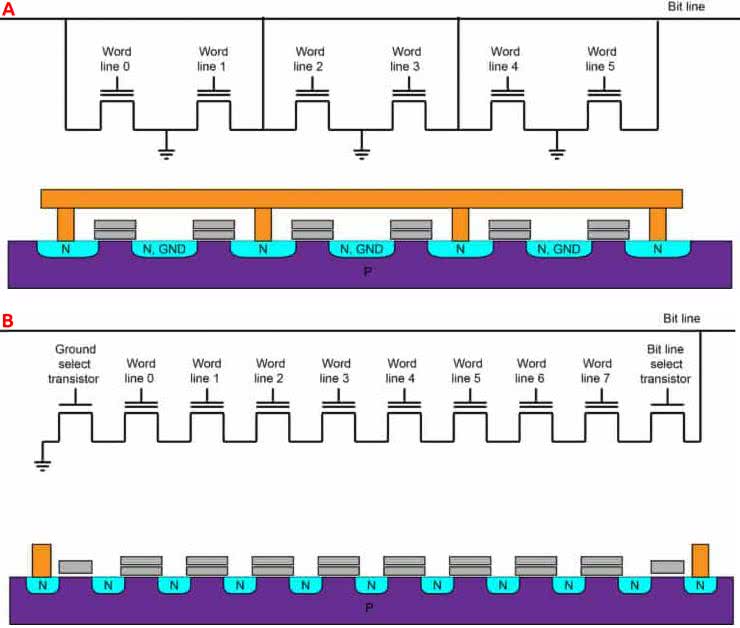

Na rysunku 1 pokazano uproszczone struktury obu rodzajów pamięci. W NOR Flash każda komórka jest indywidualnie połączona z linią bitową, natomiast komórki NAND Flash są połączone szeregowo z linią bitową. Struktura szeregowa zmniejsza liczbę połączeń, co skutkuje zwiększeniem gęstości układu – przy tej samej technologii procesu pamięć NAND Flash zajmuje o około 60% mniej przestrzeni niż pamięć NOR Flash. W naturalny sposób wpływa to na koszt produkcji (wytwarzanie pamięci NOR Flash jest droższe), ale ma też istotny wpływ na parametry układów.

NOR Flash

Pamięć NOR Flash charakteryzuje się dużą szybkością odczytu i zapewnia swobodny dostęp do każdej komórki pamięci. Możliwe jest bezpośrednie odwołanie do dowolnej lokalizacji w pamięci, bez konieczności adresowania na poziomie bloków. Te dwie kluczowe cechy czynią pamięć NOR Flash idealną do przechowywania kodu programu sterującego, takiego jak BIOS komputera.

W pamięciach Flash obu typów dane mogą być zapisywane tylko wtedy, gdy komórki zostały wcześniej wykasowane. Kasowanie danych w pamięci NOR Flash przebiega relatywnie wolno – każdy pojedynczy bajt musi być „wyczyszczony”. Trwa to nawet kilkaset razy dłużej niż w przypadku NAND Flash – na przykład układ Cypress NAND Flash S34ML04G2 wymaga 3,5 ms, aby usunąć blok o wielkości 128 kB, podczas gdy pamięć Flash Cypress NOR S70GL02GT potrzebuje około 520 ms, aby wykasować sektor o tym samym rozmiarze. To różnica prawie 150-krotna. Wolne kasowanie danych w pamięciach NOR wydłuża również operację zapisu, dlatego układy NOR Flash często oferują rozwiązania wyposażone w funkcję buforowania danych.

Pamięci te pobierają ponadto więcej energii w trakcie zapisywania danych, niż ma to miejsce w przypadku NAND Flash, ale są bardziej energooszczędne w trakcie samego odczytywania danych oraz w trybie standby. Zatem w urządzeniach zasilanych bateryjnie i innych zastosowaniach, w których problematyczne okazuje się zużycie energii, pamięci NOR Flash stanowią doskonałą opcję.

Pamięci z interfejsem szeregowym SPI

Pamięci NOR Flash są dziś dostępne zwłaszcza jako układy z interfejsem szeregowym SPI i oferują pojemności nawet 1 Gb (1 gigabit). Działają przy napięciu 3,3 V lub 1,8 V (fotografia 1), a w wersji Ultra Low Voltage – nawet 1,2 V.

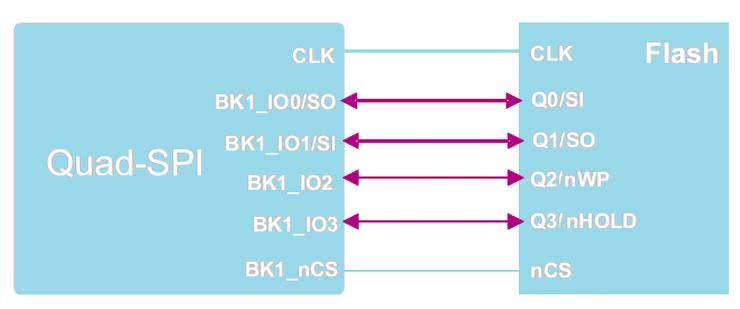

Zastosowanie interfejsu szeregowego pozwala zmniejszyć rozmiary tych komponentów oraz ich cenę, a jednocześnie umożliwia uproszczenie projektu PCB. Jednak przejście na mniejszą liczbę linii komunikacyjnych oznacza niższą przepustowość danych. Aby znaleźć kompromis pomiędzy tymi zależnościami, w najnowszych interfejsach szeregowych SPI producenci używają wersji z czterema wejściami/wyjściami danych – QSPI (Quad SPI) – dostosowanej do układów pamięci Flash SQI (rysunek 2).

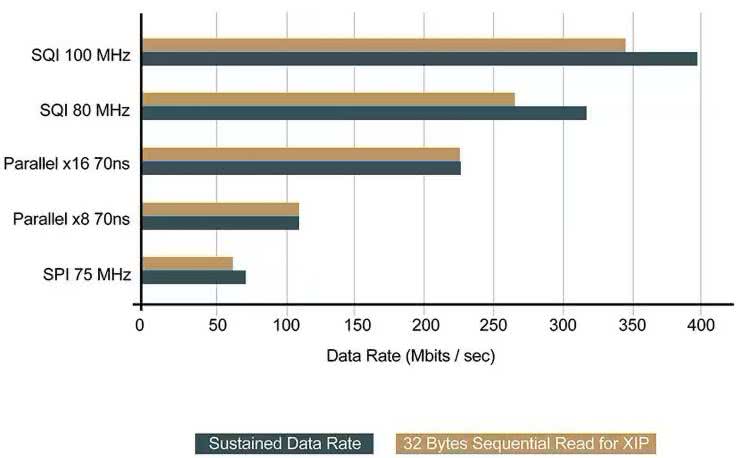

Flash SQI oznacza Flash Serial Quad I/O, czyli pamięć z 4-bitowym synchronicznym interfejsem szeregowym, charakteryzującym się naprawdę małą liczbą pinów i dużą przepustowością – komunikacja może być synchronizowana zegarem o częstotliwości nawet 100 MHz. Komendy sterujące są bardzo podobne do poleceń SPI, ale zawierają 4-bitowe sekwencje, zamiast jednobitowego strumienia. Dlatego interfejs ten oferuje około czterokrotnie większą przepustowość danych niż klasyczny SPI. W porównaniu do równoległych interfejsów pamięci Flash, SQI Flash zapewnia bardzo dużą wydajność, bez konieczności stosowania skomplikowanych obwodów PCB – rysunek 3.

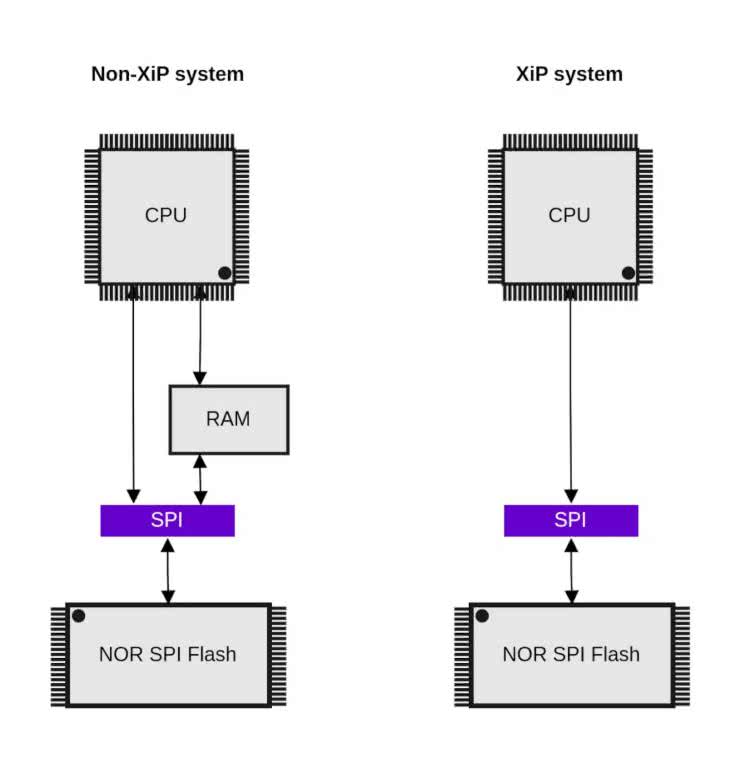

NOR Flash i XIP

Pamięci NOR Flash przyczyniły się do wdrożenia aplikacji działających w trybie XIP (Execution-in-Place). Określenie to odnosi się do wykonywania kodu programu bezpośrednio z pamięci zewnętrznej, bez potrzeby kopiowania do pamięci RAM. Uruchamianie kodu programu z pamięci zewnętrznej umożliwia zwolnienie dodatkowej pamięci operacyjnej na dane dynamiczne. Ideę tego rozwiązania pokazuje rysunek 4. Aby XIP był możliwy, pamięć musi oferować dostęp swobodny i wystarczająco dużą przepustowość. NOR Flash doskonale nadaje się do rozwiązań typu XIP, natomiast NAND Flash już nie. Kod programu zawarty w pamięci NAND Flash musi zostać skopiowany do pamięci RAM przed wykonaniem.

NAND Flash

Pamięć NAND Flash przede wszystkim odznacza się większą gęstością upakowania danych, co przekłada się na korzystniejszy stosunek kosztu do pojemności niż w przypadku pamięci NOR Flash. Jednak jest to okupione nieco utrudnionym dostępem do danych – tzw. dostępem sekwencyjnym. Wszystkie operacje odczytu i zapisu wykonywane są na określonych blokach pamięci, a dane do i z bloków przekazywane są sekwencyjnie. Tylko czas kasowania i zapisu jest krótszy niż w NOR Flash, ale w niektórych aplikacjach to wystarczy, aby wypadkowy czas dostępu również był korzystniejszy dla NAND Flash.

Działanie sekwencyjne ogranicza zakres zastosowań pamięci tego typu. Jak już wspomniano, wykonywanie kodu programu z NAND Flash jest zwykle możliwe dopiero po wcześniejszym skopiowaniu całości lub wybranych fragmentów do pamięci RAM.

Niezawodność pamięci NAND Flash

Niezawodność zapisanych danych pozostaje ważnym aspektem każdego urządzenia. W pamięciach Flash występuje zjawisko zwane bit-flipping – niektóre bity mogą zostać odwrócone. Zjawisko to jest powszechniejsze w NAND Flash niż w NOR Flash.

Ze względu na wydajność procesu produkcji nawet nowe pamięci NAND Flash zawierają uszkodzone bloki (bad blocks), które są rozrzucone całkowicie losowo i mogą zajmować nawet 2% pojemności pamięci. Ponadto każdy blok ma określoną żywotność – zwykle jest to ok. 100 000 cykli zapisu. To duża wartość, ale w niektórych aplikacjach wykonujących intensywne działania na pamięci mogą powstawać kolejne uszkodzone bloki i należy zadbać o odpowiednie zarządzanie nimi oraz o implementację systemu korekcji błędów (ECC).

Nowe pamięci NOR Flash są dostarczane bez uszkodzonych bloków, a ze względu na zastosowania tych układów ryzyko powstawania uszkodzeń okazuje się znikome.

Klasyfikacja pamięci NAND Flash

Generalnie można wyróżnić trzy główne typy pamięci NAND: SLC (Single Level Cell), MLC (Multi Level Cell) i TLC (Triple Level Cell). Pamięci TLC mają większą pojemność (przy porównywalnych wymiarach) niż MLC, które z kolei pod tym względem przewyższają SLC. Oprócz tego każdy typ pamięci NAND ma charakterystyczne zalety i pewne ograniczenia.

W pamięciach SLC każda komórka przechowuje tylko jeden bit informacji, ale pracuje przy niższych napięciach, co wydłuża żywotność nośnika wyrażoną liczbą cykli kasowania/zapisywania. Ograniczeniem układów SLC NAND jest większy koszt w porównaniu z innymi typami pamięci, które charakteryzuje wyższa gęstość upakowania danych.

W pamięciach MLC Flash każda komórka przechowuje dwa bity informacji, ale proces odczytu i zapisu działa wolniej, w porównaniu z pamięciami typu SLC. Główną zaletą jest (nawet kilkukrotnie) niższy koszt bitu danych niż w przypadku SLC NAND.

W pamięciach TLC NAND każda komórka przechowuje trzy bity informacji, ale działa wolniej od omówionych poprzednio, jest bardziej podatna na błędy i zużycie. Pamięci TLC są wytwarzane wtedy, gdy priorytetem jest koszt, a zatem głównie w elektronice użytkowej.

Ponadto dostępne są pamięci 3D NAND lub V-NAND (Vertical NAND), które mają strukturę warstwową, aby zwiększyć gęstość upakowania danych. Na rynku można spotkać układy o ponad 200 warstwach – fotografia 2.

Błędy przechowywania

Dane przechowywane w pamięciach Flash z czasem ulegają samoistnemu uszkodzeniu. Jest to spowodowane utratą ładunku w bramkach tranzystorów tworzących komórki pamięci i ostatecznie prowadzi do zafałszowania zapisanej informacji. Aby przeszkodę tę pokonać, należy problematyczny blok skopiować, a następnie skasować. Warto dodać, że na ten typ błędów bardziej narażone są komórki pamięci z większą liczbą cykli kasowania/programowania. Czynnikiem, który sprzyja zafałszowywaniu zapisanych danych, jest również temperatura – im wyższa, tym większe prawdopodobieństwo jego wystąpienia. Częściej tego typu błędy występują w pamięciach MLC i TLC.

Pamięci NAND Flash zapewniają typową retencję danych na poziomie 10 lat, podczas gdy NOR Flash oferuje czas przechowywania danych na poziomie 20 lat.

Interfejsy pamięci NAND Flash

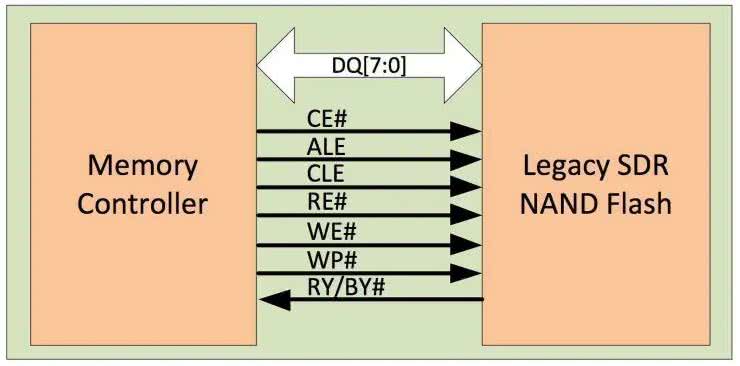

Pierwsze interfejsy pamięci NAND Flash, znane jako Legacy, były przystosowane do transferu asynchronicznego i zawierały sygnały sterujące WE – Write-Enable i RE – Read Enable, bez konieczności stosowania sygnału zegarowego. Interfejs Legacy obsługuje przesyłanie danych przy pojedynczej szybkości transmisji – Legacy SDR (Legacy Single Data Rate), zatem przesyłanie danych odbywa się tylko na jednym zboczu sygnału sterującego.

Typowe pamięci NAND Flash zawierają 8-bitową lub 16-bitową magistralę danych/adresów z dodatkowymi sygnałami, takimi jak: Chip Enable (CE), Write Enable (WE), Read Enable (RE), Address Latch Enable (ALE), Command Latch Enable (CLE) i Ready/Busy (RB) – rysunek 5. Układ sterujący musi dostarczyć polecenie (czytaj, zapisz lub usuń), a następnie adres i dane. Te wszystkie operacje sprawiają, że losowy odczyt danych z NAND Flash był bardzo powolny i maksymalna osiągalna przepustowość wynosiła około 40 MB/s.

Aby przezwyciężyć ograniczenia związane z różnorodnością działania interfejsów w układach NAND Flash, główni producenci pamięci Flash (z wyjątkiem Samsunga i Toshiby) opracowali w 2007 roku standard ONFI (Open NAND Flash Interface). Początkowa wersja specyfikacji ONFI miała na celu ujednolicenie przypisania pinów i poleceń pamięci Flash NAND. Interfejs elektryczny ONFI NAND v1.0 jest podobny do Legacy SDR, ale wprowadza opcję obsługi 16-bitowej magistrali danych lub dodatkowej niezależnej 8-bitowej magistrali danych i sygnałów sterujących w celu obsługi do 4 „kości” w jednym pakiecie. Aby połączyć się ze sterownikami pracującymi z różnymi napięciami logicznymi, dodano również opcjonalną szynę napięciową (VDDQ) jako zasilanie wejściowe interfejsu we/wy. Maksymalna osiągalna przepustowość wyniosła około 50 MB/s. Obecnie grupa robocza ONFI nadal publikuje aktualizacje rozszerzające zestaw standardów, a najnowszą wersją roboczą jest ONFI 5.0 z 2021 r. Standard ten określa przepustowość komunikacji do 2400 MT/s (megatransferów na sekundę).

W rok po wydaniu ONFI 1.0, firmy Samsung Semiconductors i Toshiba Memory Corporation (TMC) – wiodący na świecie producenci pamięci flash NAND – wprowadzili standard interfejsu Toggle jako alternatywę układów pamięci Flash, których możliwości wykraczały poza standard Legacy. Ewolucja standardu Toggle nastąpiła w ramach wydań specyficznych układów NAND firm Samsung i TMC. Kontrastuje to ze standardem ONFI, który został zaktualizowany w oparciu o ujednolicone publiczne wydania opracowane przez jego grupę roboczą.

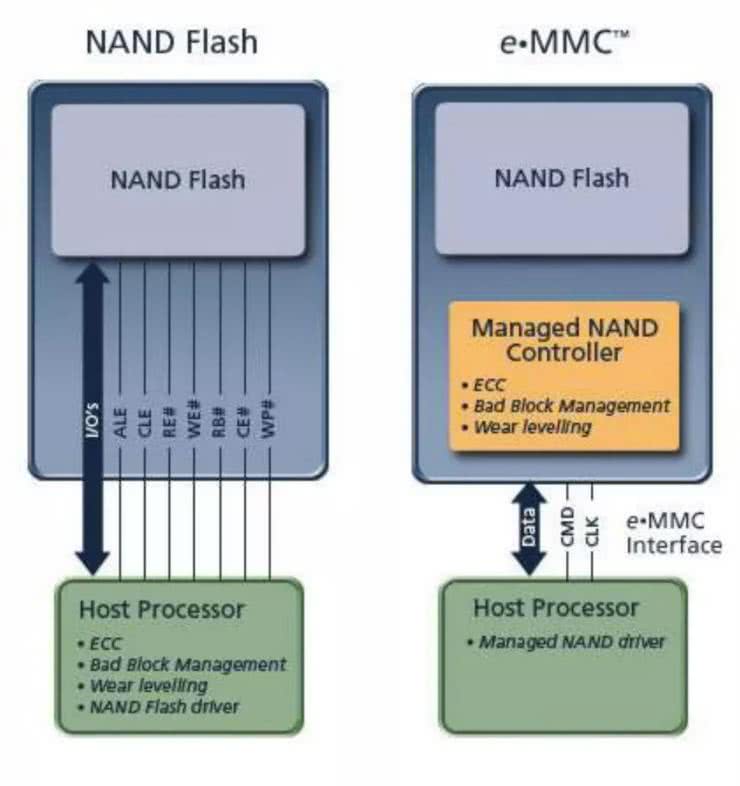

Embedded Multi Media Card – eMMC

W pewnym momencie pamięci NAND Flash dostępne były jako układy wykonane różnych technologiach (SLC, MLC, TLC, V-NAND, 3D NAND) i wyposażone w różne interfejsy (Legacy, ONFI, Toggle, QSPI). Potrzebny był ujednolicony standard komunikacyjny pomiędzy hostem a pamięcią – niezależny od właściwości zastosowanych pamięci.

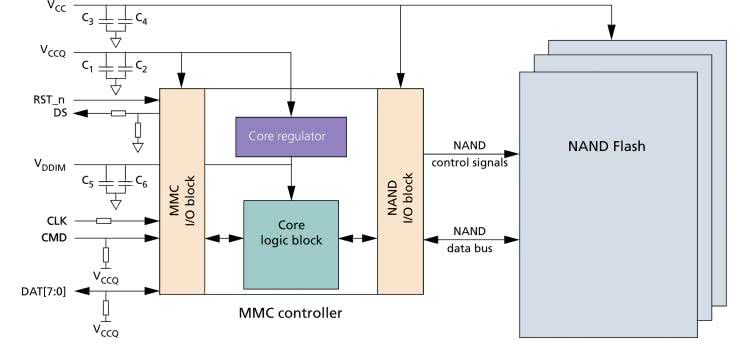

Określenie eMMC (embedded Multi-Media Card) odnosi się do miniaturowego systemu – składającego się zarówno z samej pamięci Flash, jak i jej kontrolera, zintegrowanych na wspólnej płytce krzemowej – wyposażonego w wygodny interfejs, charakterystyczny dla kart pamięci MMC. Kontroler obsługuje funkcje korekcji błędów i zarządzania blokami, w tym logiczną alokację bloków i równoważenie zużycia, które wymagają skomplikowanych algorytmów i zależą całkowicie od technologii zastosowanych pamięci NAND Flash. Kontroler obsługuje te funkcje wewnętrznie, dzięki czemu są one niewidoczne dla procesora głównego (hosta). Schemat blokowy systemu eMMC – w porównaniu ze standardową konfiguracją z pamięcią NAND Flash – pokazano na rysunku 6.

Standard eMMC został opracowany w 2006 roku przez JEDEC i MultiMediaCard Association. Technologia przeznaczona jest do stosowania w urządzeniach przenośnych (takich jak telefony komórkowe), Internecie Rzeczy (IoT) i innych systemach wbudowanych. Interfejs komunikacyjny zawiera 8-bitową, równoległą magistralę danych oraz sygnał zegarowy (CLK), sygnał sterowania komendami (CMD), strobowanie danych (DS), a także linię zerującą (RST) i kilka linii zasilania – rysunek 7.

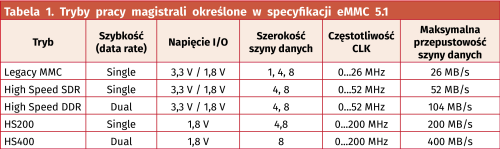

Najnowsza specyfikacja eMMC w wersji 5.1 pozwala na przesyłanie do 400 megabajtów na sekundę (MB/s), co jest porównywalne do dysku półprzewodnikowego z interfejsem SATA. Wszystkie tryby pracy magistrali określone w specyfikacji eMMC 5.1 podsumowano w tabeli 1.

Pojemności układów eMMC wahają się od 1 GB do 512 GB (fotografia 3) i są dostępne w różnych klasach w zależności od docelowego zastosowania (np. w aplikacjach konsumenckich czy przemysłowych). Biorąc pod uwagę rozmiar, eMMC jest w stanie obsłużyć niezwykle duże ilości danych na tak małej powierzchni.

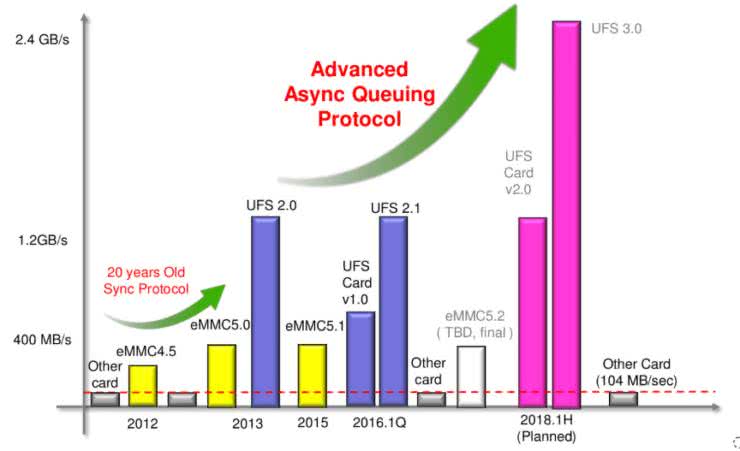

UFS zamiast eMMC

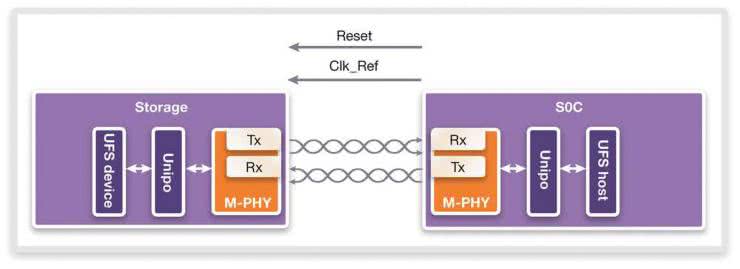

W 2011 roku JEDEC wydał standard UFS (Universal Flash Storage), mający zastąpić pamięci flash eMMC. UFS ma szeregowy interfejs LVDS (Low-Voltage Differential Signaling), który zawiera oddzielnie przypisane wyprowadzenia do odczytu/zapisu. Pozwala to na pełną interakcję dwukierunkową (full duplex) – dane do odczytu i zapisu mogą być przesyłane jednocześnie. eMMC ma równoległy interfejs, który może wysyłać dane tylko w jednym kierunku w danej chwili.

Kolejnym istotnym rozwiązaniem jest kolejka poleceń (Command Queue), która porządkuje komendy do wykonania. W ten sposób można scalać niektóre polecenia, aby nie powtarzać zadań, a dodatkowo kolejność operacji może zostać odpowiednio zmieniona. eMMC, bez CQ, musi poczekać na proces, który zostanie zakończony, zanim przejdziemy do realizacji następnego.

UFS w wersji 2.0 oferuje sekwencyjne prędkości odczytu/zapisu praktycznie porównywalne z dyskami SSD, jednocześnie zachowując niskie zużycie energii, charakterystyczne dla eMMC – rysunek 9.

Pamięć operacyjna

Określenie SDRAM (Synchronous Dynamic Random Access Memory) odnosi się do rodzaju pamięci dynamicznej wyposażonej w interfejs synchroniczny, dzięki któremu wewnętrzne sygnały taktujące generowane są z zegara szyny pamięci, co w efekcie pozwala na przyspieszenie transmisji danych. Obecnie jest to najpopularniejsza architektura pamięci RAM, ale produkowana niemal wyłącznie jako pamięć DDR (Double Data Rate). DDR oferuje zdwojoną przepustowość, ponieważ przesył danych następuje przy obu zboczach sygnału zegarowego – narastającym i opadającym (w przeciwieństwie do SDR – Single Data Rate).

Każda pamięć ma określoną częstotliwość pracy, czyli rzeczywistą częstotliwość taktowania wyrażoną w MHz. W przypadku pamięci DDR szczególne znaczenie zyskuje częstotliwość efektywna, której wartość odpowiada podwojonej częstotliwości rzeczywistej i wyrażona jest w MT/s (megatransferach na sekundę). Przepustowość jest z kolei wielkością określającą zdolność do przesyłania danych w jednostce czasu – MB/s (megabajtów na sekundę) i uwzględnia częstotliwość efektywną oraz szerokość magistrali danych pamięci.

Pamięć DDR od dawna używana była w komputerach stacjonarnych i przenośnych – w postaci modułów DIMM. Wzrost wymagań stawianych systemom embedded sprawił, że pamięci DDR znalazły się na płytkach modułów SoM i komputerów SBC – fotografia 4. Rozwiązania tego typu cechuje relatywnie nieduża przepustowość, ale w zamian gwarantują one niewielkie opóźnienie (czyli krótki czas od wysłania polecenia do pamięci, do uzyskania dostępu do danych) oraz względnie niski koszt produkcji i duże pojemności.

Parametry i generacje

Pamięci SDRAM korzystają z adresowania o strukturze siatki – przecięcie wierszy i kolumn wskazuje konkretny adres pamięci. Z takiej organizacji wynikają cztery podstawowe parametry czasowe (opóźnienia/timingi pamięci/latency), które określają szybkość działania układu:

- tCAS lub CAS Latency (Column Address Strobe Latency) – określa liczbę cykli pomiędzy wysłaniem adresu kolumny do pamięci a momentem otrzymania danych w odpowiedzi, przy założeniu, że właściwy wiersz jest już otwarty. Jest to dokładna wartość, która musi zostać ustawiona w kontrolerze pamięci. CL to jeden z ważniejszych parametrów określających szybkość i wydajność układu pamięci.

- tRCD (RAS to CAS Delay) – jest to minimalna liczba cykli zegara pomiędzy otwarciem wiersza pamięci a dostępem do znajdujących się w nim kolumn. Czas odczytu pierwszego bitu z pamięci bez aktywnego wiersza równy jest sumie tRCD + CL.

- tRP (Row Precharge Time) – jest to minimalna liczba cykli zegara potrzebnych do wykonania sekwencji zamknięcia aktywnego wiersza, wstępnego ładowania nowego wiersza i dostępu do nowego wiersza. Czas odczytu pierwszego bitu pamięci z pamięci DRAM z otwartym niewłaściwym wierszem wynosi zatem tRP + tRCD + CL.

- tRAS (Row Active Strobe Time) – jest to minimalna liczba cykli zegara wymagana pomiędzy aktywacją danego wiersza a jego zamknięciem – pojawieniem się komendy wstępnego ładowania nowego wiersza. Minimalna wartość będzie zawsze większa od sumy opóźnień CL i tRCD.

Opóźnienia dla danej pamięci podaje się zazwyczaj w formacie: CL – tRCD – tRP – tRAS, lub krócej: CL – tRCD – tRP (rysunek 10).

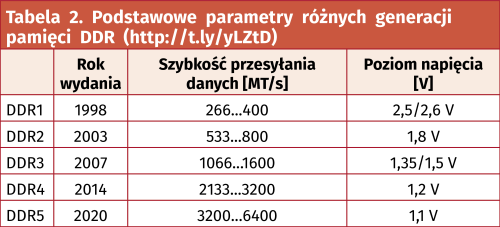

Dziś dostępne są pamięci DDR generacji 5. określane skrótem DDR5. Jednak stosuje się je tylko w najbardziej wymagających aplikacjach, podczas gdy w systemach embedded powszechne są pamięci od DDR2 do DDR4. W tabeli 2 zestawiono podstawowe parametry kolejnych generacji pamięci DDR.

Energooszczędna pamięć DDR

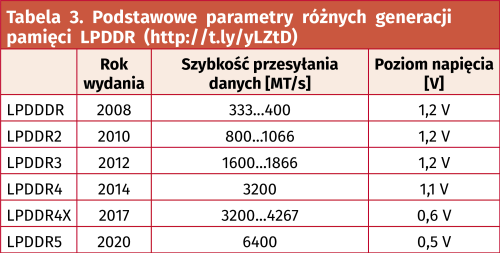

Pamięci RAM przeznaczone do takich aplikacji, jak smartfony, ultrabooki i urządzenia IoT, zostały zoptymalizowane pod kątem zapewniania wysokiej wydajności przy jednoczesnym niskim zużyciu energii. Tak powstały układy LPDDR (Low Power Double Data Rate). Zasadniczą różnicą w stosunku do DDR jest tu niższe napięcie pracy, które może wynosić nawet 0,5 V (LPDDR5) – tabela 3.

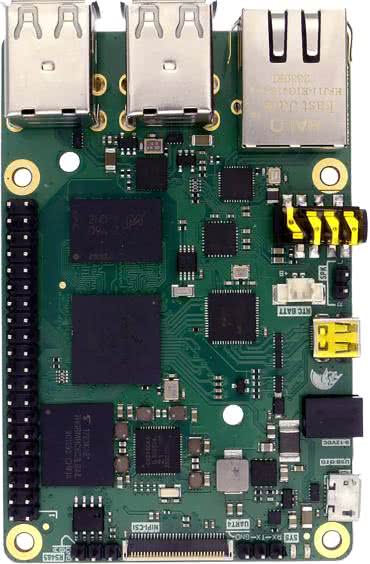

Najnowsza generacja energooszczędnych pamięci – LPDDR5 – stosowana jest przede wszystkim w smartfonach, natomiast szybkie i energooszczędne pamięci LPDDR4 napotkamy w wydajniejszych komputerach SBC – na fotografii 5 pokazano komputer jednopłytkowy typu TitanSBC wyposażony w procesor i.MX8, współpracujący z 4 GB pamięci LPDDR4.

Dodatkowe właściwości pamięci

ECC/Non-ECC

Pamięć ECC (Error Checking and Correcrion, Error Correction Code) jest wyposażona w system kodowania korekcyjnego. Zasada jej działania bazuje na rozbudowie szyny danych pamięci. Dzięki poszerzeniu szyny danych powstaje możliwość przesyłania dodatkowych informacji, w tym przypadku – informacji kontrolnych. Układy ECC pozwalają na znacznie stabilniejsze działanie systemu niż w przypadku pamięci non-ECC – oferują także możliwość korekcji błędów jednobitowych oraz detekcji błędów dwubitowych. Pamięci ECC obsługiwane są jedynie pod warunkiem, że dany system został do tego odpowiednio przystosowany.

Buffered/Unbuffered

Pamięć buforowana/niebuforowana określana jest też jako pamięć registered/unregistered. Bufory czy też rejestry, które pojawiają się w module pamięci, służą jako układy podtrzymujące przekazywany sygnał. Ich zadaniem jest synchronizacja przekazu sygnałów, zarówno sterujących, jak i pochodzących z magistrali adresowej do pamięci. Takie działanie zwiększa stabilność systemu. Kosztem tego jest zwiększenie czasu dostępu do pamięci z uwagi na większą liczbę użytych układów.

Podsumowanie

W nowoczesnych systemach embedded, takich jak moduły SoM i SBC, w roli NVM królują układy pamięci eMMC. Pomimo zalet tej technologii, wielu producentów stosuje równolegle drugi typ pamięci, np. QSPI. Jako pamięć operacyjną znajdziemy dziś najczęściej układy DDR4, charakterystyczne dla komputerów typu PC, a procesor główny obowiązkowo powinien mieć wbudowany akcelerator AI – przykład takiego rozwiązania, w postaci modułu VisionSOM-V2L, można zobaczyć na fotografii 6.

Takie zestawienie komponentów sprawia, że niewielki moduł SoM jest w stanie sprostać naprawdę wielkim wyzwaniom.

Damian Sosnowski, EP

Zaloguj

Zaloguj