Zasada działania enkodera obrotowego

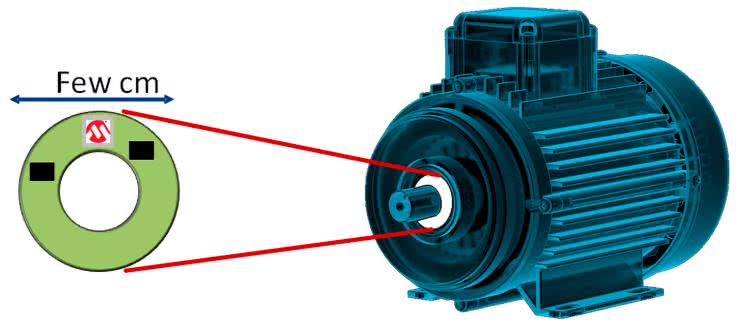

Enkodery obrotowe precyzyjnie mierzą położenie kątowe silnika elektrycznego, umożliwiając jego dokładne sterowanie. Enkodery te są zwykle montowane blisko wału silnika, tak jak pokazano na rysunku 1.

Wiąże się to ze znacznymi ograniczeniami systemowymi:

- płytka drukowana (PCB) w kształcie pierścienia daje niewiele miejsca na rozmieszczenie komponentów,

- wysoka temperatura pracy silnika oznacza wysoką temperaturę elektroniki,

- wysoka temperatura oraz drgania i wibracje wpływają na zmniejszoną niezawodność i żywotność elektroniki.

Ograniczenia te powodują, że wszelkie rozwiązania elektroniczne wymagają najbardziej niezawodnych komponentów o niewielkim samonagrzewaniu i niewielkiej powierzchni. Ponieważ enkodery obrotowe są zwykle produkowane w dużych ilościach, koszt chłodzenia systemu i produkcji płytek PCB jest ważnymi czynnikiem projektowym.

Dodatkowym czynnikiem istotnym w systemach tego typu jest bezpieczeństwo funkcjonalne, które zapewnia wiarygodność wartości pomiarowych i prawidłowe reakcje na stany awaryjne, takie jak doprowadzenie do stanu bezpiecznego - zatrzymania.

Średnica typowej płytki PCB w kształcie pierścienia, przystosowanej do takiej aplikacji, spada do ok. 35 mm, co ogranicza fizyczny rozmiar wybranych komponentów do około 10×10 mm² lub mniej. Na płytę enkodera wpływa bezpośrednio ciepło wytwarzane przez silnik i w warunkach pracy może osiągnąć temperaturę 95°C, a okresowo nawet 105°C. W takich temperaturach samonagrzewanie się elektroniki na skutek prądów upływowych jest już bardzo istotne - niektóre półprzewodniki mogą nawet cierpieć na niekontrolowaną niestabilność cieplną.

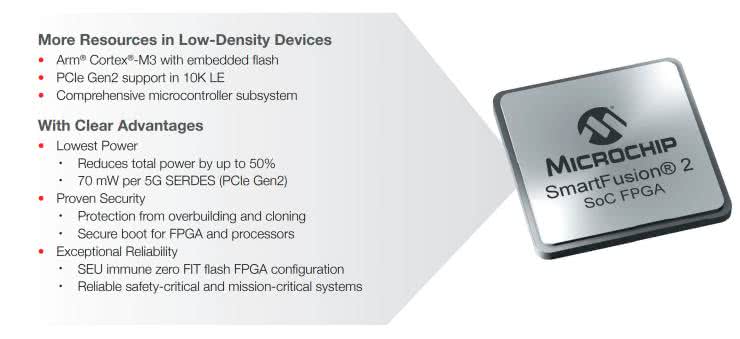

SmartFusion 2 SoC FPGA

Inżynierowie firmy Microchip specjalnie do takich aplikacji zaprojektowali układ SmartFusion 2 SoC FPGA w obudowie FCSG158. Jest to mikrosystem wyposażony w mikrokontroler Arm Cortex M3 (MCU) z dołączoną strukturą FPGA złożoną z około 25 000 elementów logicznych (LE) i z pakietem bloków peryferyjnych o łącznych wymiarach 9×9 mm² (rysunek 2). Układ jest wysoce zoptymalizowany pod kątem trudnych warunków pracy i ograniczeń konstrukcyjnych.

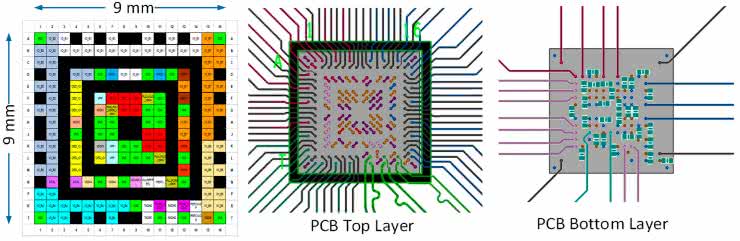

Pomimo niewielkiej obudowy, układ został zoptymalizowany pod kątem routingu i umożliwia w pełni funkcjonalną aplikację za pomocą tylko dwóch warstw sygnału na płytce PCB. Dzięki temu płytka PCB nie jest skomplikowana i jest tania w produkcji. Wolna przestrzeń w siatce padów układu pozwala na zastosowanie ekonomicznych przelotek 0,3 mm dla pierścienia wewnętrznego i umieszczenie kondensatorów odsprzęgających bezpośrednio pod układem w pobliżu wyprowadzeń zasilających pośrodku pakietu (rysunek 3).

SmartFusion 2 FPGA zapewnia 82 wejścia/wyjścia, z których 70 może łączyć się z napięciem 3,3 V, a 12 z nich może natywnie łączyć się z napięciem 2,5 V lub poprzez dzielniki rezystancyjne z napięciem 3,3 V. Dodatkowo w sytuacjach wymagających szybkiej komunikacji dostępna jest jedna para transceiverów, która może pracować z szybkością do 5 Gb/s i obsługuje PCIe Gen2. Wbudowany w chip M3 transceiver można również zastosować do typowych zadań komunikacyjnych.

Dzięki zoptymalizowanej pod względem mocy architekturze układu FPGA SmartFusion 2 i wynikającemu z niej niewielkiemu samonagrzewaniu urządzenie może pracować w temperaturach otoczenia bliskich maksymalnie określonemu zakresowi temperatur (100/125°C). Aby uzyskać dokładne szacunki zużycia energii i samonagrzewania urządzenia, zaleca się użycie narzędzia Microchip Power Estimator dla układów SmartFusion 2 SoC, IGLOO 2 FPGA lub PolarFire FPGA i SoC.

Bezpieczeństwo aplikacji

Jak wspomniano wcześniej, dane enkodera są często krytyczne dla bezpieczeństwa aplikacji, a projekt FPGA musi również mieć certyfikat bezpieczeństwa. Taki certyfikat bezpieczeństwa wspierany jest przez Microchip pakietem bezpieczeństwa SmartFusion 2/IGLOO 2 FPGA. Urządzenia SmartFusion 2 i IGLOO 2 FPGA mają certyfikat bezpieczeństwa funkcjonalnego zgodnie z normą IEC 61508. Odpowiedni pakiet bezpieczeństwa zawiera certyfikowane pod względem bezpieczeństwa środowisko programistyczne Libero SoC Design Suite wersja 18.3 SP4, 28 rdzeni IP, które są bardzo często wymagane w projektach FPGA oraz podręcznik bezpieczeństwa dla tych urządzeń i narzędzi, aby obliczyć prawdopodobieństwo awarii sprzętu.

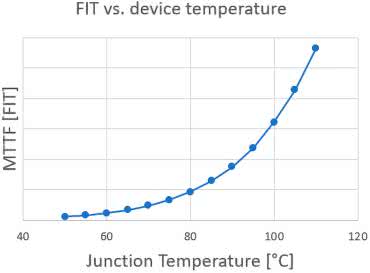

Ponieważ nasze układy FPGA i SoC są odporne na zakłócenia spowodowane pojedynczym zdarzeniem (SEU - Single Event Upset) w pamięci konfiguracyjnej, trwałe awarie sprzętu są jedynymi czynnikami wpływającymi na obliczenia FIT wymagane do dyskusji na temat bezpieczeństwa. FIT (Failures in Time) oznacza awarię w czasie, a jeden FIT oznacza jedną awarię w ciągu 109 godzin. W przypadku typowych układów FPGA bazujących na pamięci SRAM miękkie FIT powodowane przez SEU zależy od dokładnej architektury i złożoności wybranego urządzenia i zazwyczaj mieści się w zakresie około 400 FIT.

Oznacza to, że funkcje istotne dla bezpieczeństwa zajmują zwykle tylko ułamek struktury FPGA. Do tego miękkiego FIT dodawane są trwałe awarie.

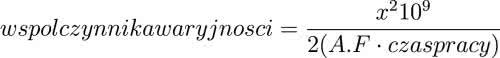

Wskaźnik FIT dla trwałych awarii ustala się na podstawie danych pomiarowych dostawcy przy podwyższonym poziomie obciążenia urządzenia, aby przyspieszyć efekty starzenia, które głównie przyczyniają się do awarii urządzeń. Wyniki tych pomiarów stanowią podstawę do obliczenia współczynnika awaryjności sprzętu w pożądanych warunkach operacyjnych w oparciu o zależność Arrheniusa:

gdzie:

A.F - współczynnik przyspieszenia

Wizualny wynik tego obliczenia pokazuje wykres na rysunku 4.

Podczas wykonywania obliczeń dla kompletnego układu FPGA uzyskany współczynnik FIT w temperaturach otoczenia > 90°C, w jakich często pracują enkodery obrotowe, może dać współczynnik awaryjności około 100 FIT. W przypadku konstrukcji bezpiecznych funkcjonalnie jest to zdecydowanie za dużo.

Innymi słowy, należy albo utrzymywać niską temperaturę urządzenia, albo - ze względów bezpieczeństwa - zachować niewielki rozmiar struktury.

Nasz pakiet bezpieczeństwa zawiera odpowiednie dane i narzędzia do określenia współczynnika FIT części całego projektu, istotnej dla bezpieczeństwa. Pomaga to w uzyskaniu certyfikatu projektu. Ponadto współpracujemy z ekspertami branżowymi, którzy mogą świadczyć usługi doradcze w zakresie projektów bezpieczeństwa funkcjonalnego. W przypadku układów FPGA jest to Expleo, które jest dostępne w 30 różnych krajach na całym świecie.

Podsumowanie

Microchip zapewnia kompletny pakiet urządzeń zoptymalizowanych pod kątem zastosowań z enkoderami obrotowymi wraz z pakietem bezpieczeństwa i ekspertami doradczymi. Aby dowiedzieć się więcej, skontaktuj się z odpowiednim przedstawicielem firmy Microchip.

Martina Kellermanna

Microchip

Zaloguj

Zaloguj