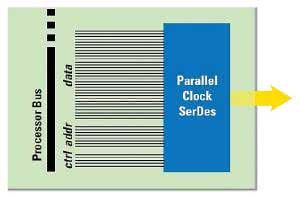

SerDes z równoległą linią zegara zazwyczaj jest wykorzystywany do obsługi tradycyjnych magistral przesyłających dane, adresy i sygnały kontrolne. Działa jak jednokierunkowy konwerter "wirtualnego kabla wstążkowego".

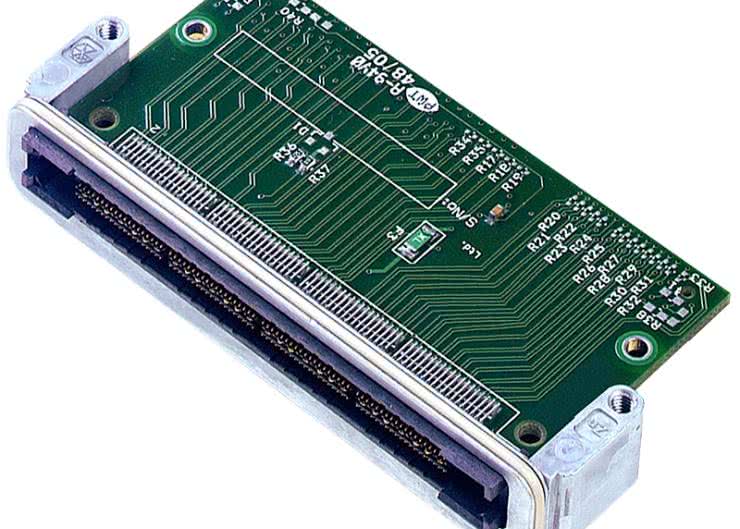

Konwerter SerDes z równoległą linią zegara

Rysunek 1. SerDes z równoległą linią zegara towarzyszy tradycyjnym, szerokim magistralom równoległym, które przesyłają adres, instrukcje sterujące i dane

SerDes z równoległą linią zegara ma przewagę nad brakiem serializacji ze względu na mniejszą liczbę linii (zwłaszcza masy), niższy pobór mocy, możliwość wysterowania dłuższych linii, mniejszy poziom szumów/zakłóceń elektromagnetycznych i mniejszy koszt przewodów oraz łączy.

To rozwiązanie nie jest ograniczone do jednej pary szeregowej - połączenia SerDes z równoległą linią zegara mogą być dowolnie szerokie i jednocześnie pozwala uniknąć problemów projektowych związanych z bardzo wysokimi szybkościami danych szeregowych (rysunek 1).

Opisywane rozwiązanie oferuje bardzo korzystny stosunek wydajności do ceny i często stanowi jedyny praktyczny sposób na połączenie tradycyjnej szerokiej magistrali równoległej za pomocą kilkumetrowego kabla. Popularne szerokości magistral równoległych, które są spotykane w układach, to 21, 28 i 48 bitów.

Typowe zastosowania obejmują wyświetlacze laptopów, bezpośrednie połączenia między gniazdami w telekomunikacji i transmisji danych oraz łącza kamer i aparatów.

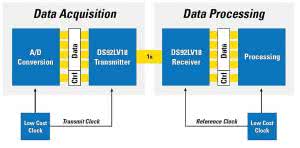

Konwerter SerDes z bitami startu i stopu

Bity startu i stopu są praktyczne w systemach, które transmitują surowe dane wraz z dodatkowymi sygnałami kontrolnymi, bitami parzystości, ramką, synchronizacją, bitami statusu itp. Przykład zastosowania serializacji 18 bitów został przedstawiony na rysunku 2.

18-bitowy nadajnik serializuje nie tylko dane, ale też dwa dodatkowe bity z informację o parzystości i ramce. Te bity są serializowane razem z danymi z normalna częstotliwością pracy przetwornika analogowo-cyfrowego, zatem nie ma potrzeby stosowania dodatkowych buforów czy układów logicznych.

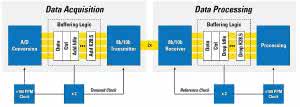

Wykorzystanie jednobajtowej serializacji 8b/10b w tym systemie byłoby bardziej skomplikowane (rysunek 3). Dodatkowe informacje kontrolne niemieszczące się w jednym bajcie musiałyby być buforowane i wysyłane w postaci całego bajtu.

Symbol przecinka K28.5 także musiałby być przesłany na początku synchronizacji łącza, co wymaga dodatkowego układu logicznego. Te dodatkowe dane niebędące danymi wymagają od układu SerDes szybszej pracy, niż minimum potrzebne do konwersji danych.

Przekłada się to na wyższe wymagania odnośnie technologii wykonania backplane czy połączeń kablowych. Konieczny jest również mechanizm dodawania i usuwania pustych danych. O ile w systemach komunikacyjnych buforowanie tego typu zazwyczaj już istnieje, o tyle w wielu innych zastosowań takie dodatkowe przetwarzanie i buforowanie trzeba by dodać samemu.

Dodatkową cechą sygnału zegara umieszczonego w sygnale jest możliwość automatycznej synchronizacji z przypadkowymi danymi. Jest to szczególnie użyteczne, gdy odbiornik stanowi oddzielny moduł poza bezpośrednią kontrolą systemu oraz gdy nadajnik transmituje sygnał do wielu odbiorników.

W razie takiej transmisji nowy moduł odbiornika dodany do magistrali będzie w stanie zsynchronizować się z dowolnymi danymi bez przerywania transmisji dla innych odbiorników i przesyłania dodatkowych sekwencji czy znaków.

Zegar umieszczony w sygnale sprawia, że deserializer synchronizuje się ze strumieniem i śledzi narastające zbocza w odbieranym sygnale. Zegar referencyjny jest potrzebny tylko podczas początkowej synchronizacji, aby uniknąć detekcji fałszywej harmonicznej.

To rozwiązanie pozwala tolerować jitter przynajmniej o rząd wielkości większy zarówno w referencyjnym sygnale zegarowym, jak i sygnale transmitowanym. Dzięki temu można obniżyć koszt układu zegarowego i sieci dystrybucji sygnału zegarowego. W wielu sytuacjach do generacji referencyjnego sygnału zegarowego w odbiorniku są używane niedrogie oscylatory klasy PC.

Zapisanie bitów sygnału zegarowego w transmisji jest praktyczne w zastosowaniach, które nie posługują się bajtami - na przykład transmisji surowych danych wraz z sygnałami kontrolnymi. Zastosowania mogą obejmować systemy przetwarzania sygnałów, takie jak stacje bazowe, obrazowanie i obsługa wideo w pojazdach, a także systemy czujnikowe, w których przetwornik analogowo-cyfrowy, kamera lub czujnik obrazu przesyła surowe dane do urządzenia odpowiedzialnego za ich obróbkę.

Konwerter SerDes z kodowaniem 8b/10b

Wykorzystanie metody kodowania 8b/10b jest odpowiednie dla danych, które składają się z bajtów (rysunek 3). Przykładem są pakiety przesyłane przez backplane, kabel lub światłowód. Wiele standardów, takich jak Ethernet, Fiber Channel, InfiniBand i inne wykorzystują popularne kodowanie 8b/10b z przepustowością 1,0625; 1,25; 2,5 lub 3,125 Gbps. Jest dostępnych wiele urządzeń SerDes obsługujących te szybkości transmisji.

Kodowanie 8b/10b zapewnia, że najdłuższa możliwa sekwencja tych samych symboli (zer lub jedynek) nie przekracza 5 bitów. Pozwala to ograniczyć widmo sygnału szeregowego, co jest pomocne, gdy zachodzi konieczność tłumienia emisji elektromagnetycznej.

Dla przykładu, linia o przepustowości 1 Gbps korzystająca z kodowania 8b/10b ma najwyższą harmoniczną o częstotliwości 1 GHz, a najniższą - 1 GHz/5 = 200 MHz. Odpowiadające im częstotliwości podstawowe to 500 MHz i 100 MHz.

Szeregowe strumienie 8b/10b są pozbawione składowej stałej - średnia różnica między liczbą zer a jedynek w strumieniu jest równa 0. Różnica liczby zer i jedynek w słowach kodowych 8b/10b wynosi w każdym przypadku +2, 0 lub -2, zatem dla całego strumienia również nie przekracza zakresu -2/+2.

Kodowanie usuwające składową stałą i krótkie serie powtarzanych impulsów są konieczne, by zapewnić niezawodną pracę w systemie ze sprzężeniem AC lub światłowodami. Jest to główna zaleta kodowania 8b/10b w szeregowych łączach optycznych. Dodatkowo usuwanie składowej stałej redukuje interferencje międzysymbolowe, co pozwala na wysterowanie dłuższych kabli.

Kodowanie 8b/10b stanowi również sposób wykrywania błędów i przesyłania informacji kontrolnych. Wykrywanie błędów opiera się na fakcie, że większość możliwych kombinacji 10-bitowych kodów nie jest dostępna wśród słów kodowych 8b/10b.

Dzięki temu układy deserializacji 8b/10b mogą wykryć nieprawidłowe kody i zapewnić wykrywanie błędów zbliżone do metody bitów parzystości. O ile ta metoda nie pozwala na zliczenie liczby przekłamanych bitów, jest dobrym sposobem na monitorowanie działania łącza szeregowego.

Poza słowami kodującymi dane, wiele standardów definiuje też słowa kontrolne - takie jak znaczniki ramki czy pakietu, flagi błędów i znaki wyrównania. Te słowa kontrolne pomagają systemowi na budowanie o odczytywanie pakietów, co sprawia, że kodowanie 8b/10b jest bardzo popularne w urządzeniach przetwarzających dane w systemach komunikacji.

Porównanie architekturKażda z omówionych architektur SerDes ma pewne zalety, które sprawiają, że szczególnie nadaje się do konkretnych zastosowań. Systemy z równoległą linią zegara są tanie i w wygodny sposób pozwalają serializować szerokie magistrale. Są tanie, ponieważ sygnał zegarowy jest transmitowany do odbiornika równolegle, zatem nie ma potrzeby odtwarzania sygnału zegara. Jednak stanowi to również poważną wadę, ponieważ wykorzystanie wielu linii szeregowych i zegarowych wymaga ostrożnego prowadzenia przewodów i małych przesłuchów między parami linii. Rozwiązania SerDes przesyłające sygnał zegarowy w strumieniu są doskonałe tam, gdzie zachodzi potrzeba transmisji kilku dodatkowych bitów lub synchronizacji z losowymi danymi. Mają również mniejsze wymagania odnośnie do jakości sygnału zegarowego nadajnika i sygnału referencyjnego, co pozwala na stosowanie tanich układów zegarowych. Jednak brak wbudowanej funkcji usuwania składowej stałej nie pozwala na stosowanie ich w przypadku sprzężenia AC i wysterowania modułów optycznych. Warto zauważyć, że 24-bitowe moduły SerDes mają funkcję usuwania składowej stałej, zatem to ograniczenie dotyczy tylko układów 10-, 16- i 18-bitowych. SerDes z kodowaniem 8b/10b sprawdza się w przypadku danych pogrupowanych w bajty lub pakiety. Kodowanie 8b/10b pozwala na łatwe wykrywanie błędów i usuwa składową stałą, co prowadzi do obniżenia poziomu interferencji międzysymbolowych i transmisji przez linie ze sprzężeniem AC, jak też światłowody. Jednak stosowanie kodowanie 8b/10b w przypadku, gdy szerokość magistrali nie jest wielokrotnością bajtu wymaga dodatkowych zabiegów w celu podziału danych na bajty, a co za tym idzie - pracy łącza z wyższą szybkością. |

Konwertery SerDes jako interfejsy FPGA

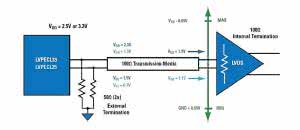

Układy SerDes dołączane do FPGA w naturalny sposób znajdują miejsce w zastosowaniach, które wykorzystują FPGA i wymagają serializacji danych wysokich szybkości przesyłanych stratnymi łączami. Takie rozwiązanie działa zarówno w systemach ze sprzężeniem AC jak i DC (rysunek 4).

Deserializer automatycznie synchronizuje się z nadchodzącymi danymi bez użycia zewnętrznego zegara referencyjnego ani dodatkowych symboli, co umożliwia łatwą pracę od razu po połączeniu układów. Ta cecha sprawia, że SerDes jest wygodny w systemach, w których dane nie są pogrupowane w bajty lub też w transmisji surowych danych. Przykłady obejmują cyfrowe systemy przetwarzania sygnałów, takie jak stacje bazowe, systemy obrazowania i wideo, a także systemy czujnikowe.

Zintegrowane metody kondycjonowania sygnału, jak deemfaza po stronie nadajnika, usuwanie składowej stałej, programowalny zakres napięcia Vod i korekcja częstotliwości po stronie odbiornika sprawiają, że jest to bardzo atrakcyjne rozwiązanie w systemach, które wymagają transmisji dużych ilości danych przy użyciu niedrogich łącz, takich jak CAT-5 lub backplane wykonane z materiału FR4.

Co więcej, integracja elementów powoduje obniżenie całkowitego kosztu systemu i elementów na płytce. Przykładowe zastosowania obejmują łącza między urządzeniami, rozpoznawanie obrazu, panele LED, obrazowanie medyczne i różne systemy bazujące konstrukcyjnie na backplane.

SerDes w postaci przystawki FPGA w naturalny sposób sprawdza się w systemach, które zawierają FPGA i muszą przesłać duże ilości danych przez tanie łącza, takie jak CAT-5 lub ścieżki prowadzone na laminacie FR4. Równoległy interfejs LVDS zmniejsza liczbę wejść/wyjść, pobór mocy, poziom interferencji elektromagnetycznych i wrażliwość systemu na zakłócenia. Deserializer automatycznie synchronizuje się z przychodzącymi danymi bez użycia zewnętrznego zegara referencyjnego lub dodatkowych symboli, co pozwala na szybkie uruchomienie połączenia.

Terminacja i konwersja

Aby zapewnić poprawną pracę łącz wysokiej szybkości, trzeba je traktować jak linie transmisyjne. Należy unikać zmian impedancji i dodać odpowiednią sieć terminacji, jeśli to konieczne. Prawidłowa terminacja jest dopasowana do impedancji linii transmisyjnej (Zl), co powoduje osłabienie odbić. O ile cel stosowania sieci terminacji jest zawsze taki sam, w celu jej realizacji trzeba rozważyć wiele zmiennych, które wpływają na stosowaną metodę terminacji.

Wewnętrzna terminacja ma tę zaletę, że działa tak blisko odbiornika, jak to tylko możliwe - co minimalizuje wpływ rozgałęzień. Jednocześnie powala zaoszczędzić powierzchnię płytki i zmniejszyć liczbę elementów. Jej wadą jest ograniczona możliwość modyfikacji. Przykładowo, wewnętrzna terminacja AC zakłada, że przychodzące dane będą pozbawione składowej stałej. Odbiornik LVDS z wewnętrzną terminacją może okazać się nieprzydatny w konfiguracji multidrop ze względu na dodatkowe obciążenie.

Terminacja i dopasowanie impedancji

Aby wyeliminować odbicia, impedancja charakterystyczna linii transmisyjnej musi być stała i równa terminacji obciążenia. Spełnienie tego warunku staje się skomplikowane, jeśli ścieżka zawiera rozmaite ścieżki, kable, przelotki i złącza. Co więcej, terminacja obciążenie może również stanowić zabezpieczenie systemu na wypadek awarii lub układ konwersji sygnału.

Standardy B-LVDS oraz M-LVDS zapewniają wyższy prąd sterownika, niż konwencjonalny LVDS, co pozwala im wysterować systemy w topologii multidrop i multipoint. W każdym z przypadków rekomendowanym rozwiązaniem jest dopasowanie efektywnej impedancji na końcu każdej ścieżki płyty tylnej.

Rezystory terminujące są dopasowane do efektywnej impedancji płyty tylnej. Impedancja charakterystyczna płyty może wynosić 100 Ω, ale dodatkowe obciążenie wnoszone przez złącza i karty może sprawić, że efektywna impedancja będzie znacznie niższa. Przykładowo, dla popularnej architektury ATCA impedancja charakterystyczna płyty wynosi 130 Ω, ale na skutek dodatkowego obciążenia kartami płyta jest terminowana wartością 80 Ω.

Sprzężenie AC to technika terminacji, w której kondensatory umieszczone są szeregowo na obu liniach pary różnicowej, poza standardową pasywną terminacją po stronie obciążenia. Istnieje kilka powodów, dla których to rozwiązanie jest pożądane - ma związek z wydajnością, kompatybilnością i możliwymi problemami systemu.

Kondensatory usuwają całkowicie składową stałą sygnału, zatem tylko zbocza narastające i opadające będą widoczne na odbiorniku. Padająca fala naładuje obwód, po czym energia zostanie stopniowo rozładowana w czasie zależnym od stałej RC.

Realizacja sprzężenia AC 2 ma następujące zalety:

- Przebieg wejściowy na odbiorniku będzie symetryczny względem napięcia obciążenia (Vbias). Dzięki temu odbiornik może pracować w optymalnym zakresie napięć, co przyczynia się do obniżenia jitteru i lepszych parametrów.

- Ponieważ techniki CML i LVPECL nie mają ustalonego standardu, nie istnieją ścisłe reguły ustawienia progów napięcia w układach. Sterowniki i odbiorniki potencjalnie mogą należeć do różnych dostawców, zatem sprzężenie AC eliminuje ewentualną różnicę progu, jaka może wystąpić między urządzeniami.

- Sprzężenie AC eliminuje różnicę poziomu między sterownikiem a odbiornikiem, zatem pozwala na łatwą konwersję między różnymi technologiami. To zagadnienie zostało dokładniej omówione w dalszej części.

- Innym powodem stosowania sprzężenia AC jest zabezpieczenie przed różnicami potencjału mas między różnymi kartami czy systemami. Jeśli kabel łączy dwa różne urządzenia z różnymi potencjałami masy, powstałe napięcie może wpłynąć na pracę pary różnicowej - w ekstremalnych sytuacjach zagrozić prawidłowej transmisji. Sprzężenie AC eliminuje stałą różnicę napięć, zatem całkowicie rozwiązuje problem.

Sprzężenie AC jest najczęściej stosowane przy wysokich szybkościach i urządzeniach CML oraz LVPECL. W praktyce wiele urządzeń zawiera kondensatory stanowiące wewnętrzną terminację odbiornika. Jednak potencjalna wadą sprzężenia AC jest konieczność usunięcia składowej stałej ze strumienia danych.

Usuwanie składowej stałej polega na minimalizacji różnicy między całkowitą liczbą jedynek i zer w strumieniu danych. Jeśli liczba zer i jedynek jest równa, przyjmuje się, że sygnał jest pozbawiony składowej stałej. Jest to ważne, ponieważ w przypadku użycia kondensatorów prąd płynie do odbiornika tylko podczas zmiany stanu. Jeśli zmiany stanu nie następują, ładunek między wejściami odbiornika powoli odpływa, co zmniejsza margines szumów.

Rozmaite techniki kodowania, takie jak 8b/10b, zapewniają wysoki stopień zrównoważenia. O ile brak składowej stałej odnosi się do całego strumienia danych, istnieją inne miary opisujące krótkoterminowe odstępstwo od ideału.

Długość ciągu to istotny parametr związany z jitterem. Deterministyczny jitter można zminimalizować, jeśli zmiany sygnału pokrywają się dokładnie z szerokością bitów. Długie ciągi powodują odpływ ładunku w obwodzie RC, który zmniejsza amplitudę sygnału, tym samym zamykając oczko. Zjawisko to prowadzi do wzrostu deterministycznego jitteru. Odpowiednio duży kondensator może pomóc utrzymać amplitudę sygnału.

Systemy często zawierają kombinację różnych technologii różnicowych wysokich szybkości, co prowadzi do konieczności konwersji sygnałów pomiędzy nimi. Najczęściej stosowaną technologia różnicową jest LVDS. Na szczęście w jej przypadku realizacja konwersji jest również najprostsza.

Wejścia LVDS mają największy dopuszczalny zakres składowej sumacyjny spośród wszystkich technologii różnicowych. Dzięki temu produkty LVDS National Semiconductor (aktualnie Texas Instruments) pozwalają na bezpośrednie łączenie z większością urządzeń CML oraz LVPECL (rysunek 5).

Ze względu na szeroki zakres napięcia składowej sumacyjnej LVDS może uchodzić za uniwersalny odbiornik różnicowy. Wejścia CML i LVPECL często ograniczają nadchodzące sygnały do wąskiego zakresu składowej sumacyjnej. W takiej sytuacji napięcie wyjściowe LVDS może znaleźć się poza dopuszczalnym zakresem wejściowym CML, co pokazano na rysunku 6.

Andrzej Gawryluk, EP

Zaloguj

Zaloguj