Wymagania aplikacji stale rosną co spowodowało, że projektanci sprzętu powinni brać pod uwagę nowe technologie, jak CML (Current-Mode Logic) i kondycjonowanie sygnału zarówno dla LVDS, jak i CML. Z tego powodu czwarta edycja standardu zawiera praktyczne porady projektowe dla tych technologii, jak również dla LVPECL oraz LVCMOS.

Przegląd interfejsów wysokich szybkości

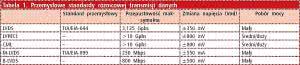

W przypadku sygnałów różnicowych wysokiej szybkości do wyboru jest wiele opcji. Rozwiązania różnicowe zazwyczaj mają podobne charakterystyki, ale różnią się znacząco pod względem wydajności, poboru mocy i docelowymi zastosowaniami. W tabeli 1 przedstawiono kilka atrybutów najbardziej popularnych technologii transmisji różnicowej.

Przemysłowe standardy dla LVDS oraz M-LVD są określone odpowiednio w specyfikacjach ANSI/TIA/ EIA-644A oraz ANSI/TIA/EIA-899. Karty katalogowe niektórych dostawców piszą o zgodności wejść i wyjść z LVDS (lub pseudo-LVDS), ale nie spełniają wymagań odnośnie składowej sumacyjnej i innych istotnych parametrów. Zatem zgodność ze specyfikacją LVDS zawartą w TIA/EIA-644A jest istotnym kryterium, o którym warto pamiętać.

Technologie CML (Current-Mode Logic) i LVPECL (Low-Voltage Positive-Emitter-Coupled Logic) są powszechnie używane, jednak żadna z nich nie jest określona przez oficjalny standard jakiejkolwiek organizacji. Implementacja i specyfikacja urządzeń będzie różna w zależności od dostawcy. Często stosowanym rozwiązaniem jest sprzężenie AC - pozwala ono zniwelować różnice napięć progowych, które mogłyby powodować brak kompatybilności.

Warto zwrócić uwagę, że wszystkie wymienione technologie są różnicowe, zatem mają zalety typowe dla sygnałów różnicowych - wysoką odporność na zakłócenia i niski poziom szumów generowany przez przełączanie układów.

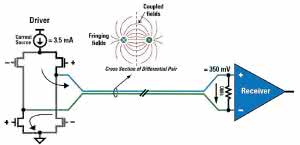

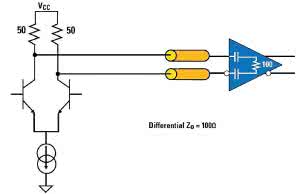

Typowa para sterownik-odbiornik LVDS jest przedstawiona na rysunku 1. Sterownik wyposażono w źródło prądowe o nominalnej wartości natężenia 3,5 mA. Ponieważ impedancja wejściowa odbiornika jest wysoka, praktycznie cały prąd przepływa przez rezystor terminujący 100 V, co przekłada się na nominalną amplitudę 350 mV napięcia pomiędzy wejściami odbiornika.

Próg odbiornika znajduje się na gwarantowanym poziomie 100 mV lub niższym, a taka czułość jest utrzymana w zakresie składowej sumacyjnej od 0 do 2,4 V. Połączenie tych cech zapewnia znakomite marginesy szumów i tolerancję przesunięcia składowej sumacyjnej między nadajnikiem a odbiornikiem.

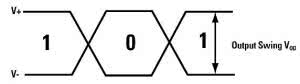

Zmiana kierunku prądu powoduje taką samą amplitudę napięcia na odbiorniku, lecz przeciwną polaryzację. W ten sposób generowane są poziomy logiczne 0 i 1. Rozwiązania CML oraz LVPECL mają podobną architekturę, ale różnią się wydajnością źródeł prądowych i sposobem terminacji.

Prosty schemat z rysunku 2 obrazuje zalety wspólne dla wszystkich różnicowych technik transmisji sygnałów. Po pierwsze, źródło prądowe jest zawsze włączone i przewodzi w różnych kierunkach podczas wysterowania logicznej jedynki lub zera. Takie rozwiązanie eliminuje zakłócenia impulsowe i interferencje elektromagnetyczne powstające wskutek przełączania tranzystorów przewodzących duże prądy.

Problem ten często występuje w przypadku transmisji jednokierunkowej. Po drugie, linie różnicowe znajdują się blisko siebie, co daje znaczącą odporność na zakłócenia. Szum pochodzący z przesłuchów czy interferencji pojawia się na obu liniach jednocześnie.

Ponieważ odbiornik reaguje na różnicę między oboma kanałami, szum "sumacyjny" pojawiający się na obu liniach zostanie odjęty na odbiorniku. Dodatkowo, ponieważ obie linie przewodzą ten sam prąd, lecz w przeciwnych kierunkach, generowane zakłócenia elektromagnetyczne są minimalne.

LVDS - niskonapięciowe sygnały różnicowe

Typowa amplituda sygnałów LVDS to 350 mV, co umożliwia minimalizację poboru mocy. Łatwa terminacja, mały pobór mocy i niski poziom generowanych szumów sprawiają, że LVDS jest bardzo popularnym wyborem dla szybkości transmisji od dziesiątek Mbps do 3 Gb/s i wyższych.

W przypadku wyższych szybkości transmisji konieczna są takie technologie, jak CML lub LVPECL. Standardy CML i LVPECL pozwalają osiągnąć bardzo wysokie szybkości transmisji, nawet powyżej 10 Gb/s. Uzyskanie takiego transferu wymaga bardzo szybkich i ostrych zboczy sygnału o typowej amplitudzie około 800 mV. Z tego powodu CML i LVPECL zazwyczaj zużywają więcej mocy niż LVDS.

Szybko narastające/opadające zbocza oznaczają dużą zawartość składowych wysokiej częstotliwości, podczas gdy straty transmisji na ścieżkach FR4 rosną z częstotliwością. Wymienione metody wymagają dodatkowego kondycjonowania sygnału w przypadku długich kabli lub ścieżek.

CML (Current-Mode Logic)

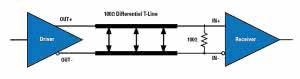

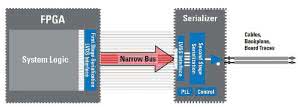

CML jest interfejsem wysokiej szybkości umożliwiającym transmisję z jednego punktu do drugiego z przepustowością przekraczającą 10 Gb/s. Jak pokazano na rysunku 3, typową cechą CML są sieci terminacji zintegrowane zarówno w nadajniku, jak i odbiorniku.

CML wykorzystuje pasywne rezystory podciągające do dodatniej szyny, których typowa wartość to 50 Ω. Większość implementacji CML wykorzystuje sprzężenie AC, zatem wymaga danych o zerowej składowej stałej. Usunięcie składowej stałej uzyskuje się poprzez kodowanie, które zapewnia taką samą średnią liczbę jedynek i zer w sygnale cyfrowym.

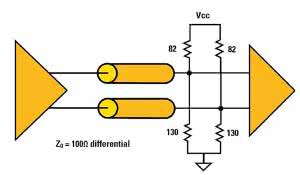

LVPECL - niskonapięciowy interfejs z dodatnim sprzężeniem emiterowym

LVPECL oraz PECL są pochodnymi dawnej technologii ECL wprowadzonej po raz pierwszy w latach ’60 ubiegłego wieku. Typowe napięcia zasilające ECL to 0 V oraz wartość -5,2 V. Ze względu na wymaganą ujemną szynę zasilania i brak kompatybilności z innymi standardami, została wprowadzona odmiana z dodatnią szyną zasilania znana jako PECL (Positive-Emitter-Coupled Logic).

Zarówno ECL, PECL, jak i LVPECL wymagają 50 Ω rezystorów terminujących szynę, która jest około 2 V poniżej szyny dodatniego napięcia. Sterowniki ECL mają małą impedancję ze względu na zastosowanie otwartego emitera i zazwyczaj generują poziomy między 700 a 800 mV.

Stopień odbiornika pozostaje w aktywnym zakresie pracy, co zapobiega nasycaniu i gwarantuje bardzo szybkie i gładkie zbocza sygnału. Do zalet LVPECL należą szybkie i gładkie zbocza oraz wysoka wydajność sterownika. Wady to względnie wysoki pobór mocy i w pewnych sytuacjach konieczność użycia dodatkowej szyny terminującej.

Wybór optymalnego interfejsu

Ze względu na występowanie wielu rodzajów łączy różnicowych potrzebne są pewne wskazówki odnośnie wyboru optymalnego rozwiązania w zależności od zastosowania. Poniższe punkty zawierają najważniejsze czynniki uwzględniane podczas wyboru technologii dla konkretnego zastosowania:

- wymagana przepustowość,

- możliwość wysterowania kabli, płyt tylnych lub długich ścieżek,

- budżet mocy,

- topologia sieci (punkt-punkt, multidrop, multipoint),

- obsługa danych szeregowych lub równoległych,

- dystrybucja zegara lub danych,

- zgodność ze standardami przemysłowymi,

- konieczność lub możliwość kondycjonowania sygnału.

LVDS jest najbardziej popularnym interfejsem komunikacji różnicowej. Niski pobór mocy, minimalny poziom interferencji i znakomita odporność na zakłócenia sprawiają, że interfejs LVDS jest wykorzystywany do wielu zastosowań. Ponadto akceptacja wysokiego poziomu składowej sumacyjnej na wejściu pozwala łatwo współpracować urządzeniom LVDS z innymi technologiami sygnałów różnicowych.

Aktualna generacja LVDS może pracować w paśmie od wartości stałej do 3,125 Gb/s, co pozwala na realizację wielu różnych systemów. Najbardziej wydajne urządzenia LVDS wykorzystują preemfazę i korekcję częstotliwości, aby umożliwić transmisję sygnału przez stratne przewody i ścieżki na płytce drukowanej.

Systemy wymagające przepustowości powyżej 3,125 Gb/s będą najpewniej wymagały zastosowania CML. Ponadto niektóre standardy komunikacji (np. PCIe, SATA czy HDMI) wymuszają użycie określonej technologii lub narzucają szereg ograniczeń, takich jak zgodność amplitudy i napięcia referencyjnego z CML.

W zastosowaniach o szybkości transmisji pomiędzy 2 Gb/s a 3,125 Gb/s optymalny wybór zależy od wymaganej funkcjonalności, wydajności i poboru mocy. Na względnie krótkich dystansach, gdzie kondycjonowanie sygnału nie jest wymagane, kluczowe jest ograniczenie pobieranej mocy i jitteru. Zazwyczaj CML ma najniższy jitter, a LVDS zużywa najmniejszą moc.

Jeśli zachodzi potrzeba przesłania sygnału na dalszą odległość, kluczowym problemem są straty przewodów, a wybór pada na rozwiązanie z najlepszym kondycjonowaniem sygnału dla danej częstotliwości i medium transmisyjnego.

Topologia sieci

Termin "topologia sieci" zazwyczaj odnosi się do fizycznego rozmieszczenia i prowadzenia połączeń węzłów sieci. Znane są takie topologie, jak pierścień, siatka, gwiazda, magistrala czy drzewo. W tym rozdziale zostały omówione typowe topologie sygnałów lub sposoby podłączenia sterowników i odbiorników sygnału do wspólnego medium transmisyjnego - takich, jak ścieżki na płytce drukowanej lub przewody miedziane. Zostały też przedstawione sposoby zastosowania typowych technologii różnicowych w tych sieciach i optymalny wybór rozwiązań dla każdej z topologii.

Istnieją dwie podstawowe topologie: punkt-punkt i wiele punktów (multipoint). Topologia punkt-punkt oznacza, że istnieje tylko jeden sterownik i jeden odbiornik sygnału, topologia multipoint może zawierać wiele sterowników i odbiorników.

Topologia punkt-punkt

Ponieważ topologia punkt-punkt składa się tylko z pary sterownika i odbiornika, medium transmisyjne może być bardzo proste. Zazwyczaj występują nieliczne przejścia między różnymi mediami (na przykład pomiędzy płytką PCB a kablem za pośrednictwem złącza). Minimalna liczba przejść najczęściej oznacza, że ścieżka sygnałowa będzie miała dobrze określoną impedancję.

Sytuacja, w której impedancja jest ściśle kontrolowana, pozwala uzyskać bardzo wysokie szybkości transferu. Choć w przypadku łącz punkt-punkt można wykorzystać każdą technologię różnicową, to LVDS, CML oraz LVPECL zostały zaprojektowane specjalnie z myślą o transmisji punkt-punkt.

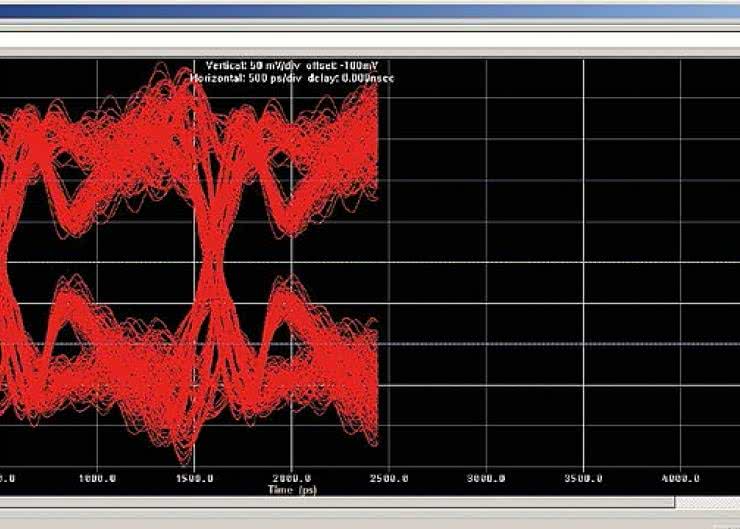

Urządzenia interfejsów LVDS, LVPECL lub CML zawierają wyjścia ze sterownikami o stromych zboczach, które pozwalają na transmisję z szybkością wielu gigabitów. Jednak sygnały o stromych zboczach są bardzo wrażliwe na jakąkolwiek nieciągłość impedancji i wymagają starannego projektowania łącz.

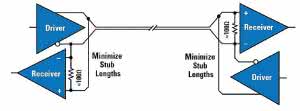

Na rysunku 5 przedstawiono typową parę: sterownik i odbiornik w topologii punkt-punkt. Kontrolowana impedancja łącza, odpowiednie obciążenie odbiornika i terminacja są kluczowymi aspektami projektowania systemu zapewniającego niski jitter transmisji.

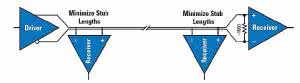

Topologia multipoint/multidrop

W odróżnieniu od topologii punkt-punkt, topologie multipoint mają wiele sterowników i odbiorników sygnału korzystających ze wspólnego łącza. Odmiana topologii multipoint, w której jest tylko jeden sterownik, ale wiele odbiorników, nosi nazwę "multidrop". Pokazano ją na rysunku 6.

Terminacja linii na najbardziej odległym odbiorniku jest zalecana tylko, jeśli sterownik znajduje się po przeciwnej stronie linii. W każdym innym wypadku (na przykład gdy sterownik jest dołączony na środku linii) terminacja musi znaleźć się na każdym z jej końców.

Innym często realizowanym wariantem topologii multipoint jest half-duplex (rysunek 7). Zawiera ona dwie pary sterowników i odbiorników, które nadają sygnał między dwoma punktami, korzystając z jednego łącza.

Fizyczne połączenie wielu sterowników i odbiorników do wspólnej magistrali stanowi wyzwanie dla projektantów topologii multidrop. Głównym problemem jest nieciągłość impedancji na wspólnej linii, którą wywołują obciążenia urządzeń i ich połączenia z magistralą. Dopasowanie impedancji obciążonej magistrali i kontrola zboczy sterowników są kluczowymi metodami realizacji bezbłędnej transmisji sygnału w topologiach multipoint. Istnieją dwie wersje LVDS zoptymalizowane pod tym kątem: Bus LVDS (B-LVDS) i Multipoint LVDS (M-LVDS).

B-LVDS ma wiele cech wspólnych z LVDS, jednak różni się znacznie większym prądem sterownika (10 mA) i kontrolowanymi (wolniejszymi) zboczami sygnału. Wersja B-LVDS została zaprojektowana zwłaszcza pod kątem wysterowania wielu obciążeń i na dobrze zaprojektowanej płycie tylnej jest w stanie obsłużyć do 32 obciążeń. Kontrola nachylenia zboczy w B-LVDS pozwala zmniejszyć odbicia w konfiguracji multidrop występujące przy wielu odbiornikach i towarzyszących im rozgałęzieniach. Wolniejsze zbocza obniżają maksymalną przepustowość B-LVDS, typowo poniżej 1 Gb/s.

Popularyzacja B-LVDS w systemach typu multidrop doprowadziła do opracowania przemysłowego standardu wersji LVDS przeznaczonej dla sieci tego typu. Firma National Semiconductor współtworzyła standard, który jest znany pod nazwą TIA/EIA-899 i technologię Multipoint LVDS (M-LVDS). Standard M-LVDS ma wszystkie atrybuty pożądane w topologii multidrop, jak wyższa wydajność sterowników, powolne kontrolowane zbocza, bardziej zbliżone progi na wejściu i poszerzony zakres składowej sumacyjnej. M-LVDS pozwala na wysterowanie 32 obciążeń przy przepustowości do 250 Mb/s.

Łączenie interfejsów różnych typów

Często zdarza się, że platformy sprzętowe wymagają różnych typów sygnałów zegarowych, kontrolnych i danych. W modularnych systemach komunikacja kart lub przyrządów zachodzi między układami wykonanymi w różnych technologiach przez różnych producentów. Z tego powodu standardy LVDS, LVPECL i CML często współpracują w ramach jednej platformy, a konwersja między jednym rozwiązaniem a drugim jest ważną częścią projektu systemu.

Jedną z możliwych realizacji konwersji jest użycie sprzężenia AC w każdym z kanałów za pomocą kondensatora rozdzielającego różne fragmenty sieci. Wymaga to jednak zrównoważenia danych (usunięcia składowej stałej). W przypadku braku zrównoważenia można zrealizować różnego typu sieci terminujące, które pozwolą na konwersję.

Architektury SerDes

Szeregowe połączenia są kluczowym elementem współczesnych systemów komunikacji. Wybór odpowiedniej techniki serializacji / deserializacji (SerDes) ma zasadniczy wpływ na koszt i wydajność systemu. Choć liczba opcji do wyboru może być przytłaczająca, urządzenia SerDes można przypisać do jednej z kilku podstawowych kategorii, z których każda jest dopasowana do określonych wymagań systemu.

Zrozumienie podstawowych różnic między poszczególnymi architekturami pozwala projektantom szybko wybrać SerDes odpowiedni dla danego zastosowania. W tym rozdziale zostały omówione cztery różne architektury SerDes wraz z funkcją, które pełnią w projekcie systemu

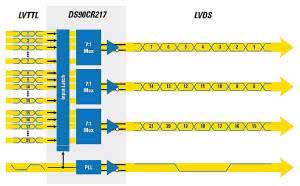

SerDes z równoległą linią zegara

SerDes z równoległym zegarem jest zazwyczaj używany do serializacji magistrali równoległych, które przesyłają dane, adres i instrukcje kontrolne. Należą do nich PCI, UTOPIA, magistrale procesora i magistrale kontrolne. Zamiast obsługiwać całą magistralę za pomocą jednego multipleksera, rozwiązanie z równoległym zegarem wykorzystuje bank multiplekserów n-do-1, z których każdy serializuje oddzielną część magistrali.

Uzyskane w ten sposób szeregowe strumienie danych są przesyłane do odbiornika na wielu równoległych liniach wraz z dodatkowym sygnałem zegarowym, który odbiornik wykorzystuje do synchronizacji i odtworzenia danych. Ponieważ dane i zegar są przesyłane wieloma parami różnicowymi, wahania zegara muszą być ograniczone do minimum, aby zapewnić poprawną deserializację.

SerDes sygnału zawierającego zegar (bity startu i stopu)

Architektura nadajnika realizującego ten tryb serializacji łączy dane magistrali i sygnał zegarowy w jeden sygnał szeregowy. Dwa bity zegara - niski i wysoki - są umieszczone w każdej ramce szeregowego strumienia, wyznaczając początek i koniec każdego serializowanego słowa. Z tego powodu ten rodzaj serializacji nazywa się czasem techniką bitów startu i stopu. Bity startu wyznaczają okresowe narastające zbocze w strumieniu szeregowym. Zaletą tego rozwiązania jest fakt, że długości słów nie są ograniczone do wielokrotności bajtu. Popularne szerokości magistral to 10, 16, 18 i 24 bity.

Po włączeniu zasilania deserializer automatycznie rozpoczyna poszukiwanie okresowego narastającego zbocza zegara. Ponieważ transmitowane dane zmieniają się w czasie, natomiast bity zegara - nie, deserializer jest w stanie zlokalizować zbocza zegarowe i dokonać synchronizacji. Następnie deserializer odczytuje dane ze strumienia szeregowego niezależnie od ich postaci.

Taka automatyczna synchronizacja jest powszechnie nazywana "synchronizacją na losowych danych" i nie wymaga udziału zewnętrznego systemu. Jest to szczególnie przydatna cecha w systemach, w których odbiornik jest modułem znajdującym się w dużej odległości, pozbawionym bezpośredniej kontroli systemu. Ponieważ odbiornik jest zsynchronizowany z zegarem odbieranym w kanale, a nie z zewnętrznym zegarem referencyjnym, wymagania na poziom jitteru w zegarach wejściowych nadajnika i odbiornika nie są tak restrykcyjne.

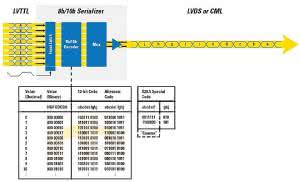

Kodowanie 8b/10b

Rysunek 11. Zewnętrzny SerDes dołączony do FPGA zajmuje się realizacją funkcji analogowych na sygnale odbieranym i wysyłanym przez LVDS

Serializer typu 8b/10b dokonuje konwersji każdego bajtu złożonego z 8 bitów na 10-bitowy kod i przesyła uzyskany 10-bitowy kod przez szeregową parę różnicową. 10-bitowe kody transmisyjne zostały opracowane przez firmę IBM na początku lat 1980 i gwarantują wielokrotne występowanie zboczy sygnału w każdym bajcie oraz usunięcie składowej stałej poprzez równoważenie liczby zer i jedynek. Częste zmiany stanu w strumieniu pozwalają odbiornikowi na synchronizację z odbieranymi danymi. Usunięcie składowej stałej umożliwia stosowanie sprzężenia AC, długich kabli i modułów optycznych.

Aby umożliwić odbiornikowi zlokalizowanie 10-bitowego słowa w szeregowym strumieniu, nadajnik najpierw sygnalizuje początek słowa, przesyłając specjalny symbol zwany przecinkiem. Unikalna sekwencja bitów tego symbolu nigdy nie pojawia się w normalnym strumieniu danych, jest zatem wiarygodnym markerem wyznaczającym wyrównanie słów. Gdy uda się zlokalizować początek słowa, odbiornik może przetłumaczyć 1-bitowe kody z powrotem na bajty, zgłaszając błąd w przypadku odczytu nieprawidłowego 10-bitowego kodu.

Architektury z deserializerem 8b/10b wykorzystują zewnętrzny zegar odniesienia, aby odzyskać sygnał zegara i przeprowadzić deserializację strumienia danych. Z tego powodu wymagają precyzyjnego źródła sygnału zegarowego i kontroli jitteru.

Układ SerDes i FPGA

W systemach SerDes z FPGA funkcje analogowe (jak odzyskiwanie zegara i danych, kondycjonowanie sygnału, synteza zegara i usuwanie jitteru) są realizowane przez zewnętrzne interfejsy warstwy fizycznej.

Interfejs LVDS dołączony do FPGA pozwala uzyskać wysokie szybkości transmisji na mniejszej liczbie ścieżek umieszczonych na płytce drukowanej. Jednocześnie zmniejsza poziom interferencji elektromagnetycznych, pobór mocy i wrażliwość systemu na szumy.

To rozwiązanie eliminuje szumy przełączania i impulsy związane z tradycyjnymi jednokierunkowymi interfejsami, jak LVTTL. Układy SerDes tego typu zazwyczaj wykorzystują metody kondycjonowania sygnału, jak deemfaza, usuwanie składowej stałej i korekcja częstotliwości. Pozwala to zwiększyć wydajność i uzyskać najwyższe przepustowości, a także uzyskać duży zasięg transmisji.

Andrzej Gawryluk, EP

Zaloguj

Zaloguj