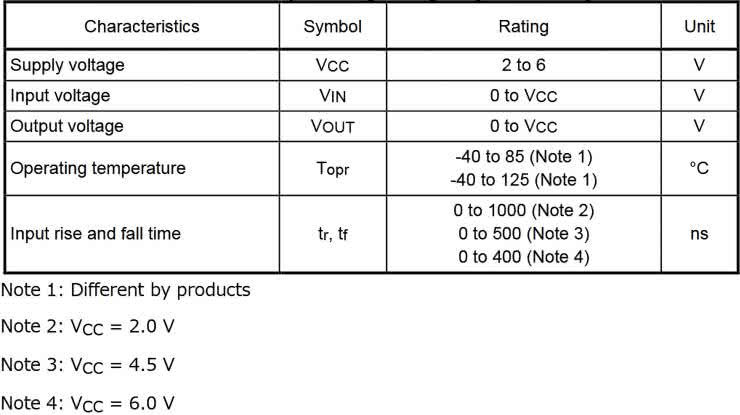

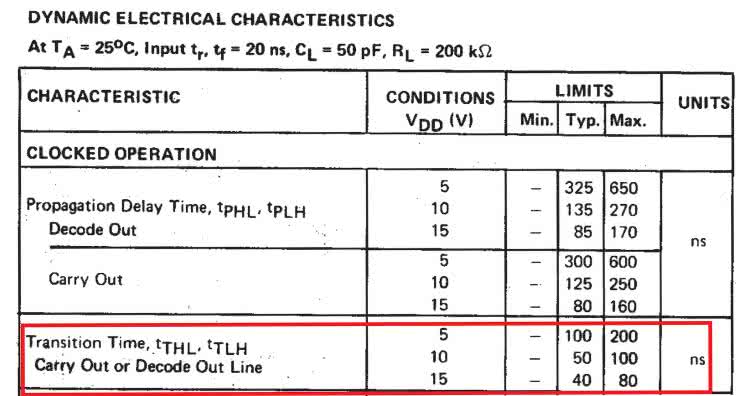

Każda karta katalogowa układu uważanego za cyfrowy (przerzutnik, bramka, mikrokontroler, pamięć itd.) zawiera informację o maksymalnym czasie narastania napięcia wejściowego. Przykładowo dla układów z rodziny HC (rysunek 1) wartość ta mierzona jest w setkach nanosekund i zależy od napięcia zasilającego.

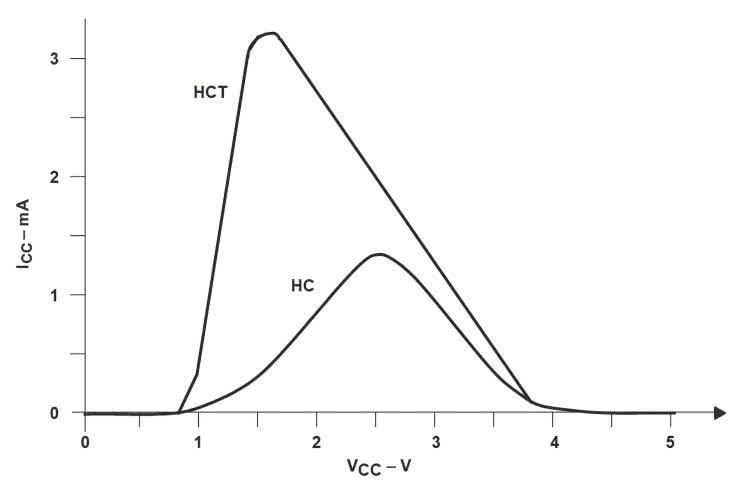

Dlaczego tak jest? To żadna tajemnica: przełączające się tranzystory PMOS i NMOS, tworzące struktury CMOS, przez krótki czas stanowią zwarcie dla linii zasilającej – jeden z nich jeszcze nie otworzył się w pełni, zaś drugi – nie w pełni zatkał. Rysunek 2 pokazuje zależność między pobieranym prądem a napięciem wejściowym dla układów z rodziny HC i HCT.

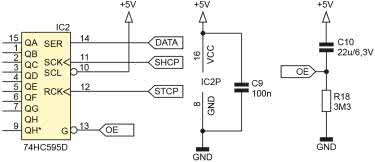

Piszę o nich dlatego, że tych pierwszych używam bodaj najczęściej, a ponadto wiąże się z nimi pewna historia, która była przyczynkiem do powstania tego artykułu: jej bohaterem jest układ 74HC595, czyli ośmiobitowy rejestr przesuwny z wyjściem równoległym. Bardzo lubię te układy i polecam je wielu osobom, ponieważ w stanie spoczynku pobierają prąd o zerowym (niemal) natężeniu i łatwo można je łączyć w kaskady. Jedno z opartych na nich rozwiązań zostało dawno temu zaprojektowane przeze mnie do tego, by skonfigurować stanami logicznymi odpowiednie wejścia większego systemu, po czym układ miał się uśpić i pobierać w tym stanie minimalną ilość energii – odpowiedzialny był za to mikrokontroler ATmega8. Tylko czemu ten mały układzik tyle prądu żre?!

Wszystko było zrobione prawidłowo, z jednym małym „ale”. Otóż przez kilkadziesiąt sekund od włożenia baterii wyjścia 74HC595 miały znajdować się w stanie wysokiej impedancji, aby operator miał czas na włożenie tego urządzenia-konfiguratora do przeznaczonego dlań gniazda. Dlatego też, niewiele myśląc, dodałem stosowny układ RC, który miał to opóźnić – rysunek 3 zawiera fragment schematu istotny dla wyjaśnienia tego zagadnienia. Wszystkie wejścia układu cyfrowego są spolaryzowane, więc w czym problem? Odpowiedź jest oczywista: w układzie RC opóźniającym załączenie wyjść.

Specjalnie dałem rezystor (ładujący kondensator) o wysokiej rezystancji, by zapewnić jak najmniejszy pobór prądu. I to było w porządku. Ale już nie w porządku było zastosowanie takiego obwodu do sterowania wejściem, które nie jest zaopatrzone w przerzutnik Schmitta. Liczyłem się z tym, że moment zmiany stanu logicznego, czyli załączenia wyjść, nie zostanie dokładnie ustalony, ale z tym, że układ zacznie pobierać ponad 4 mA – kiedy mikrokontroler jest już dawno uśpiony – ani trochę. Ostatecznie przerobiłem ten układ tak, by linią Output Enable sterować z mikrokontrolera, co załatwiło problem. Spędziłem jednak na tym sporo czasu zarezerwowanego na wakacyjny wypoczynek.

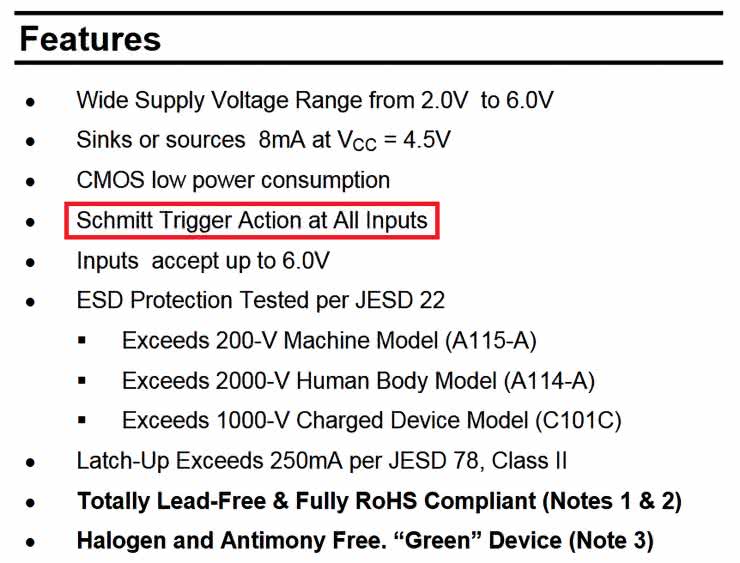

Piszę o tym, ponieważ podobny błąd jest powielany w wielu miejscach. Jednak czasem godzę się na niego, gdy: takie działanie jest jednorazowe podczas działania urządzenia, przetestowałem to już wielokrotnie, utrzymuję czas narastania nie dłuższy niż kilkadziesiąt milisekund (choć nadal dłuższy niż zaleca nota katalogowa) oraz wiem, że źródło zasilania bez problemu to wytrzyma. Trzeba być świadomym, że się coś takiego robi i jakie to może mieć konsekwencje – najpoważniejszą jest uszkodzenie podzespołu. Najlepiej byłoby stosować w takich miejscach przerzutniki Schmitta, choć nie zawsze jest na to powierzchnia na płytce; ponadto układy tego typu pobierają dodatkowe, niekiedy cenne mikroampery w stanie ustalonym. Dlatego w urządzeniach, od których nie wymaga się wysokiej niezawodności, czasem decyduję się uproszczone, choć nieidealne rozwiązanie.

Jeszcze inną kwestią jest fakt, że nawet układy z tej samej rodziny czasem mogą mieć wejścia Schmitta… albo ich nie mieć. Przykładowo SN74HC595 od Texas Instruments zawiera w swojej nocie katalogowej [2] tabelkę identyczną, jak ta z rysunku 1. Z kolei układ 74HC595 produkcji Diodes Incorporated ma dopisek informujący o tym, że wszystkie wejścia są wyposażone w przerzutniki Schmitta – rysunek 4. Który jednak uda się kupić w hurtowni – nie wiadomo, czasem nawet sami dostawcy wysyłają „analogiczne” zamienniki innego producenta, bez wcześniejszego uprzedzenia. Projektant nie ma więc gwarancji, że układ 74HC595 ma wejścia Schmitta – w przeciwieństwie do, na przykład, CD4093, dla którego jest to natywna cecha.

Wykres znajdujący się na rysunku 2 obrazuje również, dlaczego nie warto zostawiać „wiszących” wejść układów CMOS. Poza tym, że ich stan logiczny będzie wówczas nieustalony (a ładunki elektrostatyczne również „nie śpią”), to dzięki diodom zabezpieczającym potencjał tychże wejść ustali się mniej więcej w połowie napięcia zasilającego. Wynika to z prądu upływu tych diod, który jest w przybliżeniu jednakowy zarówno dla dolnej, jak i dla górnej diody, więc napięcia na nich będą praktycznie takie same. Zaś akurat w połowie napięcia zasilającego wypada maksimum poboru prądu przez układy z rodziny HC. Nieco mniejsza wartość natężenia prądu jest rejestrowana w przypadku HCT, bowiem ich górny próg przełączania wypada niżej niż w układach z serii HC, z uwagi na dostosowanie go do parametrów rodziny TTL.

Nie ma problemów z utrzymaniem żądanych czasów przełączania w przypadku sterowania wejść układów cyfrowych bezpośrednio z mikrokontrolerów czy innych układów cyfrowych. Układy z „mocarnymi” wyjściami, jak popularna ATmega8, dostarczają sygnałów o zboczach trwających pojedyncze nanosekundy, nie mówiąc o tak szybkich układach, jak chociażby FPGA. Jednak nawet tacy „słabeusze” (jak popularna seria CD) są w stanie wygenerować – przy napięciu 5 V – zbocze o czasie trwania wystarczającym do prawidłowego wysterowania układu z serii HC, na co dowód znajduje się na rysunku 5.

Przy dostatecznie krótkich połączeniach oraz małej pojemności pasożytniczej ścieżek możemy mieć pewność, że te czasy nie ulegną nadmiernemu wydłużeniu.

Michał Kurzela, EP

Źródła:

[1] https://toshiba.semicon-storage.com/info/74HC4049D_application_note_en_20210131_AKX00107.pdf?did=63521&prodName=74HC4049D

[2] https://www.ti.com/lit/ds/symlink/sn74hc595.pdf

[3] https://docs.rs-online.com/81fa/0900766b812cd41f.pdf

[4] https://www.ti.com/lit/ds/symlink/cd4017b.pdf

Zaloguj

Zaloguj