Firma Philips Semiconductors opracowała magistralę I²C ponad 40 lat temu, jako prosty interfejs do komunikacji pomiędzy różnymi układami scalonymi w obrębie jednego urządzenia. Inter-Integrated Circuit, bo tak rozwija się nazwa I²C (IIC) to szeregowa, dwuprzewodowa magistrala do dwukierunkowej transmisji danych pomiędzy układami, na ogół w obrębie jednej płytki drukowanej. Prostota i niski koszt magistrali I²C zachęciły elektroników do znalezienia większej liczby zastosowań dla tego protokołu (i jego pochodnych). Chociaż technologia ta ma prawie pół wieku, to nadal jest często stosowanym rozwiązaniem dla wielu interfejsów konserwacyjnych i kontrolnych.

Od momentu stworzenia zasadniczej specyfikacji I²C opracowano wiele dodatkowych komponentów, aby uczynić ten interfejs lepszym i jeszcze bardziej użytecznym. W szczególności, aby przezwyciężyć niektóre podstawowe ograniczenia wynikające z dodawania większej liczby urządzeń do magistrali czy jej wydłużenia poza jej pierwotne maksimum wynoszące zaledwie kilka metrów.

Topologia sieci i budowa elektryczna interfejsu I²C

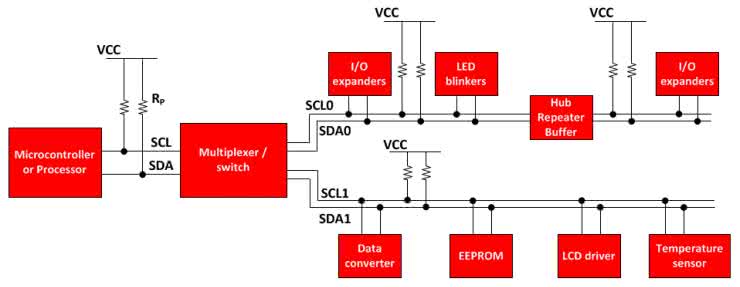

Interfejs I²C korzysta z wyjść cyfrowych z otwartym drenem/otwartym kolektorem, co oznacza, że do komunikacji można podłączyć układy scalone z różnymi wartościami napięcia zasilającego. Rezystory podciągające muszą być podłączone od linii I²C do zasilania, aby umożliwić komunikację, jak pokazano na rysunku 1.

Rezystory podciągają linię w stan wysoki, gdy nie jest ona kontrolowana (ściągana do masy) przez wyprowadzenie z otwartym drenem. Wartość rezystora podciągającego jest ważnym czynnikiem projektowym dla systemów I²C, ponieważ nieprawidłowa rezystancja może doprowadzić do utraty sygnału. W poniższym artykule zaprezentowano proste równania do obliczania rezystorów podciągających, które należy stosować do szybkiego obliczania na potrzeby dowolnego projektu.

Na rysunku 1 pokazano klasyczną magistralę I²C dla systemu wbudowanego, w którym używanych jest wiele urządzeń podrzędnych. Mikrokontroler reprezentuje nadrzędny układ (master), kontrolujący sieć I²C, który steruje i zarządza ekspanderami I/O, różnymi czujnikami, pamięcią EEPROM, przetwornikami ADC oraz DAC i wieloma innymi elementami w sieci. Wszystkie te układy są kontrolowane za pomocą tylko 2 pinów mastera. Interfejs I²C wykorzystuje linie typu otwarty dren/otwarty kolektor z buforem wejściowym na linii, co pozwala na użycie pojedynczej linii danych do dwukierunkowego przepływu danych.

Otwarty dren odnosi się do typu wyjścia, które może albo ściągnąć napięcie magistrali (w większości przypadków do masy), albo zwolnić magistralę i pozwolić, aby osiągnęła stan wymuszany przez rezystor podciągający (na ogół jest to poziom napięcia zasilania). W przypadku zwolnienia magistrali przez układ master lub slave, rezystor podciągający (RPU) na linii odpowiada za ustalenie napięcia magistrali z powrotem do napięcia linii zasilającej. Ponieważ żadne urządzenie nie może wymusić stanu wysokiego na linii, oznacza to, że magistrala nigdy nie napotka problemu z komunikacją, w którym jedno urządzenie może próbować przesłać stan wysoki, a inne niski, powodując zwarcie (szyny zasilającej do masy).

W przypadku urządzenia nadrzędnego w systemie z wieloma masterami transmitowanie stanu wysokiego służy też do sprawdzenia, czy inne urządzenie korzysta właśnie z magistrali (linia jest w stanie niskim). W szczególnym przypadku, możliwe jest nawet uzyskanie funkcji abordażu, czyli przejęcia transmisji na magistrali przez układ o wyższym priorytecie. Interfejsy typu push-pull nie pozwalają na tego typu swobodę, co jest zaletą i przyczyną tak dużej elastyczności interfejsu I²C.

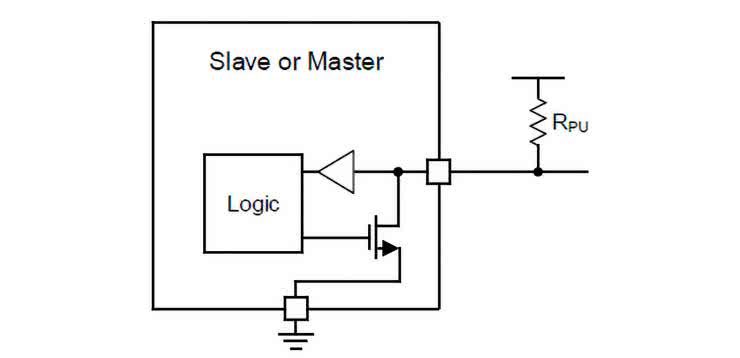

Na rysunku 2 pokazano uproszczony widok wewnętrznej struktury urządzenia - podrzędnego lub nadrzędnego - na liniach SDA/SCL. Układ obsługujący pin składa się z bufora do odczytu danych wejściowych oraz tranzystora FET do przesyłania danych. Urządzenie to jest w stanie jedynie ściągnąć linię magistrali (zewrzeć ją do masy przez tranzystor) lub zwolnić linię magistrali (wysoka impedancja do masy) i pozwolić rezystorowi podciągającemu (RPU) podnieść napięcie. Jest to ważna koncepcja, którą należy zrealizować w układzie z urządzeniami I²C, tak, aby żadne urządzenie nie utrzymywało magistrali w wymuszonym stanie wysokim. To właśnie umożliwia komunikację dwukierunkową na jednej linii za pomocą I²C.

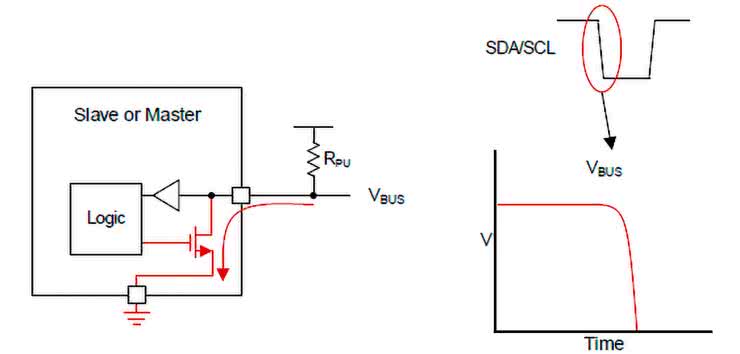

Układ w konfiguracji otwartego drenu może jedynie obniżać stan magistrali lub pozwolić rezystorowi podciągnąć ją w górę. Na rysunku 3 pokazano przepływ prądu w momencie ściągania magistrali do masy. Logika, która chce przesłać stan niski, aktywuje obniżający tranzystor FET, który zapewni zwarcie do masy, ściągając linię w dół.

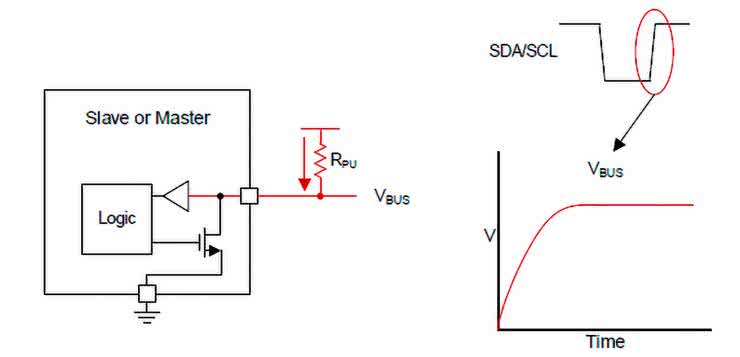

Gdy urządzenie w sieci I²C zamierza ustawić na linii stan wysoki, musi zwolnić magistralę przez wyłączenie tranzystora ściągającego ją do masy. To pozostawia magistralę w tanie nieustalonym, a rezystor podciągający (RPU) ustali napięcie takie, jak ma szyna zasilania, co zostanie zinterpretowane, jako stan wysoki. Na rysunku 4 zobrazowano przepływ prądu przez rezystor podciągający, który ustala poziom na magistrali na stan wysoki.

Analizując budowę i działanie całej magistrali, należy pamiętać, że takich układów, jak pokazane na rysunku 3 i 4 znajduje się wiele w sieci I²C (każdy master i każdy slave ma takie elementy do sterowania magistralą), a dodatkowo na układ składają się wszystkie ścieżki, łączące elementy. Natomiast opornik podciągający, typowo instaluje się jeden na całą sieć. Jego rezystancja musi być dobrana do struktury całej sieci i ilości urządzeń w niej.

Obliczanie maksymalnej i minimalnej wartości oporników podciągających

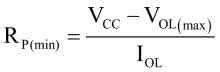

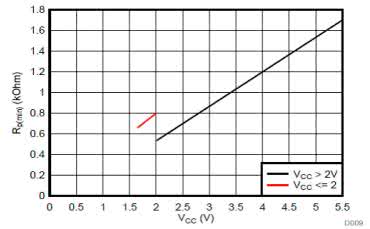

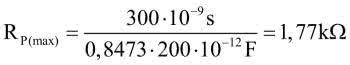

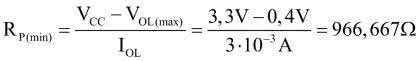

Silne podciągnięcie (przez rezystor o niskim oporze) uniemożliwia ustawienie przez układ scalony odpowiednio niskiego napięcia. Poziom VOL, który może być odczytany przez bufory wejściowe układu scalonego, jako ważny logiczny poziom niski, określa minimalną rezystancję oporników podciągających (RP(min)). Rezystancja RP(min) jest funkcją VCC, VOL(max) i IOL:

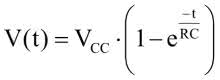

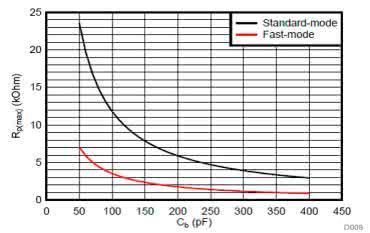

Maksymalna rezystancja podciągania jest ograniczona przez pojemność magistrali (Cb) ze względu na określony czas narastania zbocza sygnału w interfejsie I²C. Jeśli wartość rezystora podciągającego jest zbyt wysoka, linia I²C może nie móc wzrosnąć do poziomu logicznego wartości „1”, zanim zostanie ponownie obniżona do zera. Odpowiedź obwodu RC na skok napięcia o amplitudzie VCC, rozpoczynający się w chwili t = 0, charakteryzuje się stałą czasową RC. Przebieg napięcia można zapisać, jako:

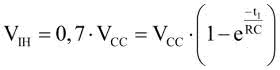

Dla VIH = 0,7 × VCC:

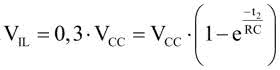

Dla VIL = 0,3 × VCC:

Czas narastania tr na linii I²C może być opisany wyrażeniem:

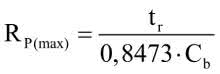

Z czego można wyznaczyć maksymalną rezystancję Rp(max) podciągającą dla zadanego układu i maksymalnego czasu narastania tr(max):

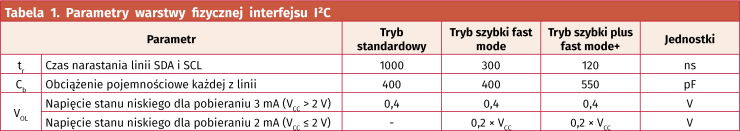

Parametry, potrzebne do powyższych obliczeń, zestawiono w tabeli 1, opracowanej na podstawie specyfikacji warstwy fizycznej interfejsu I²C.

Opór RP(min) został wyznaczony w funkcji VCC na rysunku 5 i w funkcji pojemności linii Cb na rysunku 6. Wykresy pokazują wymagania, co do opornika podciągającego w trybie standardowym i trybie szybkim.

Szybkość vs. zużycie mocy - kompromis

Po wybraniu minimalnej i maksymalnej wartości rezystora podciągającego decyzję o wyborze konkretnej wartości rezystora można podjąć na podstawie kompromisu między szybkością a budżetem mocy. Mniejszy rezystor zapewni większą prędkość narastania zbocza z powodu mniejszego opóźnienia wynikającego z wartości formujących układ RC, a z kolei rezystor o wyższym oporze zapewni mniejsze zużycie energii przez interfejs, dzięki redukcji prądu płynącego przez oporniki podciągające.

Przykładowe wyliczenia

Załóżmy układ I²C, pracujący w trybie szybkim, która pracuje w układzie o następujących parametrach:

Cb = 200 pF.

VCC = 3,3 V.

Obliczamy zakres rezystancji opornika podciągającego zgodnie z równaniami 1 oraz 6 i danymi, zawartymi w tabeli 1. W ten sposób uzyskujemy:

Oznacza to, że dobrać możemy oporniki o rezystancji zawartej pomiędzy 966,667 Ω i 1,77 kΩ. Realnie, dla oporników z szeregu E24 (5%), pozwala to wybrać spośród następujących oporników: 1,1 kΩ, 1,2 kΩ, 1,3 kΩ, 1,5 kΩ, 1,6 kΩ. Finalny wybór konkretnej wartości uzależniony jest od opisywanego powyżej kompromisu energetycznego.

Podsumowanie

Obliczanie wartości oporników podciągających linie interfejsu I²C to nic trudnego. Do wyznaczenia zakresu akceptowalnych wartości tych oporników wymagana jest zaledwie garść parametrów, z których kluczowym jest prędkość działania interfejsu oraz pojemność linii SDA i SCL (rozumiana, jako pojemność pomiędzy daną linią a masą). Pojemność ta jest uzależniona od geometrii ścieżek interfejsu na PCB i ilości podłączonych do nich urządzeń. Finalnie, istotnym czynnikiem wyboru opornika jest podejście, co do zużycia energii przez system - poświęcając prędkość interfejsu, możliwe jest zmniejszenie zużycia energii przez ten element układu.

Nikodem Czechowski, EP

Bibliografia:

- Jean-Marc Irazabal, Steve Blozis „I²C MANUAL”, Philips Semiconductors Application Note AN10216-01 (2003).

- Jonathan Valdez, Jared Becker, „Understanding the I²C Bus”, TI Application Report, SLVA704 (2015).

- Rajan Arora, „I²C Bus Pullup Resistor Calculation”, TI Application Report, SLVA689 (2015).

Zaloguj

Zaloguj