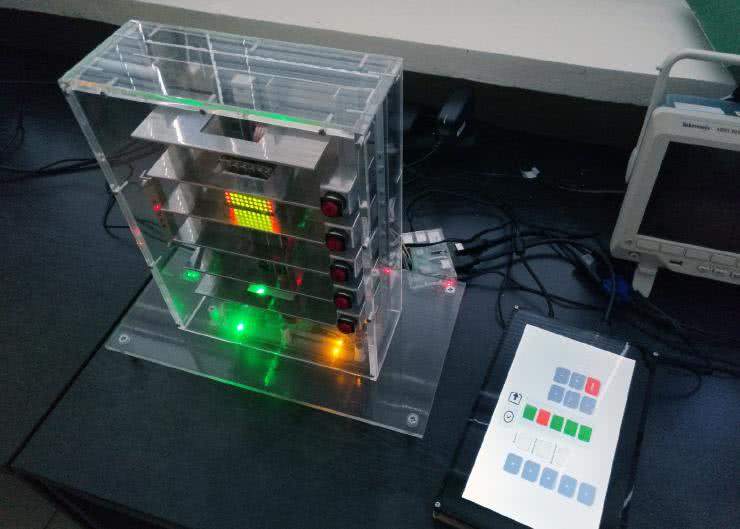

Do zbudowania sterownika programowalnego można użyć rekonfigurowalnego układu FPGA i zaimplementować w nim odpowiednią architekturę. W prezentowanym przypadku, do budowy sterownika PLC został użyty układ FPGA firmy Xilinx z rodziny Artix-7. Stanowi on główny element modułu uruchomieniowego Digilent Cmod A7-35T.

Architektura sterownika

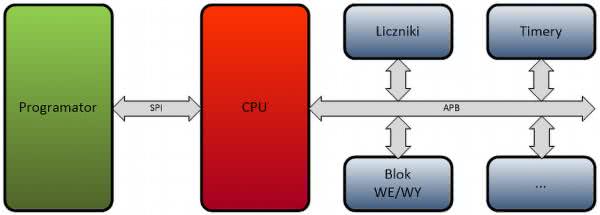

Z punktu widzenia architektury systemu, sterownik PLC może być właściwie uważany za rodzaj mikroprocesora. Podstawowy element tworzy jednostka centralna CPU. Jest ona odpowiedzialna za wykonywanie algorytmu sterowania opisanego za pomocą programu. Uzupełnieniem jednostki centralnej są dedykowane moduły, wspierające pracę całego sterownika.

Projektując mikroprocesor należy podjąć ogromną liczbę decyzji. Najważniejsze jest odpowiednie zaplanowanie architektury, która umożliwi w przyszłości rozbudowę o nowe funkcjonalności. Z punktu widzenia komunikacji z programatorem najbardziej oczywistym wyborem było zastosowanie interfejsu szeregowego SPI, powszechnie stosowanego do komunikacji z peryferiami na krótkich dystansach. Z kolei z punktu widzenia komunikacji z modułami, zdecydowanie lepszym rozwiązaniem jest zastosowanie magistrali równoległej. W tym przypadku wybór padł na magistralę APB firmy ARM. Architektura sterownika PLC jest przedstawiona na rysunku 1.

Najważniejszą zaletą architektury jest modułowość. Zastosowanie magistrali APB daje możliwość komunikacji z różnego typu modułami, np. typowymi dla sterownika PLC: licznikami, timerami, czy blokami wejścia/wyjścia, a także innymi zaprojektowanymi dla określonego zastosowania.

Jednostka centralna

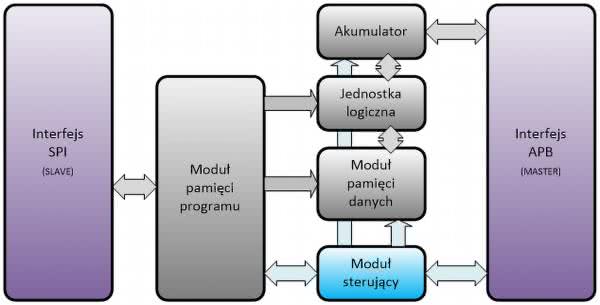

Uogólnioną strukturę jednostki centralnej zaprojektowanego sterownika pokazano na rysunku 2. Komunikację z otoczeniem przejmują wspomniane uprzednio dwa interfejsy: SPI i APB. Budowa jednostki CPU bazuje na architekturze harwardzkiej z oddzielnymi modułami pamięci programu i danych oraz rejestrem specjalnym zwanym akumulatorem. Zaprojektowana jednostka jest tzw. maszyną jednooperandową. Całością pracy jednostki centralnej CPU zarządza moduł sterujący, oparty na automacie sekwencyjnym. Odpowiada on za odpowiednie wykonywanie programu sterowania (poszczególnych instrukcji), a także za odpowiedni przepływ danych pomiędzy pozostałymi modułami. W dużym uproszczeniu, odpowiada za pobranie rozkazu z modułu pamięci programu, zdekodowanie go, wykonanie i przygotowanie licznika rozkazów w celu przygotowania jednostki do wykonania następnej operacji. Generalnie, operacje są wykonywane z daną znajdującą się w rejestrze akumulatora.

Na liście rozkazów znajdują się rozkazy pobrania i wysłania danych, szeroka gama operacji logicznych (w tym m.in. wykrywacze zboczy, instrukcje porównania) i instrukcje skoków. Instrukcje mogą być wykonane ze zmienną lub z daną natychmiastową. Możliwe jest dodatkowe zastosowanie modyfikatora negującego argument.

Wadą zaprojektowanej jednostki jest konieczność wykonywania operacji na rejestrze akumulatora (maszyna jedno-operandowa). Przetwarzanie danej musi być rozbite na wiele rozkazów. Wadę tę dość wydajnie redukuje zaprojektowana architektura, dzięki której większość operacji jest wykonywana w dwóch cyklach zegarowych. Dzięki dużej częstotliwości taktowania układu FPGA (w tym wypadku 100 MHz), uzyskana jednostka jest w zasadzie szybsza od wielu firmowych sterowników przemysłowych dostępnych na rynku.

Należy wspomnieć, że zaprojektowana jednostka jest 32-bitowa. Najciekawsze jest jednak to, że użycie pamięci wielobramowych dostępnych powszechnie w układzie FPGA umożliwia, przy zastosowaniu odpowiedniej architektury (multipleksowanie), adresowanie zarówno 1-bitowe, 8-bitowe, 16-bitowe, jak i 32-bitowe tego samego kontekstu pamięci. Należy podkreślić, że nie odbywa się to na zasadzie maskowania bitów, ale dana jest dostępna już po jednym takcie sygnału zegarowego.

Tym, co odróżnia zaprojektowany sterownik PLC od typowego rozwiązania to modułowość. Właściwie należy powiedzieć „nieograniczona modułowość”. Daje ją zastosowanie magistrali APB do komunikacji z modułami peryferyjnymi. Programista ma dwa rozkazy dotyczące APB, służące komunikacji: zapis i odczyt. Dzięki temu, programista decyduje o tym, z jakimi modułami i w jaki sposób nastąpi komunikacja, a napisany przez niego fragment programu stanowi część systemu operacyjnego sterownika. Każdy moduł ma przydzielony adres bądź grupę adresów. Programiście wystarczy znać jedynie protokół wymiany danych z danym modułem.

Programator i panel operatorski

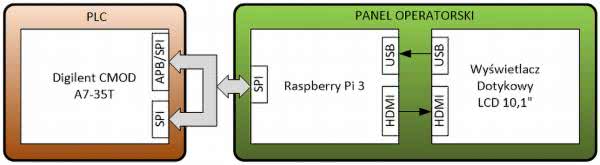

Dla użytkownika sterownika PLC nieodłącznym elementem jest programator. Został on zbudowany na bazie jednopłytkowego komputera Raspberry Pi 3 wraz z 10,1-calowym wyświetlaczem dotykowym (rysunek 3).

Zastosowanie tego zestawu nasunęło pomysł rozszerzenia funkcjonalności programatora o panel operatorski. Pojawił się jednak problem związany z komunikacją. Programator jest urządzeniem nadrzędnym w stosunku do sterownika i decyduje o programowaniu. Jednak pracując jako panel operatorski, powinien być urządzeniem podrzędnym. Konflikt ten został rozwiązany dzięki modułowości opracowanego sterownika. Jednym z modułów dołączonych do magistrali APB jest mostek APB/SPI, za pośrednictwem którego jednostka CPU komunikuje się z panelem. Po wykonaniu pętli głównej, jednostka centralna wykonuje program systemowy obsługi panelu, napisany przez programistę znającego protokół wymiany danych z panelem. Fizycznie wymiana następuje za pomocą tej samej magistrali SPI mikrokomputera Raspberry PI.

Digilent Design Contest

Autorzy projektu są studentami kierunku Elektronika i Telekomunikacja w Politechnice Śląskiej i aktywnymi członkami Studenckiego Koła Naukowego Elektroników. Są również stażystami w firmach Cadence i Digital Core Design. W 2018 roku autorzy brali udział w konkursie ściśle związanym z projektowaniem dedykowanych układów cyfrowych Digilent Design Contest w Rumunii, zajmując III miejsce.

Przemysław Mazur

Robert Nawrath

Marcin Beberok

Zaloguj

Zaloguj