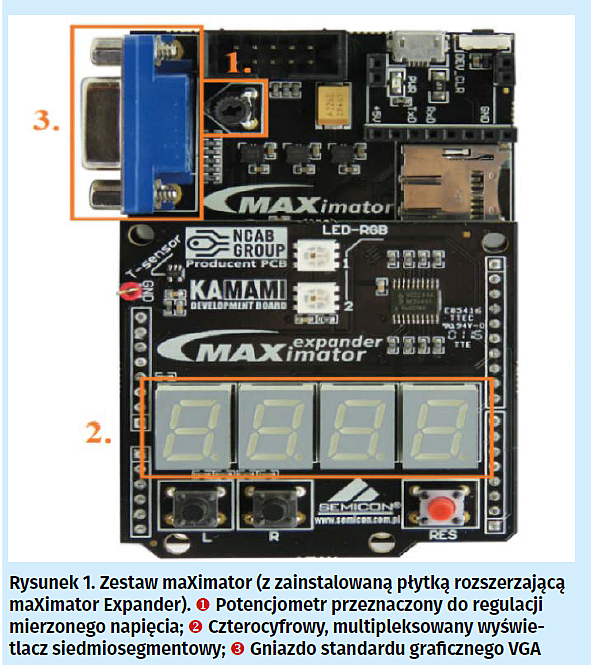

Opracowany woltomierz opiera się w swoim działaniu na dwunastobitowym przetworniku analogowo-cyfrowym (ADC), o częstotliwości taktowania równej 10 MHz oraz częstotliwości próbkowania równej 1 MHz (inaczej mówiąc: zwraca on milion próbek w ciągu jednej sekundy, funkcjonując z przepływnością 1 Msps (Megasamples per second)). Przetwornik ten wbudowany jest w układ FPGA obecny w zestawie maXimator (jest to układ z rodziny MAX10 firmy Intel (dawniej Altera), o oznaczeniu kodowym: 10M08DAF256C8GES) i przeznaczony jest do pracy z sygnałami o amplitudach z zakresu od 0 do 2,5 V (powyżej tego zakresu zwraca on, dzięki zastosowanej ochronie nadnapięciowej wyniki odpowiadające granicznemu, maksymalnemu napięciu tj. 2,5 V).

- czteropozycyjny, multipleksowany wyświetlacz siedmiosegmentowy (zawarty na płytce rozszerzającej zestaw maXimator tj. maXimator Expander),

- gniazdo standardu graficznego VGA (zawarte w samym zestawie), umożliwiające dołączenie dowolnego urządzenia wyświetlającego z nim zgodnego.

Zatem jest to także urządzenie bazujące na niewielkiej liczbie peryferiów, nieskomplikowane pod względem budowy fizycznej (biorąc szczególnie pod uwagę brak konieczności uprzedniego opracowania i zastosowania własnych torów wejściowych dla obecnego w zestawie źródła). Do stworzenia oraz implementacji woltomierza użyto darmowego środowiska projektowego o nazwie Quartus II, w wersji 16.1 Lite (do pobrania ze strony https://goo.gl/qP593Y), która wbrew pozorom nie jest jedynie w stosunku do niego obowiązującą (może on bowiem zostać również uruchomiony na pozostałych wersjach wspomnianego środowiska, tj. Standard i Prime, zarówno o niższych (starszych) jak i wyższych (nowszych) numerach, pod warunkiem jednak, że obsługują one wspomniany wcześniej układ FPGA).

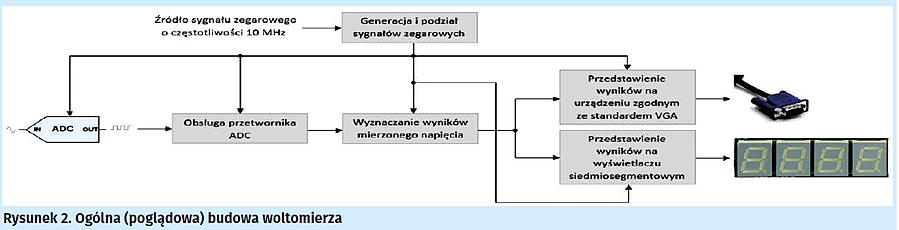

Na rysunku 2 przedstawiono ogólną (poglądową) budowę omawianego woltomierza. Na jego podstawie można wyróżnić łącznie pięć grup modułów go budujących. Są to:

- moduły generowania i podziału sygnałów zegarowych, stosowanych w obrębie woltomierza (I),

- moduły obsługi przetwornika ADC (II),

- moduły wyznaczania wyników mierzonego napięcia (III),

- moduły przedstawiania wyników w oparciu o standard graficzny VGA (IV),

- moduły przedstawiania wyników na wyświetlaczu siedmiosegmentowym (V).

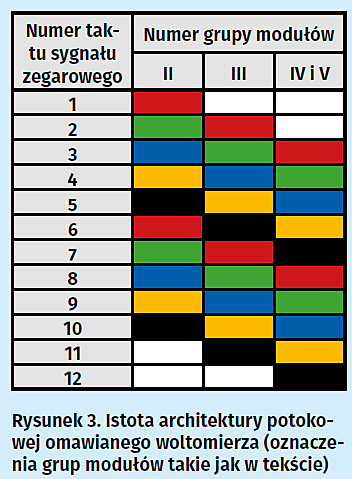

Podstawową ich cechą jest w pełni synchroniczna praca, tj. taka, która opiera się o zbocza sygnałów zegarowych do nich doprowadzonych (innymi słowy: funkcjonalność modułów realizowana jest wraz z każdym kolejnym taktem wspomnianych sygnałów, przy czym momentem ją wyzwalającym są zbocza tych taktów, domyślnie narastające (przejścia od ich stanów niskich do wysokich). Tym samym również i woltomierz jest w pełni synchroniczny, co przekłada się bezpośrednio na jego architekturę, która jest potokowa (ang. pipeline). Jej istotą jest fakt, że moduły będące w stosunku do siebie następującymi po sobie stopniami pojedynczego potoku (którym jest woltomierz) wykonują w tym samym czasie własne zadania, bazując na danych pochodzących z modułów wcześniej występujących. Czynią to w sposób przedstawiony na rysunku 3.

Moduły generowania i podziału sygnału zegarowego

W skład tej grupy wchodzą:

- pojedyncza pętla PLL,

- moduł Generator_opoznien_impulsow.

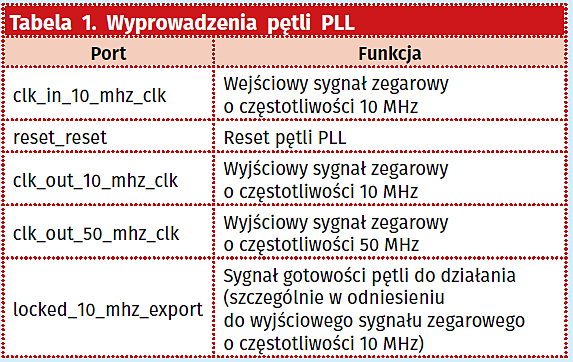

Pierwszy z przedstawionych elementów odpowiedzialny jest za generację sygnałów zegarowych, które w zależności od potrzeb albo są dostarczane bezpośrednio do dalszych modułów woltomierza, albo pośrednio, po uprzednim podzieleniu z zastosowaniem drugiego z nich. Sygnały te przedstawiono w tabeli 1.

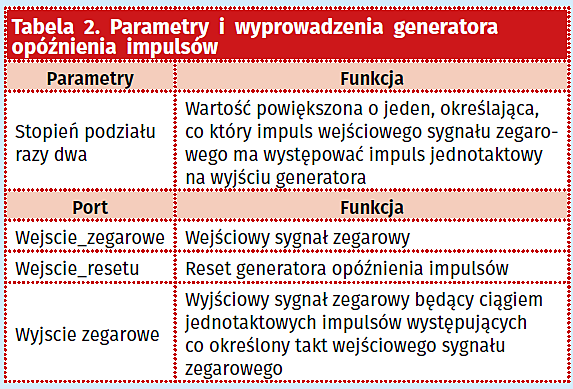

Drugi element to nic innego jak generator impulsów o stałej szerokości, równej pojedynczemu taktowi wejściowego sygnału zegarowego. Impulsy te tworzone są co określony takt tegoż sygnału. Tym samym również co określony takt generowane są ich zbocza narastające, co z kolei przekłada się na obecne w nazwie modułu opóźnienie (im szybciej się one pojawiają, tym więcej czynności w określonej jednostce czasu jest w stanie wykonać dany moduł, im rzadziej natomiast, tym mniej). Jest to podejście równoważne dzielnikowi częstotliwości (preskalerowi), przy czym różnicą w stosunku do niego jest brak zapewnienia wypełnienia taktów wyjściowego sygnału zegarowego na poziomie 50% (nie jest to jednak tu istotne – w stosunku do opóźnienia bowiem liczą się jedynie wspomniane zbocza, a nie poziomy i czas trwania taktów sygnału zegarowego. Tym samym możliwe staje się zaniedbanie tego parametru i zastosowanie w sposób wystarczający jednotaktowych impulsów). Bez względu jednak na to, w stosunku do pętli PLL generator opóźnień impulsów jest modułem parametryzowanym tzn. takim, w którym w zależności od potrzeb można ustalić wartości wybranych jego wielkości (zwanych parametrami). Wielkości te (wraz z sygnałami omawianego modułu) przedstawiono w tabeli 2.

Domeny zegarowe woltomierza, czyli wnioski

wynikające z modułów generowania i podziału sygnału zegarowego

Dotychczas przedstawiony opis pozwala na zauważenie ważnego aspektu woltomierza. Mianowicie, składają się na niego dwie odrębne grupy modułów, pracujących na sygnałach zegarowych o dwóch różnych częstotliwościach (dla przypomnienia: chodzi o częstotliwość równą 10 i 50 MHz). Grupy, o których mowa to domeny zegarowe (ang. clock domains). W ogólności dąży się do uzyskania jednej z nich w obrębie całego urządzenia. Takie, a nie inne podejście wynika z faktu, że przy sygnałach zegarowych o różnych częstotliwościach zawsze zachodzi sytuacja, w której zbocza narastające jednego sygnału będą nieznacznie wyprzedzały zbocza narastające drugiego sygnału, przyczyniając się w ten sposób do pojawienia się niepożądanych, metastabilnych stanów przerzutników (są to stany, w trakcie których przerzutniki zachowują się nieprzewidywalnie, co przekłada się na całkowicie losowe dane na ich wyjściach w określonych momentach czasowych. Prowadzi to w efekcie do ich przekłamania w trakcie wymiany pomiędzy wspomnianymi grupami, o czym szerzej można poczytać na stronie pod adresem https://goo.gl/8bZgZY).W przypadku woltomierza problem ten jednak nie zachodzi – sygnały zegarowe bowiem są między sobą zsynchronizowane (są one tworzone na bazie wspólnego sygnału, którego jakiekolwiek zmiany automatycznie przekładają równomiernie na zmiany w obydwu sygnałach). Możliwe staje się w ten sposób zmniejszenie użycia zasobów logicznych układu FPGA (nie trzeba bowiem uwzględniać mechanizmów chroniących wymieniane dane przed przekłamaniami – jest to zarazem drugi możliwy do zauważenia aspekt opisywanego woltomierza).

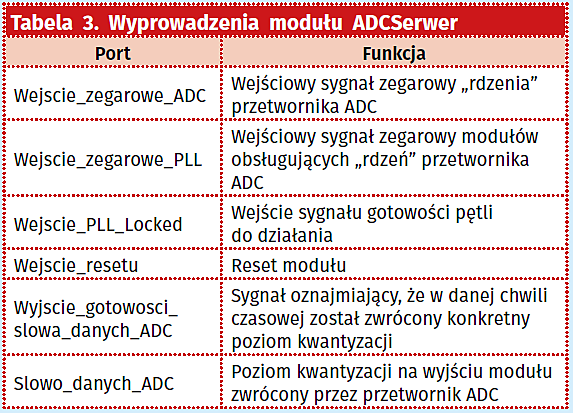

Moduły związane z obsługą ADC

W przypadku tej grupy obecne są dwa poniższe moduły:

- ADCSerwer,

- RejestrRownolegloRownolegly.

Jak można zauważyć są tu jak najbardziej obecne sygnały wymienione przy okazji omawiania pętli PLL, a także oprócz nich sygnały związane ze zwracanymi przez moduł poziomami kwantyzacji, oznajmiające ich zwrot i resetujące sam moduł (w przypadku ostatniego z nich występuje na stałe poziom wysoki, zapewniający ciągłą pracę przedstawionego modułu).

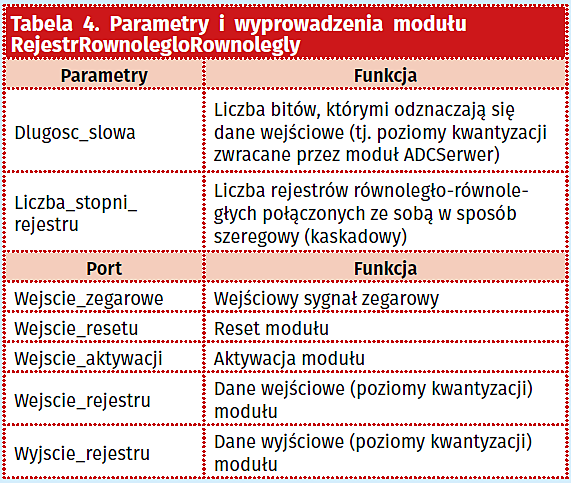

Drugi z modułów natomiast odpowiedzialny jest za zwracanie jedynie wybranych poziomów kwantyzacji. Nie chodzi jednak o świadome ingerowanie w zwracane wyniki, a pomijanie zbyt dużej ich ilości (zgodnie z wcześniejszym opisem przetwornik zwraca aż milion poziomów w ciągu sekundy, co sprawia, że zmieniają się one nadzwyczaj szybko i nie jest możliwe sensowne ich odczytanie). Tym samym realizuje on proces zwany decymacją, w oparciu o prosty rejestr równoległo-równoległy (PIPO), pod wpływem jednotaktowych impulsów wytwarzanych przez pierwszy z trzech wspomnianych wcześniej generatorów opóźnień impulsów. W tabeli 4 przedstawiono parametry i sygnały omawianego modułu.

Moduły wyznaczania

wyników mierzonego napięcia

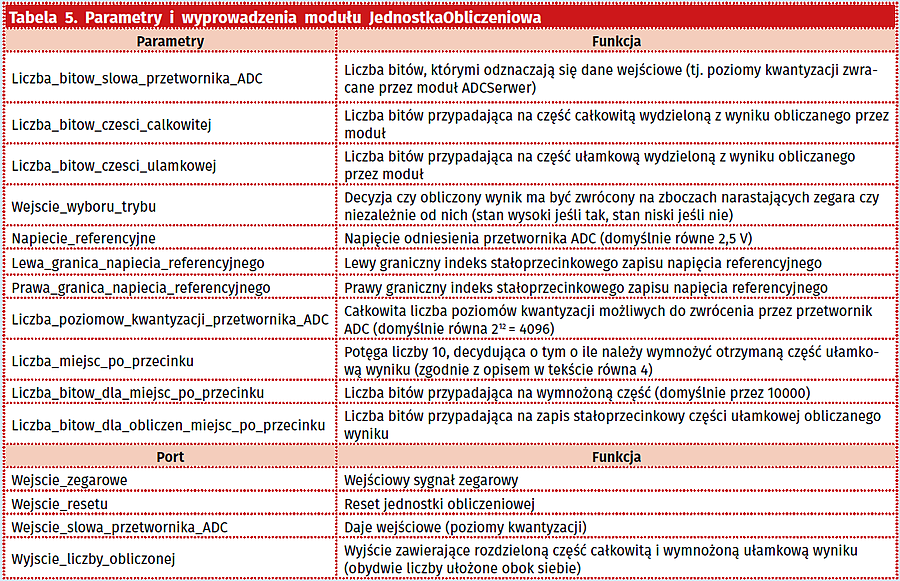

Również i tu występują dwa moduły – są to jednak tym razem:

- JednostkaObliczeniowa,

- KonwerterBinToBcd.

Najważniejszym z nich jest pierwszy, który zamienia zwracane przez moduł ADCSerwer poziomy kwantyzacji na konkretne wartości mierzonego napięcia, wyrażone w woltach. Zamiana ta odbywa się zgodnie ze wzorem 1, o postaci:

Wartość napięcia = (Wartość z przetwornika ADC/4096)·2,5 V (1)

gdzie: Wartość z przetwornika ADC przyjmuje wartości z przedziału całkowitych wartości liczbowych od 0 do 4095 (czyli wszystkie możliwe poziomy kwantyzacji przetwornika ADC).

Wzór ten (pochodzący z oficjalnej dokumentacji przetwornika, dostępnej na stronie pod adresem: https://goo.gl/uMHK8B, strony 9 i 10) wyznaczany jest w oparciu o logikę stałoprzecinkową, przy czym na część całkowitą przeznaczone są 2 bity (ze względu na fakt, że maksymalne mierzone napięcie wynosi 2,5 V, a tym samym maksymalną liczbą jego części całkowitej jest liczba 2, wymagająca do opisu jedynie dwóch bitów – 2 bowiem w zapisie binarnym to „10”), natomiast na część po przecinku łącznie 66 bitów (jest to ilość pozwalająca w sposób praktycznie jednoznaczny (z pomijalnie małym błędem) na zapisanie części ułamkowej dowolnej liczby, z dokładnością równą 1·10-4). Tym samym użytych jest łącznie 68 bitów, co wbrew pozorom nie jest znacząco dużą liczbą (jest to zarazem uzasadnienie zastosowania logiki stałoprzecinkowej zamiast zmiennoprzecinkowej, która z natury wymaga do zapisu mniejszej ilości bitów). Niezależnie jednak od tego wyznaczany w ten sposób wynik rozdzielany jest na dwie odrębne liczby – jedną obejmującą część całkowitą wyniku oraz drugą obejmującą jej część ułamkową. O ile w pierwszym przypadku wystarczające jest odrzucenie części ułamkowej wyniku, o tyle w drugim poza odrzuceniem jego części całkowitej konieczne jest jeszcze przemnożenie jego części całkowitej przez 10000, dzięki czemu możliwe jest jej potraktowanie jako łatwiejszej w operowaniu liczby całkowitej (jak można zauważyć będzie to zawsze liczba rzędu 103, co da w ostateczności wynik pomiaru określony z dokładnością do 1·10-4 V). W tabeli 5 przedstawiono parametry oraz sygnały modułu.

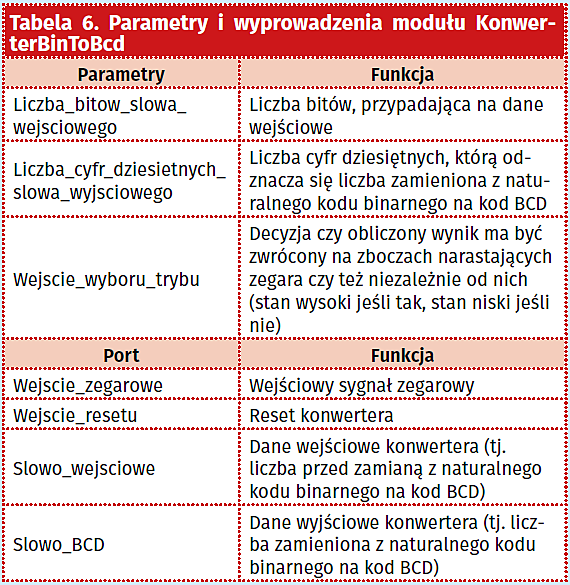

Niezależnie od tego zarówno rozdzielona część całkowita wyniku, jak i jego rozdzielona część ułamkowa wyrażone są w naturalnym kodzie binarnym, co nie jest wygodnym sposobem ich dalszej prezentacji. W związku z tym wymagają one zamiany na wygodniejszą postać, przy czym najlepszym tu rozwiązaniem jest ich zamiana na kod BCD wyrażający każdą dowolną liczbę dziesiętną w postaci ciągu cyfr dziesiętnych, które je budują, a które to zapisane są odrębnie w postaci binarnej. Zadanie to realizuje drugi z przytoczonych modułów, realizując prosty algorytm przesuwania liczby wyrażonej w naturalnym kodzie binarnym i dodawania trójki do każdej tetrady bitów liczby konwertowanej, gdy jest ona równa co najmniej 5 (wyjaśnienie algorytmu można znaleźć na stronie pod adresem https://goo.gl/fFMWe9). Parametry oraz sygnały przedstawionego modułu zawiera tabela 6.

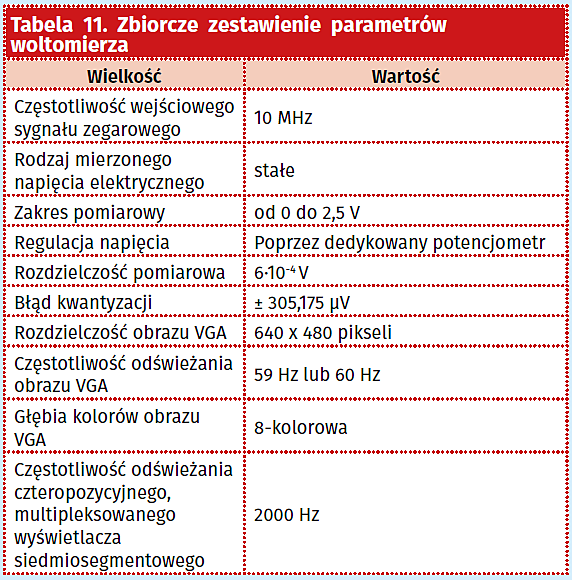

Rozdzielczość i niepewność woltomierza – wnioski płynące z modułów wyznaczania wyników mierzonego napięcia

Spoglądając jeszcze raz na wzór (1) można zauważyć, że podstawiając kolejne wartości poziomów kwantyzacji obliczone napięcie będzie rosło z krokiem równym 610,35 mV (źródło https://goo.gl/Q7V1zX, strona 9). Jeśli weźmiemy pod uwagę przyjętą we wcześniejszych rozważaniach dokładność pomiaru równą 1·10-4 V możemy zaokrąglić ten krok, uzyskując w efekcie wartość równą 6·10-4 V, która jest zarazem ostateczną rozdzielczością pomiarową opracowanego woltomierza. Należy jednak mieć przy tym na względzie to, że wynik pomiaru nią określony obarczony jest niepewnością, którą dla uproszczenia można przedstawić zgodnie ze wzorem 2.

Błąd kwantyzacji woltomierza = ±0,5 · pojedynczy krok napięcia przed zaokrągleniem = ±0,5· 610,35 mV = 305,175 mV (2)

W praktyce niepewność ta zależy od znacznie większej ilości czynników (np. od zniekształceń charakterystyki przetwornika czy zjawisk zachodzących w dołączonym do niego torze wejściowym). Jednak z racji braku stosownych w tym względzie danych czynniki te zostały pominięte, a tym samym nie zostały w jej ramach uwzględnione.

Moduły odpowiedzialne za przedstawienie wyników w oparciu o standard graficzny VGA

W przeciwieństwie do dotychczas przedstawionych grup obecne są tu trzy moduły. Są to:

- WyswietlaczVGA,

- ROM,

- SterownikVGA.

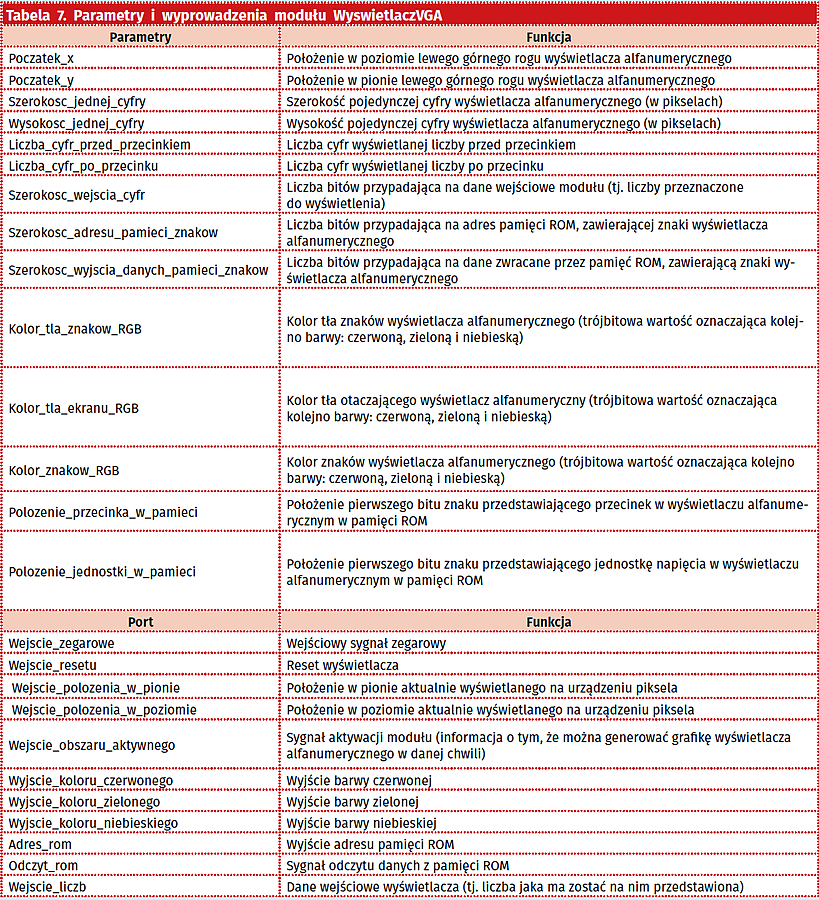

Pierwszy odpowiedzialny jest za generację dwuwymiarowej (2D) grafiki, związanej z przedstawianiem wyników pomiarów mierzonego napięcia. Grafika to nic innego jak biały, pięciopozycyjny wyświetlacz alfanumeryczny o czarnych znakach, zawarty na ciemnoniebieskim tle. Wyświetlacz ten przedstawiono na rysunku 4.

Jak można zauważyć wyniki przedstawiane są z dokładnością do czterech miejsc po przecinku, zgodnie z przytoczoną wcześniej dokładnością pomiarową. Co więcej poza samymi cyframi obecny jest znak przecinka rozdzielający część całkowitą wyniku od jego części ułamkowej oraz znak jednostki napięcia tj. „V” (również zgodnie z wcześniejszymi ustaleniami).

W oparciu o nią można stwierdzić, że odznacza się on dużą funkcjonalnością, który w zależności od potrzeb można dowolnie modyfikować (można np.: określić dokładne jego położenie na ekranie, można określić wielkość znaków jaka ma być wyświetlana, czy też można ustawiać dowolne kolory zarówno samych znaków, jak i wyświetlacza oraz tła go otaczającego). Co więcej, jest on dołączony do drugiego z wymienionych wcześniej modułów, tj. do pamięci ROM, która przechowuje wszystkie jego znaki. Pamięć ta (przeznaczona domyślnie wyłącznie do odczytu), opiera się w swej pracy na adresach jednoznacznie identyfikujących każdy jej bit (mamy tu zatem do czynienia z adresacją po bitach, zwaną inaczej: adresacją bitową). Na tej podstawie zwraca ona na każdym kolejnym zboczu narastającym doprowadzonego do niej sygnału zegarowego dane, będące pojedynczymi pikselami wspomnianych wcześniej znaków. Innymi słowy odznacza się ona sygnałami takimi jak w tabeli 8.

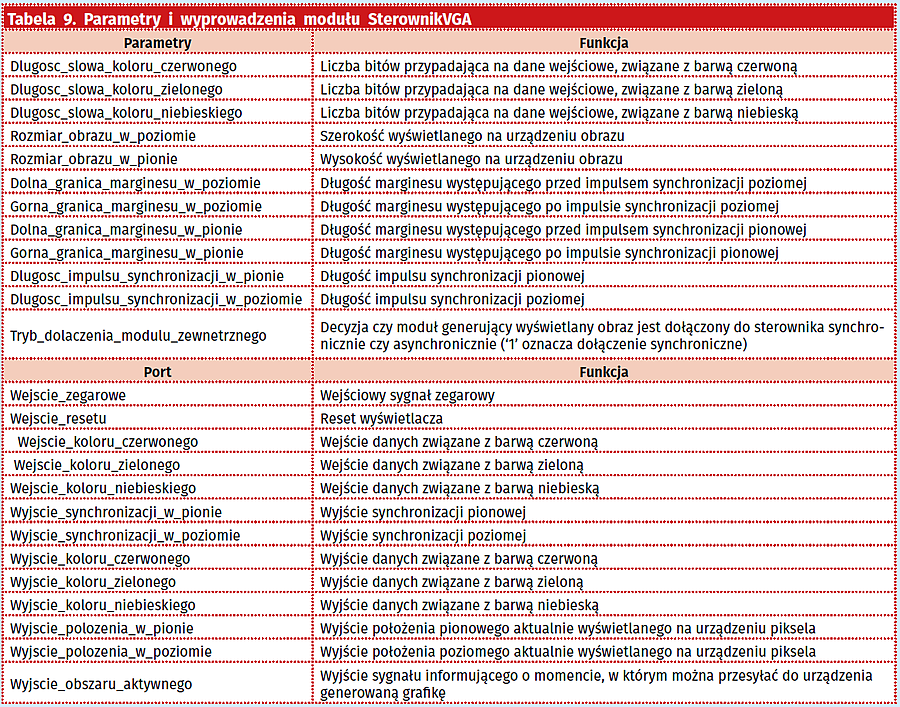

Pozostaje jeszcze do omówienia wstępnie już napomknięty moduł SterownikVGA, który jak się dało zauważyć odpowiada za przesyłanie danych graficznych do urządzenia wyświetlającego otrzymywanych z modułu WyswietlaczVGA (jest to tym samym zgodnie z nazwą pełnoprawny sterownik graficzny). Co więcej jest on związany ze wspomnianym już wcześniej standardem graficznym VGA, w przypadku którego odznacza się poniższymi parametrami:

- rozdzielczość przesyłanego obrazu: 640×480 pikseli,

- częstotliwość jego odświeżania: 59 lub 60 Hz,

- głębia kolorów: 8-bitowa (po jednym bicie na barwę czerwoną, zieloną i niebieską).

W celu ich spełnienia (zwłaszcza dwóch pierwszych) omawiany moduł funkcjonuje w oparciu o sygnał zegarowy o częstotliwości równej 25 MHz, która to pozyskiwana jest z sygnału zegarowego o częstotliwości równej 50 MHz, z zastosowaniem drugiego z przedstawionych wcześniej generatorów opóźnień impulsów (jak można zauważyć generacja jednotaktowych impulsów co drugi impuls wejściowego sygnału zegarowe jest tożsame z zastosowaniem dzielnika częstotliwości (preskalera) przez dwa – stąd też wynika pierwotnie użyta nazwa parametru związanego ze stopniem podziału)). Co więcej pierwsze dwa parametry zostały dobrane arbitralnie (według uznania autora), przy czym w przypadku drugiego z nich nie chodzi o możliwość wyboru wymienionych przy nim wartości przez użytkownika – zamiast tego chodzi o wspomniany już sygnał zegarowy o częstotliwości równej 25 MHz, która w rzeczywistości jest zaokrąglona i nie jest w pełni zgodna z oficjalnymi wartościami przewidzianymi dla rozdzielczości 640×480 pikseli (w praktyce bowiem potrzebny jest sygnał zegarowy o częstotliwości 25,175 MHz, który nie jest łatwy w uzyskaniu, nawet za pomocą pętli PLL). Tym samym niektóre urządzenia wyświetlające mogą pod jej wpływem różnie po prostu zinterpretować częstotliwość odświeżania obrazu (nie ma to jednak większego znaczenia, szczególnie, że po pierwsze ludzkie oko nie dostrzeże różnicy, a po drugie natomiast większość współczesnych urządzeń radzi sobie bez problemu zarówno z jedną, jak i z drugą częstotliwością odświeżania obrazu)). Ostatni z parametrów natomiast ma związek z tym, że w zestawie maXimator obecny jest trzybitowy przetwornik, dołączony do gniazda standardu VGA (sprawia to, że każdą z barw przestrzeni RGB przypada wyłącznie jeden bit, co w sumie daje 23 = 8 możliwych do otrzymania kolorów). W tabeli 9 przedstawiono parametry i sygnały związane ze sterownikiem.

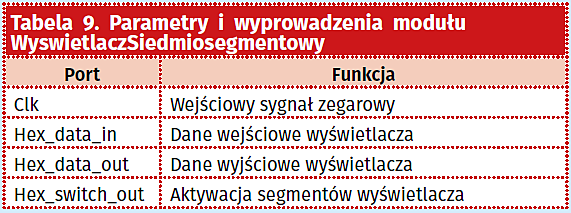

Moduły odpowiedzialne za przedstawienie wyników na wyświetlaczu 7-segmentowym

W przypadku ostatniej z grup woltomierza mamy do czynienia wyłącznie z jednym modułem, którym jest WyswietlaczSiedmiosegmentowy. Moduł ten jest zbiorem trzech następujących elementów:

- rejestr przesuwny z wartością początkową binarną równą „1000”,

- dekoder przekazujący w danej chwili dane bity danych wejściowych wyświetlacza,

- dekoder zamieniający wartość bitów danych wejściowych wyświetlacza na kod wyświetlacza 7-segmentowego.

Oprócz tego zawiera on trzeci i ostatni generator opóźnień impulsów, poprzez który następuje jego odświeżanie (zgodnie z wcześniejszym opisem do woltomierza dołączony jest wyświetlacz multipleksowany, czyli taki, w którym dochodzi do cyklicznego przełączania wszystkich jego segmentów z poziomu dołączonych do niego katod. Tym samym wspomniane odświeżanie sprowadza się do szybkości przełączania segmentów wyświetlacza na tychże katodach). Zasada jego działania jest następująca: rejestr przesuwny „przerzuca” na każdym narastającym zboczu sygnału zegarowego zawartą w jego wartości początkowej binarnej „jedynkę”, która decyduje o tym, który segment ma zostać w danej chwili uaktywniony (tym samym ich identyfikacja odbywa się na podstawie położenia „jedynki” w wartości początkowej). Następnie określane jest to, które bity danych wejściowych powinny być w danej chwili pobrane (czynione jest to w oparciu o drugi z wymienionych elementów wyświetlacza, na podstawie aktualnego położenia przesuwanej w rejestrze „jedynki” – dla przykładu: jeśli w rejestrze jest obecna wartość równa „1000” to odczytane zostają pierwsze cztery bity danych wejściowych, jeśli „0100” to następne cztery bity itd.). Ostatecznie dane które są w danej chwili pobierane zamieniane są na określony kod wyświetlacza siedmiosegmentowego, po uprzednim ich podaniu na anody wyświetlacza. W efekcie na danym segmencie pojawia się oczekiwana cyfra (i tak w przypadku pozostałych segmentów). W tabeli 9 przedstawiono parametry i sygnały przedstawionego modułu.

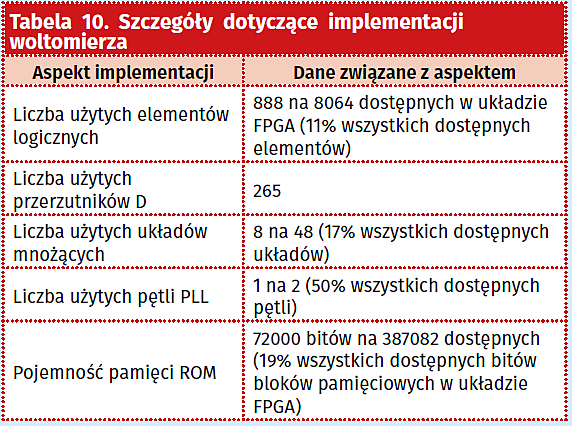

Szczegóły dotyczące implementacji woltomierza zawarto w tabeli 10, natomiast w tabeli 11 umieszczono zbiorcze zestawienie parametrów woltomierza.

Jakub Tyburski, WAT

Zaloguj

Zaloguj