Tematyka kompatybilności elektromagnetycznej pojawiała się łamach „Elektroniki Praktycznej” już wielokrotnie. Nic dziwnego – wszak zachowanie zgodności z wymogami normalizacyjnymi nie tylko otwiera drogę do komercjalizacji wyrobu, ale także istotnie wpływa na jego użyteczność i niezawodność.

Na temat EMC powstały dziesiątki (a nawet setki) książek, nieprzebrana ilość artykułów, wpisów blogowych i kursów. Oczywiste jest, że w ramach jednego artykułu dałoby się szeroko zaprezentować zaledwie jedno, może dwa szczegółowe zagadnienia z tego zakresu. Dlatego – podchodząc do sprawy realistycznie, ale i praktycznie – postanowiliśmy tym razem zaproponować naszym Czytelnikom nieco inną formę materiału: zamiast klasycznego artykułu, przygotowaliśmy przystępną checklistę EMC, czyli zestaw 14 wybranych zasad, które warto spełnić, by zwiększyć szanse na powodzenie badań projektowanego urządzenia elektronicznego w laboratorium kompatybilności elektromagnetycznej.

1. Normy nie gryzą

Dobrym punktem wyjścia do zapewnienia zgodności z normami jest… uwzględnienie ich już na samym początku projektu. Choć wskazówka ta może brzmieć jak banał, w praktyce nader często spotkać się można z zupełnie odwrotnym podejściem: wielu konstruktorów najpierw projektuje urządzenie tak, by w spełniało założenia funkcjonalne, a dopiero przed etapem komercjalizacji zaczyna się zastanawiać nad tym, które normy owego sprzętu dotyczą. Co gorsza, w niektórych firmach podobne podejście praktykuje się nawet podczas opracowywania urządzeń medycznych. I choć skupienie się wyłącznie na funkcjonalności jest istotnie ogromnie ważne na etapie prototypu czy też MVP, to jednak proces projektowania wersji komercyjnej zdecydowanie powinien uwzględniać zagadnienia normalizacyjne (zarówno w zakresie odporności, jak i emisji – patrz rysunek 1) już na samym początku. Co ważne, opisana zasada dotyczy nie tylko samej kompatybilności elektromagnetycznej, ale także norm z zakresu bezpieczeństwa elektrycznego, użyteczności bądź aspektów natury mechanicznej lub materiałowej – każda branża rządzi się swoimi prawami, dlatego warto przynajmniej pobieżnie zorientować się, z czym będziemy mieli do czynienia po przekroczeniu drzwi laboratorium.

2. Wybieramy klocki

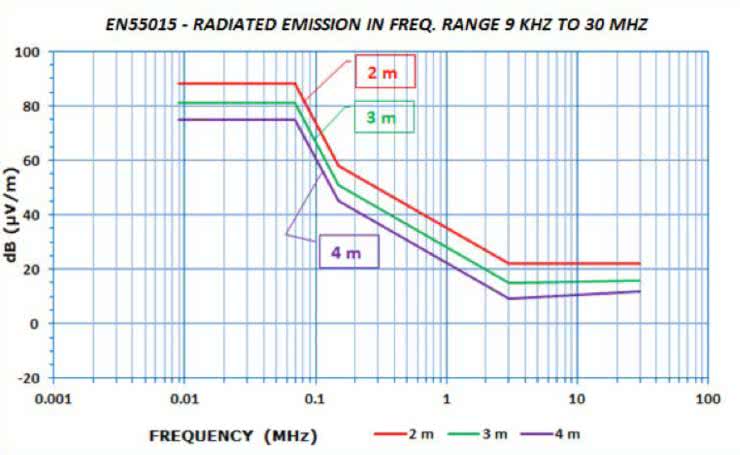

Na wczesnym etapie projektu nie sposób rzecz jasna przewidzieć, jaka będzie rzeczywista emisja zakłóceń oraz w jakim stopniu sprzęt będzie podatny na zaburzenia odbierane z zewnątrz. Konkretne wartości liczbowe „ujawniają” się zwykle dopiero na etapie badań precompliance, ale znajomość: pasm częstotliwości podlegających ocenie, wartości narażeń testowych generowanych przez symulator ESD, czy też napięć stosowanych w testach udarowych pozwala od razu dobrać komponenty, które dadzą najwyższe prawdopodobieństwo sukcesu w pomiarach laboratoryjnych. Właściwa selekcja elementów ochrony przeciwprzepięciowej (np. transili), niskoszumnego konwertera DC/DC, a nawet odpowiednich komponentów biernych potrafi zdziałać cuda. Dobrym przykładem będzie kwestia dławika współpracującego z przetwornicą impulsową – modele ekranowane są wprawdzie droższe od ich nieekranowanych odpowiedników o zbliżonych parametrach (indukcyjności, prądzie nasycenia, rezystancji DC itp.), ale zastosowanie ekranu magnetycznego pozwala znacznie ograniczyć emisję zaburzeń promieniowanych (rysunek 2). Mało tego – może się okazać, że oszczędności pozyskane dzięki zastosowaniu „gorszego” dławika okazałyby się niewspółmiernie małe, w porównaniu do kosztów procesu przeprojektowywania PCB oraz liczby iteracyjnie wykonywanych badań inżynierskich. Zasada „right the first time” w odniesieniu do EMC jest naprawdę warta rozważenia – a widać to jak na dłoni po zapoznaniu się z przykładowym cennikiem usług dowolnego laboratorium...

3. Dziel i rządź

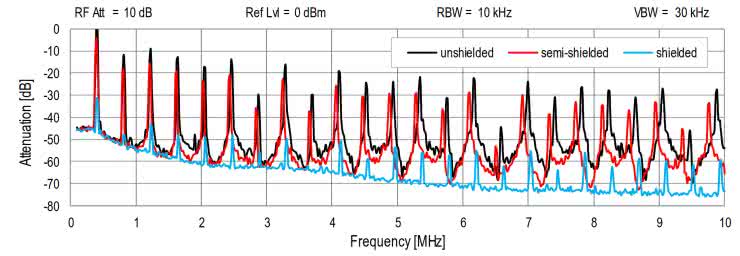

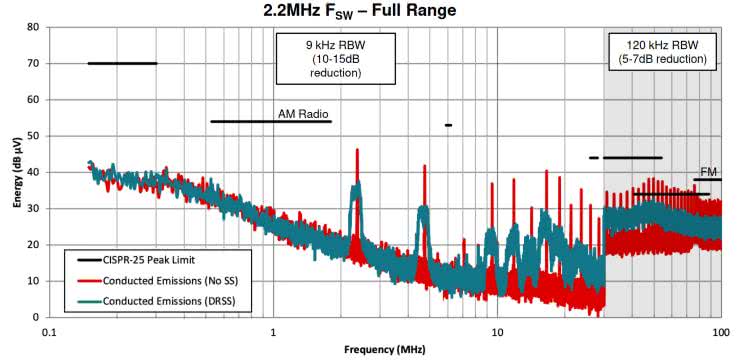

Skoro jesteśmy już przy tematyce konwerterów DC/DC, to warto podać ciekawy przykład, związany z doborem właściwego rodzaju kontrolera pozwalającego na obniżenie poziomu zakłóceń emitowanych przez układ zasilania. Klasyczne przetwornice impulsowe pracują zwykle na jednej, ustalonej fabrycznie (lub regulowanej przez użytkownika) częstotliwości. Takie rozwiązanie jest relatywnie proste konstrukcyjnie, ale ma dość istotną wadę: całość energii emitowanej w postaci zaburzeń RFI skupia się w wąskich pikach widma, odpowiadających częstotliwości podstawowej oraz szeregowi jej kolejnych harmonicznych. Zastosowanie techniki widma rozproszonego (ang. spread spectrum), polegającej na losowym lub okresowym odstrajaniu częstotliwości kluczowania w niewielkim zakresie, powoduje „rozlanie” pików do postaci szerszych pasm o niższej wartości szczytowej (rysunek 3). W ten sposób konstruktor może „uciec” nawet o kilkanaście decybeli od limitów emisji określonych normą, co w wielu sytuacjach okaże się zbawienne dla wyniku badań laboratoryjnych.

4. Łowienie na przynętę

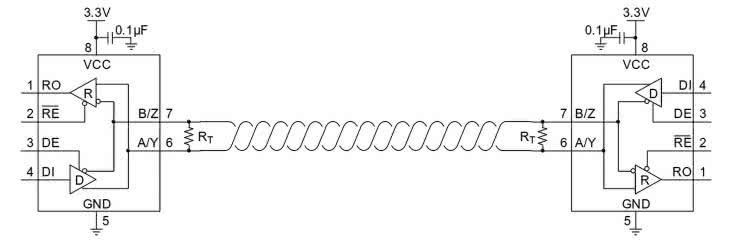

Jak powszechnie wiadomo, reklama jest dźwignią handlu. Niestety, opisy rozmaitych produktów nagminnie tuszują ich niedoskonałości, wydobywając zarazem „na wierzch” tylko zalety. Technika ta jest maksymalnie eksploatowana np. przez deweloperów, którzy kuszą klientów mieszkaniami w dobrze skomunikowanym i zielonym otoczeniu, zapominając przy tym wspomnieć o planowanej tuż obok linii tramwajowej lub obwodnicy. Producenci komponentów elektronicznych nie pozwalają sobie wprawdzie na aż tak wyraźne nadużycia zaufania odbiorców, jednak także nie pozostają „kryształowo czyści” – dobrym przykładem mogą tutaj być noty katalogowe układów scalonych z wbudowanymi wzmocnionymi zabezpieczeniami ESD. Należy bowiem pamiętać, że nie każdy układ opisywany np. jako „15 kV ESD-protected” faktycznie spełni wymogi normy dotyczącej systemowej ochrony ESD, tj. 61000-4-2.

Często zapis ten będzie się bowiem odnosił do badań wg modelu HBM (Human Body Model), a rzeczywista wytrzymałość przepięciowa okaże się znacznie niższa. Jeżeli zatem chcemy zaoszczędzić złotówkę i kilka...kilkanaście mm² powierzchni PCB poprzez rezygnację z dodatkowego transila – upewnijmy się najpierw, że wybrany konwerter RS485 (przykład można zobaczyć na rysunku 4), interfejs USB lub inny układ faktycznie przetrwa „strzały” z symulatora ESD. Więcej informacji na ten temat można znaleźć w artykule pt. „Elektroniczne komponenty zabezpieczające – podzespoły, aplikacje i normy”, który także publikujemy w tym numerze „Elektroniki Praktycznej”.

5. Sklep z kanapkami

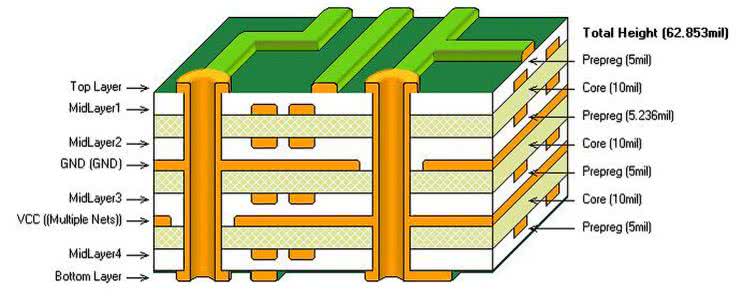

Kolejnym ważnym założeniem projektowym, które ma ogromny wpływ na optymalizację osiągów urządzenia w zakresie EMC, jest wybór optymalnego stosu wielowarstwowej płytki drukowanej. Warto w tym przypadku posiłkować się dokumentacją udostępnianą przez wybraną fabrykę – przyjęcie nierealistycznych lub nieekonomicznych założeń drastycznie zwiększy koszty produkcji, zaś podążanie ścieżką standardową (tj. zastosowanie jednego ze typowych stosów) pozwoli zachować relatywnie niski koszt i skrócić czas produkcji. Powszechnie wiadomo, że obwody wielowarstwowe dają projektantom znacznie większe możliwości m.in. w zakresie ekranowania krytycznych ścieżek w celu redukcji zakłóceń emitowanych i odbieranych z otoczenia. Równie ważne, a nawet jeszcze ważniejsze od grubości i ułożenia poszczególnych warstw dielektryka oraz miedzi (rysunek 5), będzie właściwe użycie dostępnych płaszczyzn. Kolejność ułożenia płaszczyzn masy i zasilania oraz warstw sygnałowych determinuje bowiem nie tylko ścieżki prądów powrotnych i pojemności międzypłaszczyznowe, ale także… istotnie zmienia warunki kontroli impedancji.

6. Pary idealne

W internetowych dyskusjach bardzo często pojawia się następujące pytanie: „jaki jest optymalny układ stosu warstw w przypadku płytki N-warstwowej”, gdzie N to dowolna parzysta liczba wskazana przez autora pytania. Jak to zwykle bywa w przypadku elektroniki, istnieje całkiem pokaźna liczba odpowiedzi, zaś każda z nich ma swoje grono zwolenników i przeciwników. Prowadzenie ścieżek sygnałowych tylko na warstwach wewnętrznych oraz zastosowanie jednolitych płaszczyzn miedzi na warstwach TOP i BOTTOM jest wprawdzie rozwiązaniem doskonałym pod względem EMC (zapewnia bowiem świetne ekranowanie całości mozaiki), jednak z oczywistych przyczyn stosowane bywa dość rzadko. Świetnym wyjściem jest także użycie stosu pokazanego schematycznie na rysunku 6 – wszystkie warstwy sygnałowe znajdują się blisko odpowiedniej płaszczyzny masy (łatwiejsza kontrola impedancji, jasno określone ścieżki prądów powrotnych), dolna płaszczyzna masy (5) jest oddzielona od płaszczyzny zasilania (4) jedynie cienką warstwą rdzenia (duża pojemność rozproszona wspomagająca odsprzęganie), a odległość między zasilaniem (4), a wewnętrzną warstwą sygnałową (3) pozostaje możliwie duża (słabe sprzęganie zakłóceń). Rzecz jasna, istnieje także wiele innych kombinacji – w każdym przypadku odpowiednia analiza stosunków grubości i kolejności par warstw miedzi okaże się niezwykle przydatnym narzędziem optymalizacji PCB pod względem integralności sygnałów i zasilania oraz minimalizacji zakłóceń promieniowanych.

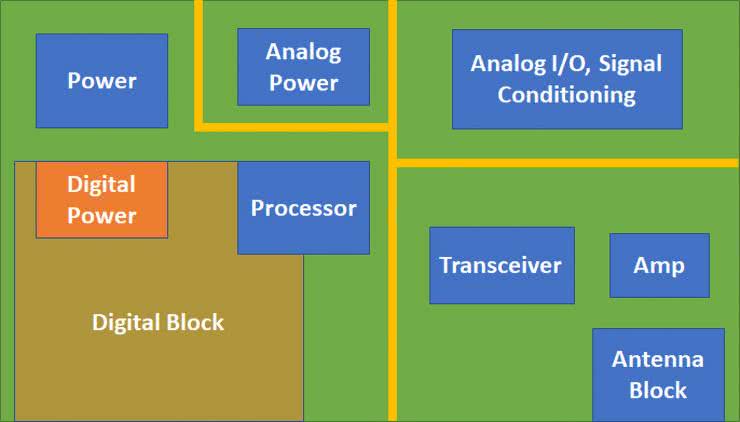

7. Zasada dobrego sąsiedztwa

O prawidłowym (z punktu widzenia EMC) ułożeniu bloków urządzenia na obszarze PCB napisano już dziesiątki artykułów i rozdziałów w specjalistycznych monografiach. Niestety, w praktyce nad wyraz często zdarza się, że spełnienie oczekiwań teoretycznych okazałoby się niemożliwe lub nieopłacalnie trudne. Podczas codziennej pracy dość rzadko mamy możliwość całkowicie dowolnego rozłożenia podsystemów na PCB, gdyż każdy z nich współpracuje z jakimiś złączami, elementami kontrolnymi, czy nawet mechaniczną lub optyczną częścią złożonego urządzenia. O ile bowiem na dużej płytce drukowanej możemy często dość daleko odsunąć czułe układy pomiarowe od modułu radiowego lub przetwornicy DC/DC (rysunek 7), o tyle przypadku PCB przeznaczonej np. do urządzenia ubieralnego każdy blok „będzie miał blisko” do wszystkich pozostałych. I tutaj w grę wchodzi doświadczenie projektanta – to, co można, należy od siebie poodsuwać, zaś na dalszym etapie projektowania trzeba sięgnąć po inne narzędzia – optymalizację płaszczyzn masy i zasilania, filtry i obwody odsprzęgające, a nawet… techniki programowe.

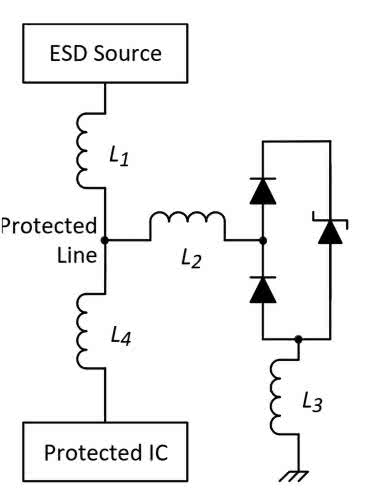

8. Długość ma znaczenie

Każdy projektant PCB doskonale wie, jak ważne jest ułożenie kondensatorów odsprzęgających (oraz części pozostałych komponentów dyskretnych) możliwie jak najbliżej wyprowadzeń układu scalonego. Producenci półprzewodników nie pozwalają nam zresztą o tym zapomnieć i profilaktycznie umieszczają stosowne „przypominajki” w każdej nocie katalogowej lub aplikacyjnej. Niestety, wielu konstruktorów wciąż popełnia błędy w zakresie routingu innych komponentów, chociażby transili – a przecież w tym przypadku każdy, najkrótszy nawet odcinek ścieżki, także odgrywa rolę pasożytniczej indukcyjności (rysunek 8), która może skutecznie odseparować chroniony komponent od źródła ryzykownych przepięć lub (w przypadku błędnego ustalenia proporcji poszczególnych odcinków mozaiki) – utrudnić ładunkom podążanie do transila i przekierować sporą ich część do wrażliwego układu scalonego. Dlatego też przed wysłaniem „gerberów" do fabryki warto sumiennie prześledzić (i w razie potrzeby skorygować) layout wejść oraz wyjść urządzenia (choć innym ścieżkom także się to należy).

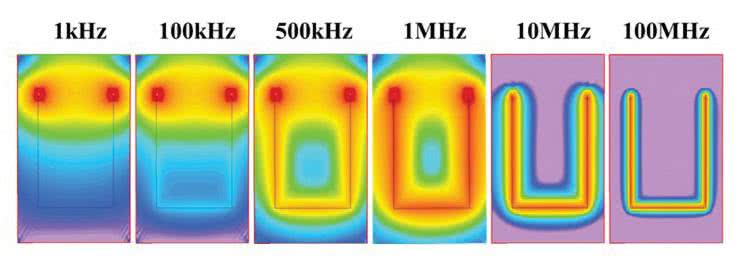

9. Tam i z powrotem

Ważnym zagadnieniem (o którym już zresztą wspomnieliśmy w niniejszym opracowaniu) jest optymalizacja projektu PCB pod względem zapewnienia właściwych ścieżek dla prądów powrotnych. W uproszczeniu możemy zdefiniować to zjawisko następująco: każdy przepływ ładunków z punktu A do punktu B na płytce drukowanej wiąże się z powstaniem prądu powrotnego, płynącego przez masę w kierunku przeciwnym (tj. z powrotem do źródła). Ścieżka powrotna zależy jednak od częstotliwości, gdyż „leniwy” prąd „wybierze” sobie drogę o najniższej możliwej impedancji. W zakresie częstotliwości niskich (do około 100 kHz) znaczna większość prądu powróci najkrótszą ścieżką, jednak w wyższych pasmach zacznie dominować składowa urojona impedancji – prąd powrotny, przez sprzężenie indukcyjne, będzie próbował wrócić do źródła tuż pod ścieżką główną (lub obok niej). Im więcej przeszkód na drodze prądu powrotnego, tym większe ryzyko nieprzewidzianych sprzężeń i emisji w różnych częściach obwodu drukowanego. To jest właśnie główny powód, dla którego prawidłowe zaprojektowanie PCB z zastosowaniem dzielonych płaszczyzn masy (zalecane w wielu materiałach dotyczących układów mixed-signal) jest tak trudne, a błędy na tym polu często stają się przyczyną jeszcze większych problemów.

10. Wespół w zespół

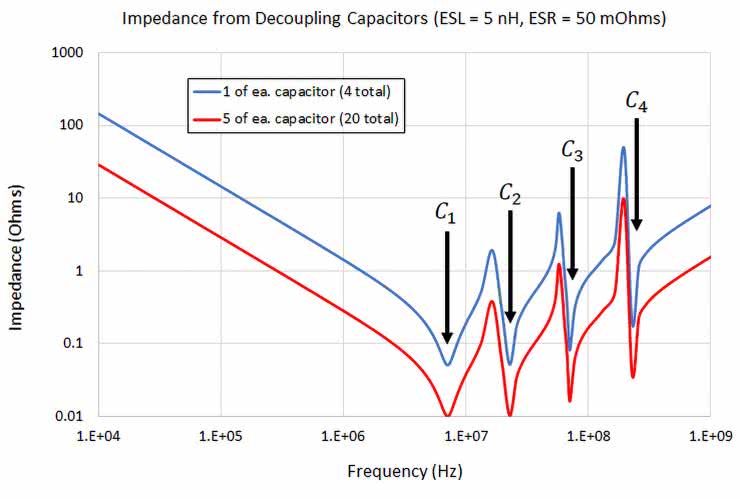

Bądźmy szczerzy – zdarza nam się lenistwo. My, elektronicy, mamy w swojej pracy bardzo często do czynienia z podobnymi lub wręcz identycznymi rozwiązaniami układowymi, powtarzanymi w ramach różnych projektów. W samym zastosowaniu sprawdzonych „w boju” rozwiązań nie ma oczywiście nic złego – co innego jednak, jeżeli bezrefleksyjnie powtarzamy je w każdej sytuacji. Dobrym przykładem będzie tutaj dobór wartości kondensatorów odsprzegających. W znakomitej większości przypadków do tego celu stosuje się pojemności 100 nF + 1...10 μF, ale przedmiotem głębszego zastanowienia bywa zwykle tylko wartość większego kondensatora, odpowiedzialnego w układzie za filtrację tętnień i zaburzeń przewodzonych w niskim paśmie częstotliwości. W szybkich układach cyfrowych i RF musimy jednak operować w pełnym spektrum używanym w danym urządzeniu – dlatego też często spotykane jest rozwiązanie, w którym łączymy równolegle całą baterię kondensatorów, np. 3 lub 4 elementy o pojemnościach różniących się pomiędzy sobą kolejno o rząd wielkości. Takie rozwiązanie pozwala znacząco obniżyć impedancję i efektywniej stłumić także zaburzenia o najwyższej częstotliwości (w tym harmoniczne wyższych rzędów).

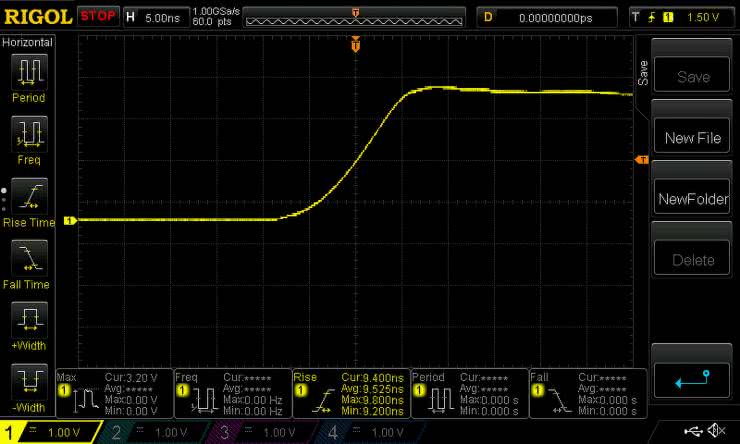

11. Spiesz się powoli

W świecie komputerów dość popularną techniką jest podkręcanie częstotliwości taktowania procesora w celu uzyskania wyższej wydajności obliczeniowej. Na gruncie projektowania elektroniki także mamy do czynienia ze stopniowym zwiększaniem maksymalnej częstotliwości zegara mikrokontrolerów i procesorów aplikacyjnych – nie oznacza to jednak, że zawsze należy „jechać po bandzie”. Z punktu widzenia kompatybilności elektromagnetycznej (ale także pod względem zużycia energii) wskazane jest bowiem możliwie jak najmocniejsze obniżenie częstotliwości taktowania, co pozwala wydatnie zredukować pasmo emitowanych zaburzeń radiowych. Podobnie dzieje się także w przypadku linii sygnałowych – przykładowo, jeżeli do wiązki kablowej lub przewodu FPC/FFC wprowadzamy sygnały cyfrowe, warto lekko złagodzić ich zbocza, ponieważ dłuższe czasy narastania i opadania to także niższe pasmo zaburzeń. Współczesne mikrokontrolery ułatwiają zresztą to zadanie – przykładowo układy STM32 oferują możliwość programowego spowolnienia dynamiki przełączania portów GPIO poprzez zapis odpowiedniego rejestru konfiguracyjnego (rysunek 11).

12. Zasłona milczenia

Nawet najlepiej zaprojektowana płytka drukowana potrzebuje czasem dodatkowego wsparcia. Jeżeli dane urządzenie jest wyjątkowo wrażliwe na zakłócenia (jak np. czułe obwody pomiarowe lub tory RF) bądź też samo generuje silne zaburzenia, niezbędne może okazać się zastosowanie ekranowania. Oprócz użycia metalowych obudów, można także posiłkować się napylaniem warstw lakieru na bazie proszków metalicznych na wewnętrzną powierzchnię tworzywowej obudowy (fotografia 1). Szczególnie dużo uwagi należy poświęcić wszelkim otworom – niezależnie od tego, czy są one wykonane pod złącza, wyświetlacze, czy też wentylatory, zawsze będą stanowiły otwarte wrota dla zaburzeń propagujących do/z wnętrza urządzenia. W niektórych przypadkach sensowne będzie także rozważenie ekranów lokalnych, wykonanych w formie metalowych puszek lutowanych lub zatrzaskiwanych w specjalnych zaciskach na samej płytce drukowanej. Współczesna elektronika dysponuje ponadto pełnym arsenałem dodatkowego wyposażenia ekranującego, do którego należą: dławnice przewodzące, metaliczne siatki do osłony otworów wentylacyjnych, panele do ekranowania wyświetlaczy, czy też specjalne zaciski łączące oploty kabli z szyną DIN lub metalową obudową. Warto pamiętać, że sama obecność ekranu nie wystarczy – trzeba jeszcze zadbać o odpowiednie, niskoimpedancyjne połączenie go z masą urządzenia lub uziemieniem, gdyż bez tego nawet najlepszy ekran nie zapewni wymaganego poziomu tłumienia zaburzeń RFI.

13. Software (też) ma tę moc

Zagadnienia EMC tylko z pozoru mogą stanowić pole do popisu wyłącznie dla projektantów hardware’u. W rzeczywistości jednak sporo do zdziałania mają tutaj także programiści systemów wbudowanych. O ile bowiem ograniczenie emisji zaburzeń po stronie firmware’u sprowadza się głównie do opisanych wcześniej sposobów (zastosowanie wolniejszego taktowania i mniej stromych zboczy sygnałów cyfrowych), o tyle już w zakresie odporności istnieje dużo więcej zadań dla programistów. Należy bowiem pamiętać, że testy EMC dotyczą nie tylko tego, czy dany sprzęt „przeżyje” wyładowanie z symulatora ESD bądź generatora zaburzeń EFT – niebagatelne znaczenie, zwłaszcza w przypadku urządzeń krytycznych z punktu widzenia bezpieczeństwa (np. aparatury medycznej, elektroniki pokładowej w branżach motoryzacyjnej i lotniczej, czy też sprzętu militarnego) ma także odpowiednia reakcja na silne zakłócenia, które często mogą całkowicie zdezorientować procesor bądź nasycić wzmacniacze w czułym torze pomiarowym. Najprostszy przykład to zastosowanie odpowiednio solidnych procedur debouncingu, czyli eliminacji drgań styków. Jeżeli program zostanie odpowiednio zabezpieczony, to poradzi sobie nie tylko z mechanicznymi wibracjami spowodowanymi sprężystością blaszek kontaktowych przycisku, ale także z zaburzeniami przewodzonymi lub indukowanymi w okablowaniu wewnętrznym. Inne techniki obejmują m.in. zastosowanie watchdogów, układów POR i BOR, zewnętrznych obwodów nadzorczych, czy też obszarów pamięci podtrzymywanych bateryjnie (backup domain).

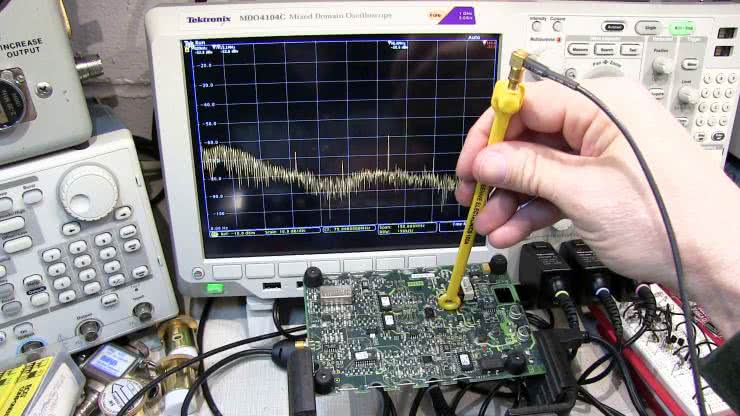

14. Dzwoni… ale w którym kościele?

Niezwykle wartościowym narzędziem podczas wstępnego „przeszukiwania” PCB w celu określenia źródeł niepożądanych emisji są sondy pola bliskiego (fotografia 2). Pozwalają one nie tylko na ustalenie przybliżonego położenia źródła (np. układu scalonego odpowiedzialnego za generowanie zaburzeń), ale wręcz na zlokalizowanie najbardziej problematycznych ścieżek. Duże znaczenie ma tutaj kierunkowy charakter sond pola magnetycznego (H-field), których czułość jest największa tylko w jednej orientacji względem badanego przewodnika. Pewnym problemem okazuje się silny wpływ odległości sonda-PCB na amplitudę mierzonego sygnału – przy odrobinie zachodu da się jednak tak przygotować stanowisko pomiarowe, by możliwe było prowadzenie pomiarów porównawczych (np. przed i po wymianie dławika lub kondensatora odsprzęgającego). Jeszcze bardziej powtarzalne warunki stwarzają komory TEM – umożliwiają one ponadto przekonwertowanie wyników pomiaru na postać porównywalną (w pewnym ograniczonym zakresie) z wynikami otrzymywanymi podczas testów w pełnowymiarowych komorach SAC. I choć konwersja z pola bliskiego na pole dalekie nie jest zagadnieniem prostym pod względem matematycznym, to mimo wszystko zastosowanie TEM w testach inżynierskich okazuje się niezwykle cennym narzędziem, daje bowiem pewną zgrubną aproksymację wyników, których należy spodziewać się po pełnych badaniach EMC w profesjonalnym laboratorium. Mało tego – przy zastosowaniu odpowiedniego wzmacniacza mocy oraz generatora RF lub wyjścia TG (generatora śledzącego) dostępnego w analizatorze widma, możliwe jest wstępne testowanie odporności prototypu na zakłócenia propagowane drogą radiową.

Podsumowanie

W artykule zebraliśmy zestaw czternastu wybranych porad dotyczących prawidłowego podejścia do projektowania urządzeń elektronicznych w zgodzie z normami EMC. Staraliśmy się przy tym objąć możliwie szeroki zakres zagadnień – począwszy od wstępnej fazy procesu projektowego, aż po wykonywanie badań inżynierskich. Czytelników zainteresowanych omówioną tematyką gorąco zachęcamy do samodzielnych poszukiwań oraz… do studiowania oryginalnych norm, gdyż tylko takie podejście pozwala dogłębnie zrozumieć złożony, ale także bardzo interesujący świat kompatybilności elektromagnetycznej.

inż. Przemysław Musz, EP

Zaloguj

Zaloguj