Wszechświat jest przepełniony różnymi rodzajami promieniowania. W większości środowisk, tutaj na ziemi, jesteśmy odizolowani od niego, ale wraz z coraz intensywniejszą eksploracją przestrzeni kosmicznej, przez coraz precyzyjniejszą elektronikę, problem ten staje się coraz wyraźniejszy. W ciągu ostatnich dekad na całym świecie wysłano wiele bezzałogowych i załogowych misji w przestrzeń kosmiczną. Te naszpikowane elektroniką pojazdy muszą być ekstremalnie niezawodne z uwagi na koszty misji kosmicznych, jak i potencjalne zagrożenie życia, w przypadku misji załogowych.

Urządzenia elektroniczne byłyby nieprzydatne na orbicie, gdyby nie tolerowały promieniowania kosmicznego i regularnie ulegały awariom. Z tego powodu promieniowanie, jego wpływ na elektronikę i różne metody zapobiegania lub korygowania niekorzystnego wpływu promieniowania na obwody elektroniczne stały się dużym obszarem badań w inżynierii lotniczej. Projektowanie i wykonywanie obwodów lub urządzeń odpornych na promieniowanie nazywa się często hartowaniem radiacyjnym obwodu lub urządzenia. Oznacza to, że urządzenia lub obwody są utwardzone na działanie promieniowania i stąd nazwa – rad-hard.

Spośród wielu technologii, które są stosowane do implementacji struktur rad-hard, takich jak elementy CMOS, BJT i FPGA, układy CMOS zyskały ogromną popularność, jako korzystna opcja dla elektroniki kosmicznej. Zalety, jakie mają – niewielki rozmiar, duża szybkość działania, a co najważniejsze, ich zdolność do pracy przy niskim zużyciu energii, są niesamowicie istotne w przypadku urządzeń pracujących w kosmosie przy bardzo ograniczonym budżecie mocy.

Istnieje kilka aspektów, jakie są optymalizowane w układach, aby utwardzić je na wpływ promieniowania. Zabiegi te skupiają się głównie w dwóch obszarach – konstrukcji samych urządzeń półprzewodnikowych oraz architekturze układu, która jest istotna zwłaszcza w przypadku systemów cyfrowych, gdzie rozwiązania programowe mogą kompensować pewną część problemów wywoływanych przez promieniowanie. W dalszej części artykułu przyjrzymy się obu obszarom, które służą do utwardzania systemów elektronicznych.

Mechanizmy oddziaływania promieniowania

Istnieje kilka mechanizmów opisujących, jak różnego rodzaju promieniowanie oddziałuje z urządzeniami półprzewodnikowymi. Sposób i siła tego oddziaływania zależne są głównie od rodzaju cząstki i jej energii. Wysokoenergetyczne cząstki, które silnie oddziałują z jądrami powodują uszkodzenia półprzewodnika, zmianę domieszkowania itd., przyczyniając się do degradacji elementu i finalnie jego uszkodzeniu. Rozpędzone elektrony z kolei, uderzając w półprzewodnik, mogą powodować jego jonizację, co ma wpływ na działanie i może indukować zakłócenia w postaci szpilek napięcia. To może doprowadzić do uszkodzenia układu. Dokładniejszy opis tych mechanizmów można znaleźć w drugim artykule poświęconym tematyce rad-hard, jaki prezentujemy w tym wydaniu „Elektroniki Praktycznej”.

Awarie

Kiedy ciężki jon uderza w obwód elektroniczny i przechodzi przez jego czuły punkt, generuje przejściowy impuls napięcia w tym punkcie. Nazywa się to zdarzeniem przejściowym (SET). Kiedy taki jon uderza np. obszar dyfuzji w urządzeniu MOS, SET indukuje jonizację w tym obszarze, co często powoduje zmianę stanu logicznego. Tego rodzaju błędy stanów są określane, jako zakłócenia pojedynczego zdarzenia (SEU).

Impuls jonizacji indukowany przez ciężkie jony może spowodować włączenie struktury tyrystorowej p-n-p-n (obecnej w objętościowych obwodach CMOS). Powoduje to utrzymanie struktury w niskiej impedancji między katodą a anodą, a pasożytniczy tyrystor pozostaje włączony przez cały czas. Nazywa się to zatrzaśnięciem układu może być bardzo destrukcyjnym efektem promieniowania jonizującego, ponieważ powoduje, że urządzenie nie reaguje na żadne sygnały sterujące.

Uszkodzenia

Do uszkodzeń urządzenia dochodzi na skutek kilku mechanizmów. Wszystkie one prowadzą finalnie do awarii układu, jednak mogą się różnic tempem, czy też dynamiką pojawiania się. Pewne uszkodzenia będą nagłe, inne będą powodowały powolne pogarszanie parametrów układu.

Jonizacja nośników w półprzewodniku może doprowadzić nie tylko do przełączenia się stanu logicznego w układzie, ale także do powstania lokalnego zwarcia, co oczywiście prowadzi do przepływu sporego prądu, który może uszkodzić dany fragment struktury półprzewodnikowej.

W przypadku innych zjawisk obserwuje się dwa mechanizmy – kinetyczne uszkodzenia półprzewodników, na skutek zderzeń pomiędzy atomem półprzewodnika i cząstką promieniowania (najczęściej zjonizowanym jonem, protonem itp.) oraz efekty atomowe, np. transmutacja, na skutek zderzenia neutronu z jądrem atomowym.

Pierwszy z efektów powoduje powstanie defektu, a nawet dwóch, w strukturze półprzewodnikowej. W momencie, gdy atom zostaje wybity z sieci krystalicznej, pozostaje po nim puste miejsce, tzw. wakans, który jest rodzajem defektu struktury krystalicznej półprzewodnika. Wybity atom lokuje się poza siecią, formując tzw. atom pozasieciowy – inny rodzaj defektu. Tego rodzaju defekty półprzewodnika powodują, generalnie, pogorszenie jego rozmaitych parametrów, związanych z przewodnictwem itp.

Drugi z efektów skutkuje zmianą atomów krzemu czy domieszek w inne atomy na skutek reakcji jądrowych. Dokładny opis tych procesów wykracza poza ramy tego artykułu, ale wystarczy wspomnieć, że może prowadzić do zmiany domieszkowania półprzewodnika z N na P i odwrotnie. Trochę więcej informacji na temat tych zjawisk znaleźć można w sąsiednim artykule poświęconym wpływowi promieniowania na półprzewodniki. Oczywiście, w przypadku degradacji na skutek pojawiania się defektów czy transmutacji atomów i zmian domieszkowania półprzewodnika, kluczem jest skala. Pojedyncze zdarzenie tego rodzaju nie ma istotnego wpływu na większość urządzeń półprzewodnikowych. Jednak uszkodzenia te, z biegiem czasu w promieniotwórczym środowisku, kumulują się, w końcu doprowadzając do istotnego pogorszenia parametrów układu, czyniąc go, de facto, nieużywalnym – niesprawnym.

Rozwiązania sprzętowe

Podstawowym krokiem, jaki można przedsięwziąć, jest utwardzenie samych urządzeń półprzewodnikowych. Robi się to na ogół na etapie projektowania i wytwarzania struktur półprzewodnikowych tych urządzeń, dlatego też w tym artykule omówimy jedynie główne techniki, stosowane w tych procesach, nie zagłębiając się zbytnio w ich mechanizmy działania. Tematyka projektowania i wytwarzania struktur półprzewodnikowych, jakkolwiek szalenie ciekawa, leży poza zakresem tematycznym EP.

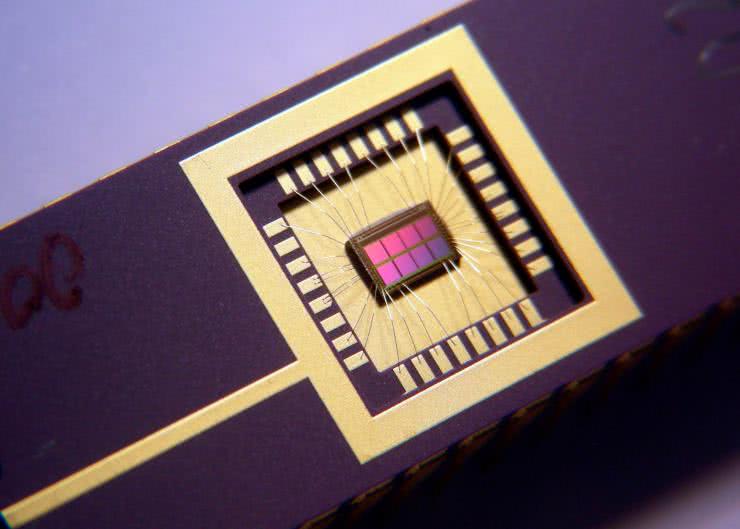

Podłoża izolacyjne

Utwardzone chipy są często produkowane na podłożach izolacyjnych zamiast zwykłych substratów półprzewodnikowych. Powszechnie stosowane są technologie, takie jak krzem na izolatorze (SOI) czy nawet krzem na szafirze (SOS). SOI wykorzystuje warstwę izolującą na podłożu krzemowym zamiast konwencjonalnych substratów krzemowych w celu zmniejszenia pojemności pasożytniczych. Różnica między urządzeniami SOI a konwencjonalnymi polega głównie na tym, że złącze krzemowe znajduje się nad izolatorem elektrycznym. Pierwsze przemysłowe wdrożenie SOI miało miejsce w sierpniu 1998 roku. Korzyści płynące z techniki SOI w porównaniu z konwencjonalnym technologiami produkcji to:

- niższa pojemność pasożytnicza dzięki izolacji od krzemu objętościowego w substracie,

- poprawiona odporność na zatrzaśnięcie dzięki całkowitej izolacji struktur domieszkowanych N oraz P.

Z punktu widzenia produkcji podłoża SOI są kompatybilne z większością konwencjonalnych procesów. Podstawową barierą we wdrażaniu SOI jest drastyczny wzrost kosztów substratów, który przyczynia się do wzrostu całkowitego kosztu produkcji o około 10...15%.

SOS to heteroepitaksjalny proces produkcji układów scalonych, składający się z cienkiej warstwy krzemu wyhodowanej na płytce szafirowej. Proces ten jest częścią rodziny technologii CMOS SOI. Jest używany głównie w zastosowaniach lotniczych i wojskowych ze względu na swoją naturalną odporność na promieniowanie. Pierwsza zaleta szafiru polega na tym, że jest on doskonałym izolatorem elektrycznym, zapobiegającym rozprzestrzenianiu się prądów błądzących spowodowanych promieniowaniem. Drugą zaletą jest to, że może być on wytwarzany w tych samych fabrykach, które produkują zwykłe układy na zwykłych substratach krzemowych. Wadami SOS jest głównie bardziej złożony proces produkcji i wysoka cena podłóż szafirowych. Dodatkowo, podłoża te są cięższe niż układy krzemowe, co w pewnych przypadkach może być problemem.

Jeśli chodzi o tolerancję na promieniowanie, podczas gdy zwykłe chipy komercyjne mogą wytrzymać od 5 do 10 krad, chipy klasy kosmicznej produkowane w technologii SOI lub SOS mogą przetrwać dawki, o co najmniej kilka rzędów wielkości wyższe. Kiedyś wiele chipów z serii 4000 było dostępnych w wersjach utwardzanych, obecnie układy te są mniej popularne.

Bipolarne układy scalone

Bipolarne układy scalone zawierają tranzystory bipolarne (BJT) jako główne elementy. Tranzystory tego rodzaju do działania potrzebują zarówno elektronów, jak i dziur. Przepływ ładunku w BJT wynika z dwukierunkowej dyfuzji nośników ładunku przez złącze między dwoma obszarami o różnych stężeniach nośników. Ten sposób działania kontrastuje np. z tranzystorami polowymi, w których tylko jeden typ nośnika jest zaangażowany w działanie.

Nowa koncepcja Super Junction (SJ) dla energoelektroniki może pomóc w podtrzymaniu trendu zmniejszania strat przełączania przyszłej elektroniki. Tranzystory bipolarne z SJ (SJBT) wykazują wiele podobieństw z superzłączowym tranzystorem MOSFET. Po kilku dekadach rozwoju, pseudomorficzny tranzystor o dużej ruchliwości elektronów wykonany z GaAs (pHEMT) okazał się być urządzeniem o wysokiej sprawności i niskim koszcie, który można komercyjnie produkować. Tego rodzaju elementy mogą skutecznie konkurować z układami polowymi, co jest istotne, bo jeśli chodzi o tolerancję na promieniowania, bipolarne układy scalone mają generalnie wyższą tolerancję promieniowania niż obwody CMOS. Seria LS5400 może wytrzymać 1000 krad, a wiele urządzeń ECL może wytrzymać do 10 000 krad.

SRAM odporny na promieniowanie

Aby tolerować promieniowanie, pamięć DRAM bazująca na kondensatorach jest często zastępowana przez bardziej wytrzymałą (ale większą i droższą) pamięć SRAM. Urządzenie SRAM używane są głównie do odczytu, w aplikacjach takich, jak pamięć konfiguracyjna dla układów FPGA, można uodpornić na efekty promieniowania do bardzo wysokiego poziomu, dodając rezystor o dużej wartości do komórek pamięci.

Urządzenie SRAM używane głównie w stanie odczytu są zwykle zapisywane tylko raz po włączeniu zasilania, aby zdefiniować funkcję układu scalonego, a w większości aplikacji nigdy nie jest zmieniana zawartość zaprogramowanej po włączeniu zasilania pamięci. Możliwa jest również produkcja SRAM na podłożach SOI, co oferuje wartościową charakterystykę utwardzania układu pamięci na wynik pojedynczego zdarzenia (SEU) czy zwiększenia całkowitej dopuszczalnej dawki promieniowania dla takiego układu.

Podłoże z materiału o szerokim pasmie wzbronionym

Wyższą tolerancję na defekty można uzyskać stosując podłoże o szerokiej przerwie energetycznej, gdyż materiały te na ogół mają małe atomy i silnie elektroujemne wiązania atomowe, co zmniejsza prawdopodobieństwo wytwarzania defektów przez promieniowanie.

Półprzewodniki z szeroką przerwą energetyczną, takie jak azotek galu (GaN) czy węglik krzemu (SiC), okazały się jednymi z najbardziej obiecujących materiałów na przyszłe komponenty elektroniczne wysokiej mocy. Oferują one ogromne korzyści w zakresie sprawności energetycznej, ale także wysoką niewrażliwość na promieniowanie, możliwość działania w wysokich temperaturach itp. Nadal w tym zakresie prowadzi się wiele prac badawczo-rozwojowych. W szczególności konieczna jest poprawa jakości substratów krystalicznych, aby zwiększać wydajność i niezawodność tych elementów. Konieczne są także dalsze prace badawcze, aby lepiej zrozumieć fizykę tych półprzewodników, poprawić wzrost materiałów i dalej zoptymalizować sprawność tych urządzeń.

Ochrona układu przed promieniotwórczością

Jest to intuicyjne działanie, mające na celu zmniejszenie ekspozycji struktury krzemowej na promieniowanie. Naukowcy badają różne materiały, nawet tak egzotyczne jak gleba księżycowa, jako osłonę przed promieniowaniem kosmicznym. Badania te opierają się na pomiarach, jak i modelowaniu zjawisk fizycznych. Zastosowanie odpowiednich materiałów zapewnia znaczną ochronę przed pierwotnym promieniowaniem kosmicznym i zdarzeniami związanymi z cząstkami słonecznymi. Głównym czynnikiem, jaki mówi o efektywności w ekranowaniu danego pierwiastka jest jego liczba atomowa Z – im wyższa, tym generalnie dany ekran jest skuteczniejszy. Badane są metale takie jak aluminium reprezentujące materiał o niskim/średnim Z czy wolfram reprezentujący materiał o wysokim Z. Wyniki obliczeń wskazują, że dla tłumienia promieniowania wymaganego dla typowej elektroniki używanej w misji Jowisza, materiał o niskim Z w połączeniu z materiałem o wysokim Z są gorszą osłoną na tę samą masę powierzchniową materiału o wysokim Z. Jednakże, gdy do ochrony elektroniki bardzo wrażliwej na promieniowanie wymagane jest masywne ekranowanie o masie powierzchniowej powyżej 10 g/cm2, wówczas połączenie warstw z niską i wysoką liczbą atomową zapewnia optymalniejszy i co istotne lżejszy ekran radiacyjny.

Wytwarzanie chipów za pomocą zubożonego boru

Zubożony bor składa się tylko z izotopu boru-11. Jest to istotne, ponieważ promieniowanie kosmiczne wytwarza wtórne neutrony, jeśli uderzy w struktury statku kosmicznego, a neutrony powodują rozszczepienie boru-10, jeśli jest on obecny w półprzewodnikach statku kosmicznego. Podczas takiego rozszczepiania wytwarza się promieniowanie gamma, cząstka alfa i jon litu. Powstałe produkty rozszczepienia mogą przekazać swój ładunek do pobliskich struktur półprzewodnikowych, powodując różnego rodzaju problemy.

W konstrukcjach półprzewodników utwardzanych na promieniowanie jednym ze środków zaradczych jest użycie zubożonego boru do domieszkowania. Prawie nie zawiera on boru-10. Bor-11 jest w dużej mierze odporny na promieniowanie. Ogólnie rzecz biorąc, zubożony bor jest stosowany w warstwie pasywacyjnej szkła borokrzemianowego w celu ochrony układów scalonych. Szkło borofosfokrzemianowe (BPSG), jest rodzajem szkła krzemianowego, które zawiera dodatki zarówno w postaci boru, jak i fosforu.

Rozwiązania architektoniczne i programowe

Inne techniki hartowania systemów obejmują stosowanie środków logicznych, programowych i architektonicznych, aby zwiększyć odporność całego systemu na promieniowanie. Wymagają one oceny niezawodności systemu, aby wykryć miejsca kluczowej podatności i móc zastosować odpowiednie środki zaradcze.

Korekcja błędów pamięci

Pamięć DRAM zapewnia zwiększoną ochronę przed błędami w oparciu o kody korekcji błędów. Pamięć z korekcją błędów, znana, jako pamięć ECC (Error Correcting Codes) jest szczególnie odpowiednia dla aplikacji o wysokiej odporności na błędy, takich jak serwery, a także aplikacji kosmicznych ze względu na promieniowanie. Zawiera dodatkowe bity parzystości do sprawdzania i ewentualnie poprawiania uszkodzonych danych.

Ponieważ efekty promieniowania mogą zmienić zawartość pamięci, nawet, jeśli system nie uzyskuje w danym momencie dostępu do pamięci RAM, do ciągłego czyszczenia pamięci RAM należy używać tak zwanego obwodu skrubera. Zwykle następuje to w trzech krokach podczas odświeżania pamięci:

- odczyt danych,

- sprawdzanie bitów parzystości pod kątem błędów danych,

- zapisywanie poprawek do pamięci RAM.

Tradycyjne kontrolery pamięci z korekcją błędów wykorzystują tzw. kody Hamminga, chociaż niektóre mogą korzystać z potrójnej redundancji modułowej (TMD). Przeplot pozwala rozłożyć efekt pojedynczego promienia kosmicznego, który potencjalnie zaburza wiele fizycznie sąsiadujących bitów w wielu słowach poprzez powiązanie sąsiednich bitów z różnymi słowami. Dopóki pojedynczy błąd zdarzenia (SEU) nie ma zasięgu większego niż pewien ustalony próg błędu w jakimkolwiek konkretnym słowie między dostępami, można go poprawić i utrzymać wolne od błędów dane dla systemu.

Schematy korekcji błędów są szeroko stosowane zarówno w architekturach pamięci, jak i przy komunikacji. Jednak najnowocześniejsze technologie CMOS i dyskowe mają bardzo mały poziom błędów, który może sięgać zaledwie jednego miliarda, dlatego rygorystyczna korekcja błędów nie zawsze jest konieczna. Wraz z postępującą miniaturyzacją układy są jednak coraz bardziej narażone na błędy w sygnałach, przez co konieczne jest wprowadzanie nowych rozwiązań. W skali nano wymagane są silniejsze i wielokrotne kody korygujące błędy, takie jak kody BCH. Czy też nowe układy do realizacji procedur dekodowania i kodowania kodów Hamminga, w którym zwiększa się niezawodność pamięci kosztem tylko kilku nanosekund opóźnienia w czasie dostępu do pamięci.

Chociaż kody Hamminga są w stanie skorygować pojedynczy błąd w bloku fizycznych bitów, stają się mniej produktywne w przypadku wysokiego wskaźnika błędów. W zastosowaniach praktycznych kod BCH (250, 32, 45) może zapewnić 99,9956% poprawności przy nawet 10% bitowej stopie błędów w pamięci, ale oczekuje się, że 1 bajt na każde 711 bajtów będzie wadliwy. Ogólnie rzecz biorąc, jeśli użyjemy tylko kodów korekcji błędów, konieczne będzie implementowanie bardzo silnych i złożonych kodów korekcji błędów, co spowoduje duży narzut w obszarze złożoności obliczeniowej czy opóźnień. Tym samym traci się też zalety, wynikające z stosowania pamięci produkowanych w technologiach z bardzo małym wymiarem charakterystycznym. Między innymi to jest przyczyną, że układy o zastosowaniach kosmicznych produkuje się raczej w starszych procesach technologicznych.

Redundancja podatnych elementów

W inżynierii redundancja to powielanie krytycznych komponentów systemu w celu zwiększenia jego niezawodności. W wielu systemach o znaczeniu krytycznym dla bezpieczeństwa, np. awionice, niektóre części systemu sterowania powinny być nawet potrojone. W potrójnie redundantnym systemie jego trzy komponenty podrzędne muszą ulec awarii, zanim nastąpi awaria całego systemu. Ponieważ każdy z nich rzadko zawodzi i oczekuje się, że zawiedzie niezależnie. Prawdopodobieństwo, że wszystkie trzy zawiodą jednocześnie jest (dostatecznie) małe.

Nadmiarowe elementy mogą być stosowane na poziomie systemu lub na poziomie obwodu. Na poziomie systemu można zastosować np. trzy oddzielne płytki mikroprocesorowe, które mogą działać niezależnie. Można dodać logikę, aby wykrywać i wyłączyć płytkę w przypadku powtarzających się błędów. Na poziomie obwodu z kolei pojedynczy bit można zastąpić trzema bitami i oddzielną logiką głosowania dla każdego bitu, aby w sposób ciągły określać jego wynik. Jednak ta strategia zwiększy obszar chipa pięciokrotnie, więc zarezerwowana jest tylko dla mniejszych projektów.

Podejście z zastosowaniem potrójnej redundancji ma tę zaletę, że systemy tego rodzaju w zasadzie nie mają negatywnego wpływu na wydajność działania systemu, w odróżnieniu od np. układów z zegarami kontrolnymi itp. opisanymi poniżej.

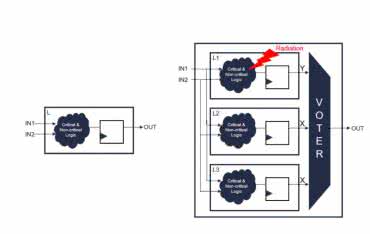

Systemy wielordzeniowe z głosowaniem

O szczególnym przypadku redundancji mówi się w przypadku systemów głosujących. Jest to architektura wykorzystująca kluczowe układy logiczne w postaci minimum trzech, równolegle pracujących systemów, połączonych na końcu układem „głosującym”. Obwód ten porównuje wyjścia tych identycznych subsystemów i wybiera odpowiedź większości. Na rysunku 1 pokazano tego rodzaju architekturę w postaci schematu blokowego.

Jeśli jeden z obwodów doświadcza zdarzenia wywołanego promieniowaniem, które wpływa na wyjście, to jego wyjście będzie się różnić od pozostałych dwóch obwodów. Gdyby porównano tylko dwa identyczne obwody, różny stan wyjść pozwoli zidentyfikować, że nastąpiło zdarzenie, ale nie obwód, w którym wystąpiło, ani prawidłowy wynik działania. Przy trzech obwodach można określić prawidłowe wyjście (w oparciu o rozsądne założenie, że prawdopodobieństwo wystąpienia identycznych błędów w dwóch obwodach jest praktycznie zerowe). W zależności od oprogramowania, system może następnie zaakceptować dane wyjściowe większości modułów lub ponowić operację.

Na rynku dostępne są systemy tego rodzaju. W przypadku mikrokontrolerów/procesorów, umieszcza się w jednej obudowie trzy rdzenie. Często są one taktowane zegarem przesuniętym w fazie względem siebie i fizycznie rozsunięte lub obrócone, aby zminimalizować prawdopodobieństwo wystąpienia błędu w dwóch rdzeniach naraz.

Zegary kontrolne

W systemach krytycznych stosuje się również tzw. zegary nadzorujące, które mogą być wykorzystane do wykonania twardego resetu systemu, chyba, że zostanie wykonana jakaś sekwencja, która ogólnie wskazuje, że system działa, na przykład operacja zapisu z wbudowanego procesora. Przykładem takiego zegara może być Watchdog, implementowany w większości mikrokontrolerów.

Jeśli promieniowanie spowoduje nieprawidłową pracę procesora, jest mało prawdopodobne, że oprogramowanie będzie działać wystarczająco poprawnie, aby np. wyczyścić licznik czasu zegara nadzorującego. Watchdog, gdy licznik zostanie przepełniony, wymusi reset systemu. Jest to uważane za ostatnią deskę ratunku w porównaniu do innych metod utwardzania radiacyjnego.

Ocena niezawodności

Należy zauważyć, że oprócz powyższych technik hartowania, bardzo ważnym tematem jest również sposób testowania niezawodności układu scalonego. Istnieje wiele technik i podejść statystycznych do testowania układów. Najnowsze z nich bazują na rozkładzie Weibulla. Kluczowe jest połączenie metod empirycznych i statystycznych bazujących na danych z testów żywotności układów, aby oszacować niezawodność komponentów systemu.

Kluczowe jest zbadanie wpływu czynników na przyspieszoną degradację układu, do czego często stosuje się sztuczne źródła promieniowania, takie jak np. akceleratory. Pozwala to na symulowanie określonych rodzajów promieniowania, a co za tym idzie, studiowanie jego wpływu na gotowy system, jego awaryjność, przyspieszone starzenie itd.

Podsumowanie

Zaprezentowane strategie zabezpieczania urządzeń półprzewodnikowych pozwalają zmniejszyć zawodność elektroniki narażonej na promieniowanie jonizujące, kosmiczne i inne. Tego rodzaju promieniowanie występuje w wielu środowiskach, ale kluczowe sektory, w jakich analizuje się podatność urządzeń półprzewodnikowych to systemy kosmiczne (satelity, pojazdy kosmiczne i inne), układy pracujące w reaktorach atomowych, systemy awioniki oraz, z uwagi na wymaganie wysokiej niezawodności, krytyczne elementy układów bezpieczeństwa itp. w systemach medycznych i bezpieczeństwa funkcjonalnego w przemyśle.

Poruszone w artykule aspekty sprzętowego zabezpieczania struktur półprzewodnikowych są, na ogół, poza zasięgiem elektroników, projektujących urządzenia elektroniczne. Nie oznacza to, że nie są one istotne. Dobierając układy do systemu narażonego na promieniowanie, należy starać się sięgać po układy rad-hard, które posiadają nie tylko zwiększoną odporność na promieniowanie, ale także są przebadane pod tym kątem, co pozwala na oszacowanie podatności i zawodności systemu. Szacowanie podatności systemu jest istotne, aby wprowadzić architektoniczne i programistyczne mechanizmy kompensowania podatności na promieniowanie. Istotna jest jednak wiedza, gdzie mogą występować problemy i jak często należy się ich spodziewać.

Zachowując odpowiednie podejście, modelując i testując zawodność układu, a także wprowadzając odpowiednie środki zapobiegawcze na poziomie sprzętu i oprogramowania, można uzyskać systemy, które będą spełniały wymagania pracy w nawet najbardziej wymagających środowiskach, gdzie elementy elektroniczne narażone są na wysokie poziomy promieniowania.

Nikodem Czechowski, EP

Bibliografia:

- Y. Fa-Xin, L. Jia-Rui, Zheng-Liang Huang, L. Hao, L. Zhe-Ming, „Overview of Radiation Hardening Techniques for IC Design”, Information Technology Journal 9 (2010).

- R. Garg, N. Jayakumar, S. P. Khatri and G. S. Choi, „Circuit-Level Design Approaches for Radiation-Hard Digital Electronics” IEEE Transactions on Very Large Scale Integration (VLSI) Systems 17 (2009).

- S. Nimmakayala, „A Survey of Radiation Hardened CMOS Techniques”, praca dyplomowa na Dept. of Electrical and Computer Engineering, Montana State University, 2009.

- https://bit.ly/3vDx7ic

- Y. Q. de Aguiar, „Predictive tools and Radiation-Hardening-by-Design (RHBD) techniques for SET and SEU in digital circuits”. Electronics. Université Montpellier, 2020

Zaloguj

Zaloguj