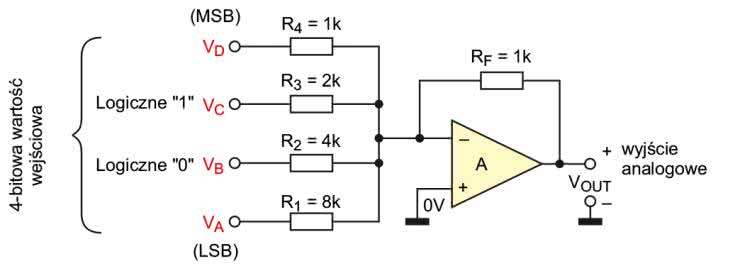

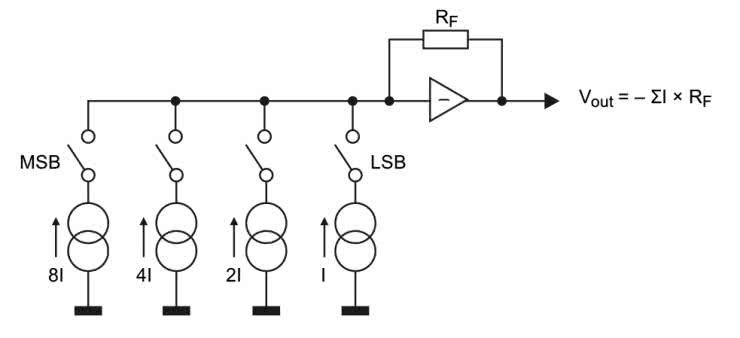

Omawianie konwerterów cyfrowo-analogowych zazwyczaj rozpoczyna się od najbardziej intuicyjnego przetwornika binarnie ważonego. Przykład 4-bitowej realizacji takiego układu pokazano na rysunku 1.

Przetwornik binarnie ważony to układ wzmacniacza sumującego napięcia na wejściu odwracającym. Można wykazać, że napięcie wyjściowe VOUT jest równe:

![]()

A podstawiając za RF, R1, R2, R3 i R4 wartości z rysunku 1, otrzymamy:

![]()

Jeżeli teraz przyjmiemy, że napięcia na wejściach VA…VD przyjmują tylko dwie wartości: 0 V (logiczne zero) lub na przykład +5 V (logiczna jedynka), to otrzymamy na wyjściu analogowym napięcie proporcjonalne do cyfrowego kodu wejściowego.

Opisana topologia może dobrze się sprawdzić w bardzo prostych przetwornikach o kilkubitowej rozdzielczości, natomiast jest zupełnie bezużyteczna w przypadku wielobitowych konstrukcji, koniecznych w wysokiej jakości przetwornikach sygnału audio. W przypadku układu z rysunku 1 rezystancja R1, odpowiadająca najmniej znaczącemu bitowi (LSB), ma wartość 1 kΩ, a R4 – odpowiadająca najbardziej znaczącemu bitowi – ma wartość 8 kΩ, czyli R4=(24)·R1. Przyjmijmy, że mamy taki przetwornik o rozdzielczości 16 bitów, potrzebujemy zatem układu z szesnastoma opornikami. Jeżeli – tak jak na rysunku 1 – oporność R1 będzie równa 1 kΩ, to wartość R16 wyniesie: R16=(216)·R1, czyli: 1 kΩ·65536=65,536 MΩ.

Bardzo trudne jest wykonanie układu dokładnych rezystorów o tak dużej rozpiętości wartości rezystancji, szczególnie w układzie scalonym, który – dla rynku konsumenckiego – musi być stosunkowo tani. Dodatkowo taki układ rezystorów nie będzie stabilny temperaturowo i wraz ze zmianami warunków otoczenia będzie następowała zmiana funkcji przetwarzania, powodująca wprowadzanie błędów do charakterystyki konwertera. Topologia ważonego przetwornika cyfrowo-analogowego, pokazanego na rysunku 1, jest zatem bezużyteczna w wielobitowych układach audio.

Przetwornik o topologii R2-R

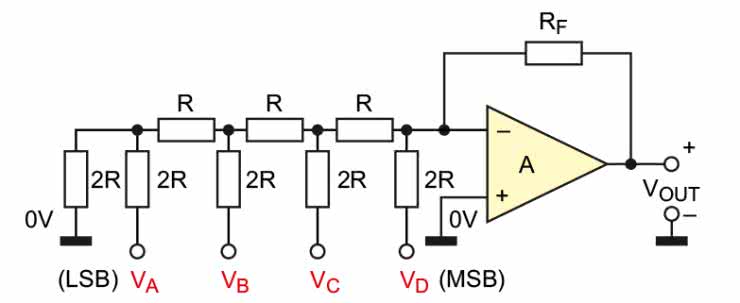

Wspomnianej wady układu binarnego ważonego pozbawiona jest topologia drabinki rezystorowej typu R2-R, pokazana na rysunku 2.

Sieć drabinki rezystancyjnej R-2R to długi ciąg równolegle i szeregowo połączonych rezystorów o wartościach R i 2·R. Taki układ jest dużo łatwiej wykonać w technologii scalonej. Sieć działa jako połączone ze sobą, kolejne dzielniki napięcia. Napięcie wyjściowe VOUT zależy wyłącznie od oddziaływania ze sobą napięć wejściowych VA, VB. VC...Vn, a nie bezpośrednio od wartości rezystancji rezystorów drabinki. Napięcia wejściowe mogą zatem przybierać wartości 0 V dla stanu logicznego niskiego lub VIN – dla stanu wysokiego. VIN jest napięciem referencyjnym, nazywanym najczęściej VREF. Analizując sieć rezystorów można wykazać, że napięcie wyjściowe jest równe:

![]()

gdzie: n oznacza liczbę wejść cyfrowych przetwornika, czyli jego rozdzielczość bitowa

Rozdzielczość napięciowa przetwornika, czyli zmiana napięcia na wyjściu spowodowana zmianą kodu wejściowego na pozycji najmniej znaczącego bitu, wynosi:

![]()

gdzie VIN jest tożsame z napięciem odniesienia VREF.

Przykładowo: dla przetwornika 16-bitowego z napięciem odniesienia równym 5 V rozdzielczość jest równa 5/(216)=5/65536=92 μV. To pokazuje, że nawet przy 16-bitowej rozdzielczości mamy do czynienia z bardzo małymi poziomami, które łatwo jest zdegradować szumem i innymi zakłóceniami toru audio, a tym samym... ograniczyć jego rzeczywistą rozdzielczość.

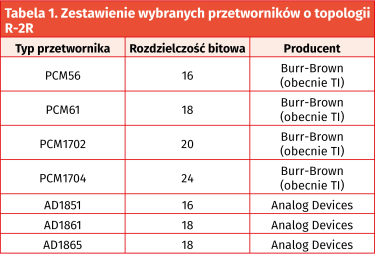

Topologia R-2R jest szeroko stosowana w scalonych przetwornikach audio przeznaczonych dla rynku konsumenckiego. W tabeli 1 pokazano zestawienie wybranych, wielobitowych przetworników audio, opartych na topologii R-2R.

Wszystkie te przetworniki (za wyjątkiem AD1865) mogą konwertować jeden kanał audio, zatem do budowy przetwornika stereofonicznego potrzebne są 2 układy.

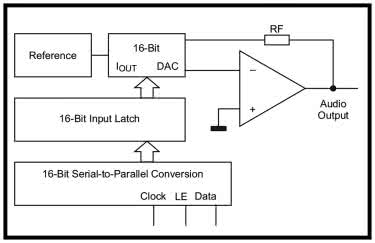

Na rysunku 3 pokazano schemat blokowy przetwornika PCM56 firmy Burr Brown. Dane audio, przesyłane szeregowo przez wejścia Clock, LE i Data, są zatrzaskiwane w 16-bitowym rejestrze wejściowym. Po skompletowaniu całego, 16-bitowego słowa dane są przekazywane na przetwornik DAC typu R-2R. Blok Reference dostarcza dokładne i stabilne napięcie referencyjne.

Jak już wspomniałem, możliwe jest wykonanie scalonego przetwornika R-2R wysokiej klasy, jednak wymaga to zaawansowanej technologii łączącej krzemową strukturę układu z rezystorami cienkowarstwowymi. Aby uzyskać dużą dokładność rezystancji, poszczególne elementy w sieci R-2R układu są w procesie produkcyjnym dodatkowo kalibrowane (trymowane) za pomocą lasera. Przykładem zastosowania bardzo wyrafinowanej technologii jest układ PCM1704, który według danych katalogowych uzyskuje rozdzielczość 24-bitową, może próbkować dane z maksymalną częstotliwością fS=96 kHz i charakteryzuje się parametrem THD na poziomie 0,0008%. Zdecydowana większość przetworników wielobitowych cieszy się bardzo dobrą opinią wśród osób ceniących dźwięk na najwyższym poziomie. Jednak mimo tych bardzo dobrych parametrów i opinii, w większości przypadków nie są one produkowane i stosowane w nowych konstrukcjach, a ceny ze starych zapasów osiągają zawrotne wartości. Przyczyną takiego stanu rzeczy jest zapewne bardzo kłopotliwy i – co za tym idzie – kosztowny proces produkcyjny. Ograniczenie stanowi rozdzielczość bitowa, która – za wyjątkiem układów PCM1704 i PCM1702 – wynosi 16 lub 18 bitów, a dodatkowym problemem jest niższa częstotliwość próbkowania. Nie bez znaczenia jest także fakt, że do układów stereofonicznych potrzebujemy 2 przetworników. Ale i to nie wszystko. Kompletne przetworniki potrzebują do pracy trzeciego układu: filtra cyfrowego. Realizuje on proces nadpróbkowania w interpolatorze cyfrowym i cyfrowej filtracji dolnoprzepustowej. Gwoli ścisłości należy wspomnieć, że wśród amatorów DIY na całym świecie istnieje cała rzesza entuzjastów rozwiązania nazywanego NOS DAC, czyli No OverSampling DAC. Przetworniki budowane według tej idei nie mają filtra cyfrowego realizującego nadpróbkowanie, a sygnał PCM jest podawany bezpośrednio na wejście przetworników DAC. Nie stosuje się też dolnoprzepustowych filtrów rekonstruujących. Brak filtra cyfrowego w strukturze przetwornika powoduje, że konieczne są dodatkowe układy logiczne, które dostosowują format I²S do formatu wejściowego przetworników (wymagającego podanie sygnałów Clock, LE i Data).

Brak nadpróbkowania i analogowej rekonstrukcji sygnału wyjściowego ma powodować, że dźwięk po konwersji będzie inny, niż w klasycznych rozwiązaniach – a wg opinii wielu lepszy lub nawet dużo lepszy. Ponieważ jest to artykuł techniczny, nie będziemy nad tym dyskutować – skutki tak wykonanej konwersji możemy zobaczyć, analizując pierwszą część niniejszego opracowania.

Przetwornik DEM (Dynamic Element Matching)

Jak już wspomniałem, choć sieci drabinkowe R2-R pozwalają na zbudowanie konwertera DAC o wysokiej jakości, to ich dobre parametry są okupione trudnościami technologicznymi i – w konsekwencji – relatywnie wysoka ceną. Dlatego szukano przed laty tańszych alternatyw, pozwalających na uzyskanie równie dobrych parametrów, ale mniejszym kosztem.

W 1976 roku Rudy van de Plassche, młody inżynier ds. badań i rozwoju pracujący w Laboratoriach Badawczych Philipsa, publikuje pracę zatytułowaną „Dynamic Element Matching for High-Accuracy Monolithic D/A Converters”, w której proponuje nowatorski, prosty i dokładny konwerter cyfrowo-analogowy o nazwie „Dynamic Element Matching” w skrócie DEM. Ta metoda ta nie wymagała trymowania laserowego rezystorów w trakcie produkcji i mogła być produkowana masowo przy użyciu ówcześnie dostępnej, standardowej technologii bipolarnej.

Idea działania jest podobna do ważonego przetwornika binarnego, pokazanego na rysunku 1. Zamiast rezystorów stosuje się jednak źródła prądowe (rysunek 4). Jeżeli bitowi MSB (najstarszemu) przypiszemy źródło w wydajności prądowej I, to kolejnej wadze odpowiadać będzie źródło o wydajności 2/I – i tak dalej, aż do najmłodszego bitu. Oczywiście otrzymamy tu również bardzo dużą rozpiętość wartości prądu, który musi być bardzo precyzyjnie podzielony.

Jeżeli najstarszemu bitowi przetwornika 16-bitowego przypiszemy prąd 2 mA, to w przypadku najmłodszego bitu będzie to natężenie zaledwie 61 nA! Tu musi się pojawić pytanie: jak wygenerować dokładne prądy binarnie ważone (malejące w stosunku 1:2) dla wszystkich naszych bitów danych? Najlepiej dzieląc każdy następny prąd dokładnie na pół. No dobrze, ale jak to zrobić, skoro wiemy, że każdy realny element aktywny lub pasywny wprowadzi jakiś błąd i ten błąd będzie się sumować w każdym kolejnym stopniu podziału?

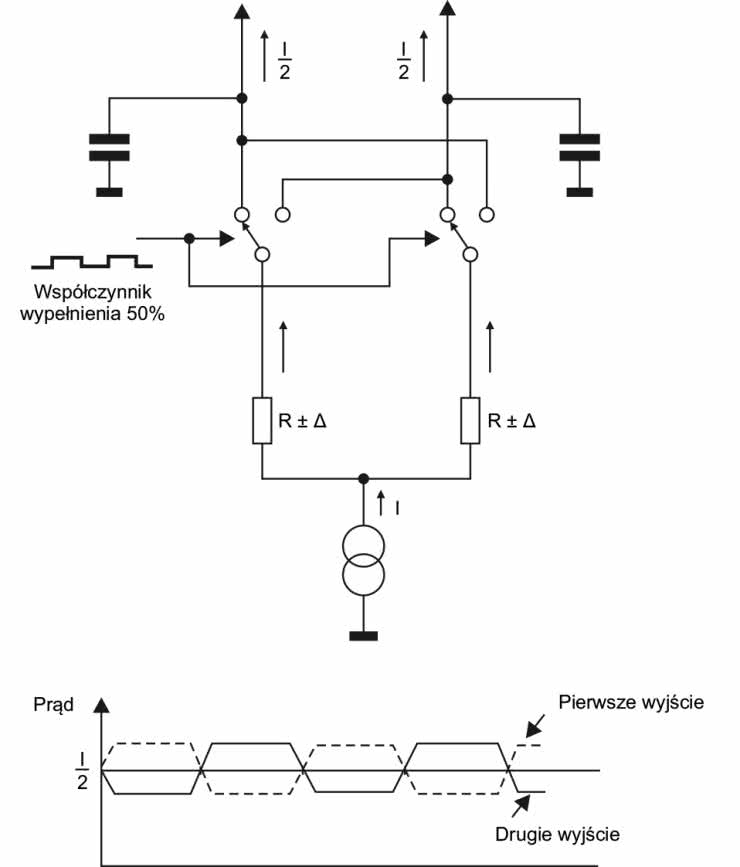

Rudy van de Plassche zaproponował sprytne rozwiązanie problemu. Rysunek 5 pokazuje źródło prądowe zasilające parę nominalnie równych rezystorów. Jednak ich rezystancje nie będą idealnie równe ze względu na tolerancje produkcyjne i dryft temperaturowy. Dlatego prąd jest tylko w przybliżeniu dzielony po połowie. Para przełączników umieszcza każdy rezystor szeregowo z każdym wyjściem. Średni prąd na każdym wyjściu będzie wtedy identyczny – pod warunkiem, że współczynnik wypełnienia sygnału sterującego przełącznikami wyniesie dokładnie 50%. A to jest już łatwo osiągalne w układzie dzielenia częstotliwości przez dwa. Kryterium dokładności zostało przeniesione z wartości rezystancji do dziedziny czasu, w której wysoka dokładność łatwa do osiągnięcia. Uśrednianie prądu jest wykonywane przez parę kondensatorów, które nie muszą być wysokiej jakości.

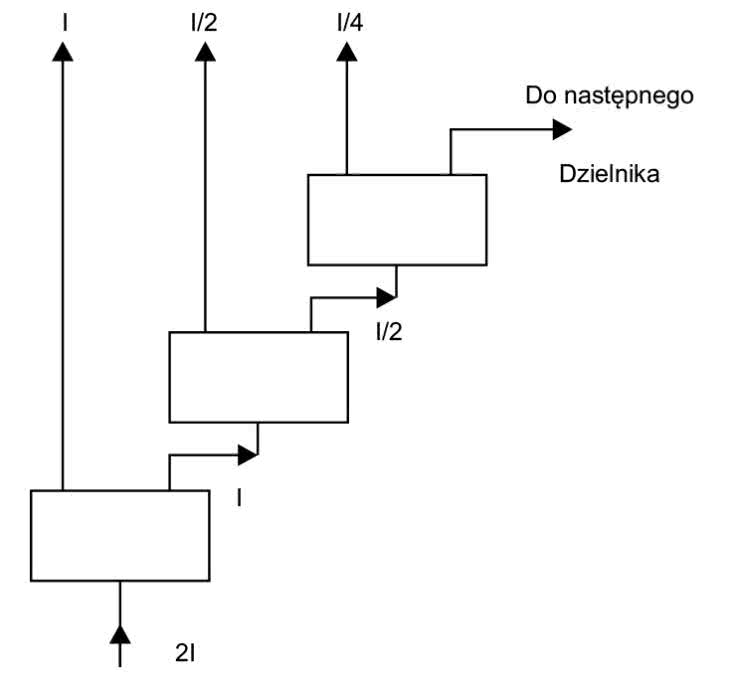

Przyjmijmy, że prąd I na rysunku 5 ma wartość 4 mA. Na wyjściach dzielnika mamy 2 prądy po 2 mA. Jeżeli teraz jedno z wyjść będzie źródłem prądu dla kolejnego układu dzielnika, to otrzymamy w konsekwencji prądy o dokładnych wartościach: 4 mA, 2 mA i 1 mA. Łącząc kaskadowo szereg dzielników otrzymujemy ciąg dokładnych prądów binarnie ważonych – patrz rysunek 6.

Ważną cechą układu DEM jest fakt, że dokładność dzielenia prądów nie zależy od częstotliwości, a tylko od dokładności (czasowej) współczynnika wypełnienia. W praktyce wybór częstotliwości DEM ma jednak pewne znaczenie. Panuje pogląd, że powinna ona być większa od częstotliwości próbkowania i stanowić jej wielokrotność. W literaturze można znaleźć dokładne analizy wpływu częstotliwości taktującej DEM na zniekształcenia THD i szumy konwersji. Wynika z nich, że nie ma idealnego rozwiązania i potrzebny okazuje się wyważony kompromis.

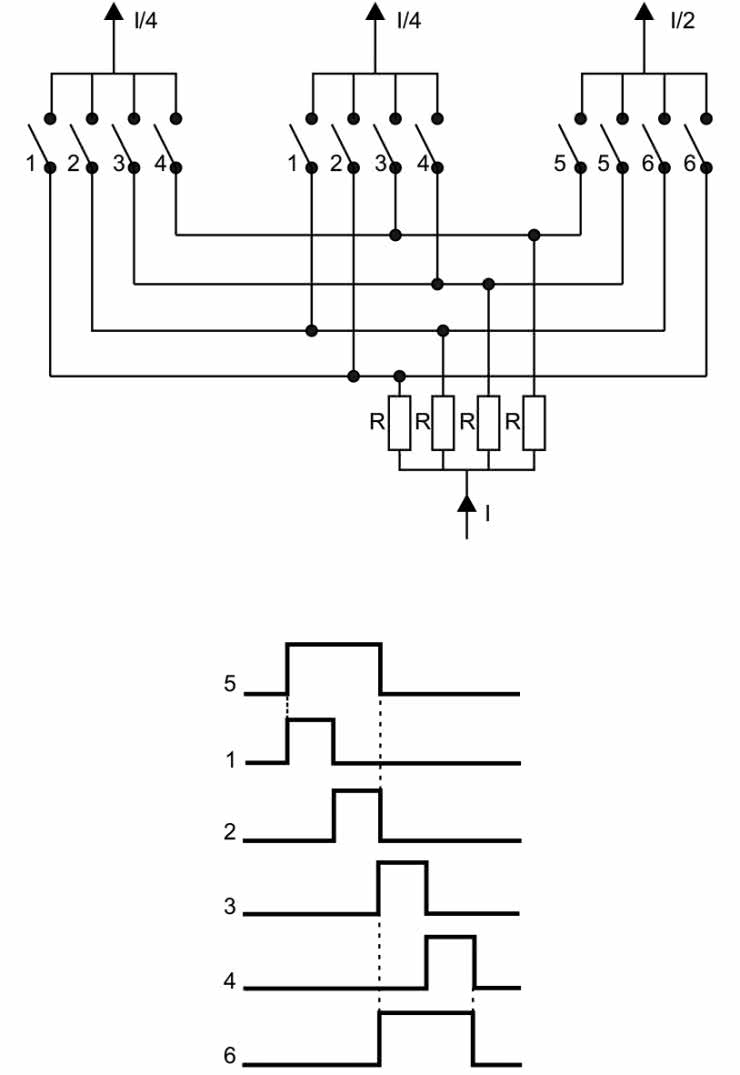

W praktyce można uzyskać redukcję liczby etapów dzielenia, stosując bardziej złożony układ przełączania. Generuje on prądy o stosunku 1:1:2, dzieląc prąd na cztery ścieżki, a następnie dwie z nich trafiają do jednego wyjścia, jak pokazano na rysunku 7.

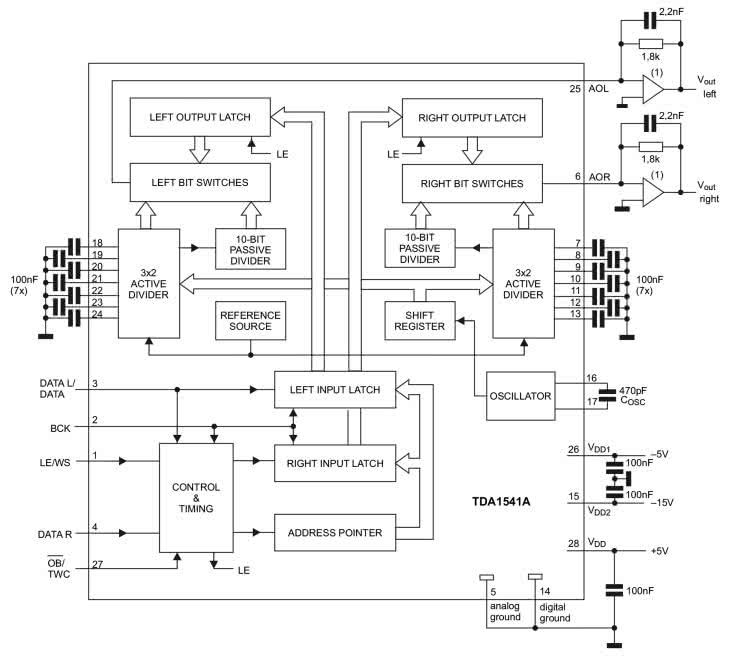

Topologia DEM jest używana w 14-bitowym przetworniku TDA1540 i kultowych już, 16-bitowych, stereofonicznych przetwornikach TDA1541 i TDA1541A, produkowanych przez Philipsa w czasach, gdy firma ta zajmowała się jeszcze przemysłem półprzewodnikowym. TDA1541A o najlepszej gradacji produkcyjnej osiąga dzisiaj zawrotne ceny i jest przez wielu postrzegany jako najlepszy przetwornik w historii. My skupimy się jednak na parametrach technicznych, pomijając jego legendę i niemierzalne, subiektywne właściwości brzmieniowe. Ten stary układ ma – z dzisiejszego punktu widzenia – dość przeciętne parametry. Zniekształcenia harmoniczne to typowe 0,0018%, THD+N wynosi 0,79%, a nieliniowość przetwarzania to ±1 LSB. Schemat blokowy układu został pokazany na rysunku 8.

Na schemacie uwzględniono zewnętrzny konwerter prąd/napięcie, zrealizowany na bazie wzmacniacza operacyjnego NE5534. Układ dzielnika w każdym kanale podzielony jest na 6-bitowy, aktywny dzielnik (dzielący prądy od największego, czyli od bitu MSB) i 10-bitowy, pasywny dzielnik, obsługujący 10 najmłodszych bitów.

Rudy van de Plassche dokładnie opisał działanie zarówno dzielnika aktywnego, jak i pasywnego. Działanie filtra aktywnego jest oparte na zasadzie dzielenia prądów w stosunku 1:1:2 (rysunek 7).

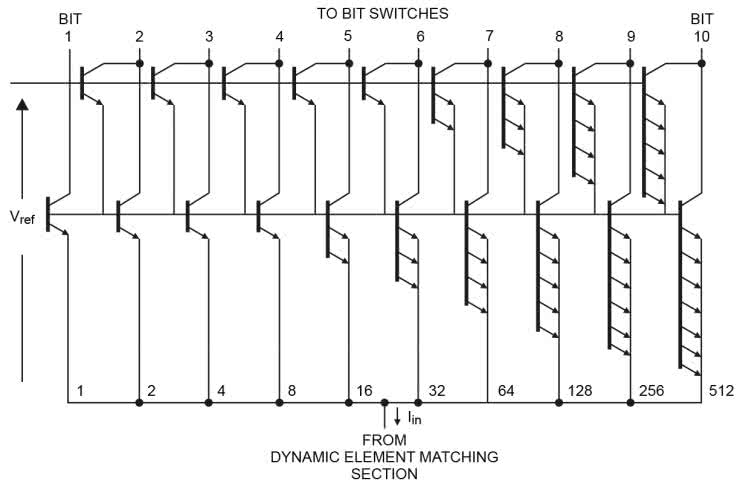

Rysunek 9 prezentuje podstawową koncepcję pasywnego dzielnika prądu, opartą na skalowaniu emitera tranzystorów. Ta koncepcja jest używana do generowania pozostałych dziesięciu, najmniej znaczących bitów. Układ składa się tylko z 1024 tranzystorów Darlingtona i nie wymaga żadnej procedury trymowania lub regulacji, działa ponadto w szerokim zakresie temperatur pracy. Ponieważ wszystkie tranzystory znajdują się na wspólnym podłożu krzemowym układu scalonego, to mają takie samo napięcie baza-emiter i równe prądy kolektora. W ten sposób prąd wejściowy jest dzielony na 1024 równe prądy o wartości jednego LSB każdy. Prąd wyjściowy bitu MSB tego pasywnego dzielnika jest konstruowany przez kombinację 512 prądów kolektora.

Działanie przetwornik Philips TDA1543 opiera się na podziale prądów tylko za pomocą dzielników pasywnych, dla wszystkich bitów (tj. bez użycia DEM). Ma on istotnie słabsze parametry i w założeniu był przeznaczony dla popularnych odtwarzaczy CD. Prądy z dzielników są włączane i wyłączane zależnie od wartości słowa wejściowego przez analogowe klucze. Ich rezystancja w stanie załączenia może wpływać na wartość prądu, szczególnie w przypadku większych prądów odpowiadających starszym bitom. Aby temu zapobiec, stosuje się klucze o większej szerokości ścieżki półprzewodnikowej w torach obsługujących prądy o wyższych natężeniach.

Przetwornik z integratorem

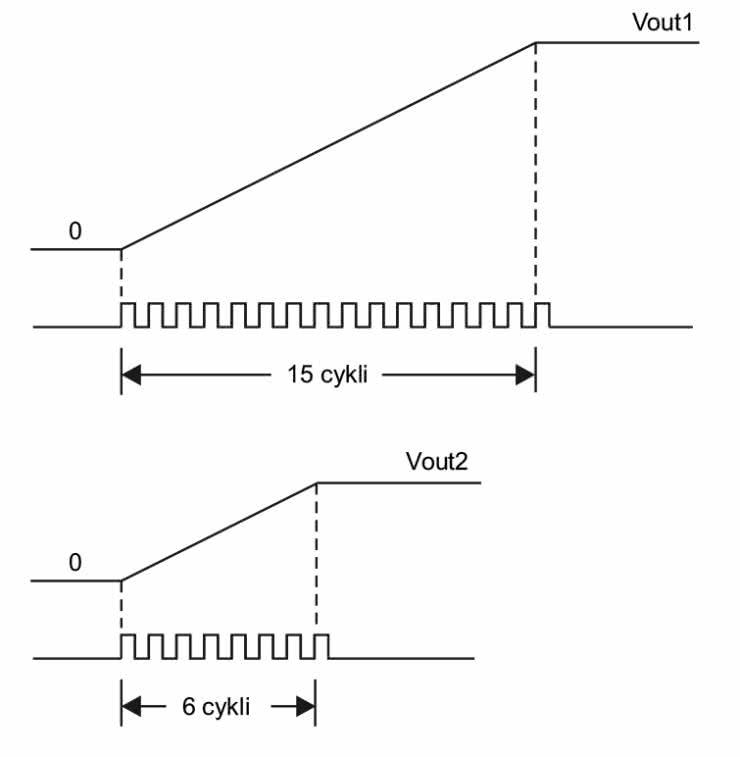

Ogólna koncepcja działania takiego przetwornika jest stosunkowo prosta. Napięcie na wyjściu jest w istocie napięciem na kondensatorze ładowanym przez źródło prądowe od zera, przez czas proporcjonalny do wartości danej wejściowej (próbki). Jeżeli dana wejściowa ma małą wartość, to czas ładowania jest krótki i kondensator naładuje się do niskiego napięcia, natomiast jeśli wartość wejściowa jest większa, to czas ładowania jest dłuższy, zaś cały proces prowadzi do zgromadzenia wyższego ładunku.

Załóżmy, że mamy przetwornik czterobitowy. Na jego wejściu mogą się pojawiać wartości od 0 do 15. Na rysunku 10 pokazano dwa przypadki. W pierwszym z nich kondensator jest ładowany przez 15 cykli (dla danej wejściowej równej 15). Pojemność naładuje się do napięcia Vout1. Drugi przypadek pokazuje ładowanie w czasie tylko sześciu cykli, przez co kondensator naładuje się do wyraźnie niższego napięcia, odpowiadającego wartości wejściowej równej 6.

Niestety, w praktyce nie jest to takie proste. Załóżmy, że chcemy zbudować wysokiej jakości przetwornik 16-bitowy. Nasze źródło prądowe musi mieć bardzo małą wydajność prądową, a liczba cykli zliczania musi być duża, żeby uzyskać wymaganą rozdzielczość. Dla dużych wartości wejściowych naładowanie kondensatora może trwać zbyt długo – a powinno przecież nastąpić w czasie krótszym niż okres przebiegu określającego częstotliwość próbkowania. Dlatego zegar taktujący konwersję musiałby mieć częstotliwość 65536 razy większą od częstotliwości próbkowania, czyli… około 3 GHz. To oczywiście powodowałoby bardzo duże problemy technologiczne i w praktyce taka implementacja nie była możliwa.

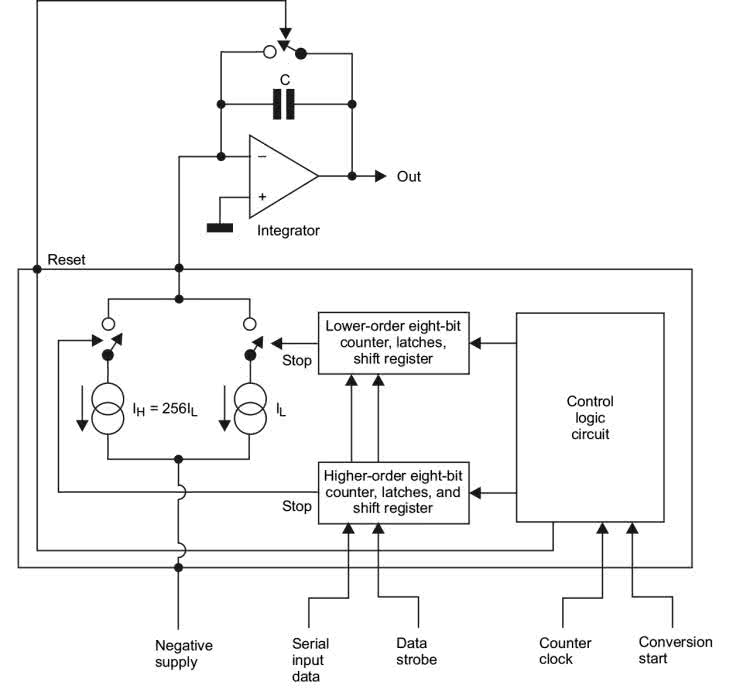

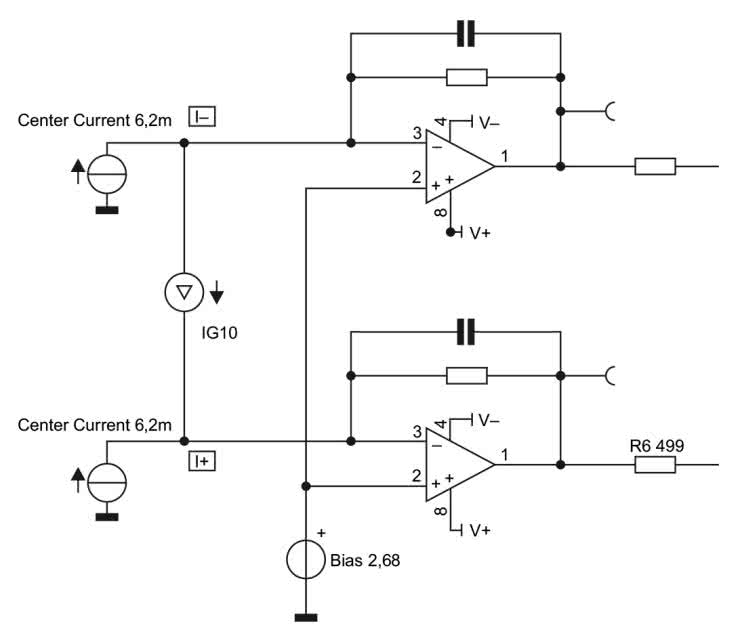

I znów – tak jak w poprzednich implementacjach konwerterów R2R i DEM – trzeba było wymyślić jakiś sposób na pokonanie problemu. Podzielono więc 16-bitowe słowo wejściowe na osiem młodszych bitów i 8 starszych bitów. Pierwsze w z nich określają czas ładowania kondensatora małym prądem IL, a osiem starszych bitów – dużym prądem IH. Należy przy tym pamiętać, że wartość IH musi być dokładnie 256 razy większa od IL. Dokładność wielokrotności tych prądów wpływa znacząco na dokładność konwersji, ale – jak już wiemy – istnieją sposoby, by to zrobić naprawdę dokładnie. Na rysunku 11 pokazano uproszczony schemat blokowy przetwornika Sony CX-20017. Widoczne są źródła prądu wyższego i niższego rzędu (IH i IL) oraz powiązane z nimi obwody czasowe. Niezbędny integrator jest w tej implementacji układem zewnętrznym.

Przy takim rozwiązaniu zegar taktujący czas zliczania może mieć częstotliwość ok. 20 MHz w przypadku przetwornika o rozdzielczości 16 bitów i częstotliwości próbkowania 48 kHz. Maksymalny czas ładowania kondensatora wyniesie wtedy 12,8 μ – pozostaje zatem jeszcze 8 μs na pobranie kolejnej próbki i resetowanie układu, które polega głównie na rozładowaniu kondensatora.

Kondensator C zewnętrznego integratora musi mieć niski prąd upływu, a wzmacniacz operacyjny – możliwie najmniejszy prąd polaryzacji wejść. Najlepiej, gdyby był to wzmacniacz z wejściami JFET.

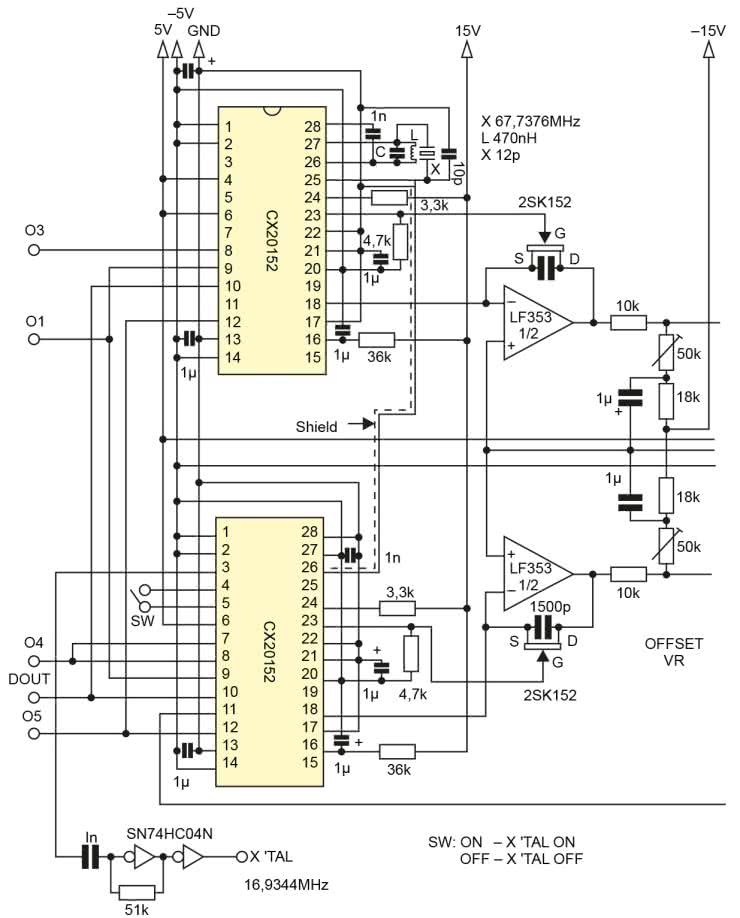

Z tych względów układ integratora jest montowany z zewnętrznych elementów, a nie wbudowany w strukturę przetwornika. Na rysunku 12 pokazano przykład fragmentu implementacji przetwornika CX 20152 firmy Sony z zewnętrznymi układami integratora.

Obecnie przetworniki wielobitowe nie są już produkowane, ale – co najważniejsze – nie są nawet dalej rozwijane. Układy te okazały się bowiem trudne do scalenia i drogie w produkcji. Wraz z rozwojem cyfrowej techniki audio przestały spełniać oczekiwania producentów sprzętu. Maksymalna użyteczna rozdzielczość do 20 bitów i częstotliwość próbkowania do 48 kHz okazały się niewystarczające. Do zbudowania kompletnego przetwornika potrzebny był ponadto dodatkowy układ filtra realizującego funkcje nadpróbkowania, co również zwiększało koszty i komplikowało układ. Trzeba pamiętać, że przetworniki DAC są obecnie stosowane na bardzo dużą skalę w wielu urządzeniach konsumenckich: w telefonach komórkowych, laptopach, telewizorach itp. Tam liczą się dobre parametry, ale też małe rozmiary, niskie napięcie zasilania, niewielki pobór mocy itd. Przetworniki wielobitowe są bardzo cenione przez część środowiska audiofilskiego, jednak to chyba za mało, żeby ktoś podjął się produkcji i być może nawet rozwijania skomplikowanego technologicznie układu. Przetworniki wielobitowe DAC zostały bezpowrotnie zastąpione przez konstrukcje z modulatorami delta-sigma.

Przetworniki z modulatorami delta-sigma

Modulator delta-sigma może pracować zarówno w przetwornikach analogowo-cyfrowych, jak i cyfrowo-analogowych. Topologia i koncepcja działania są takie same, ale trochę inaczej pracują pewne bloki modulatora. Najłatwiej będzie wyjaśnić działanie modulatora w konwersji analogowo-cyfrowej.

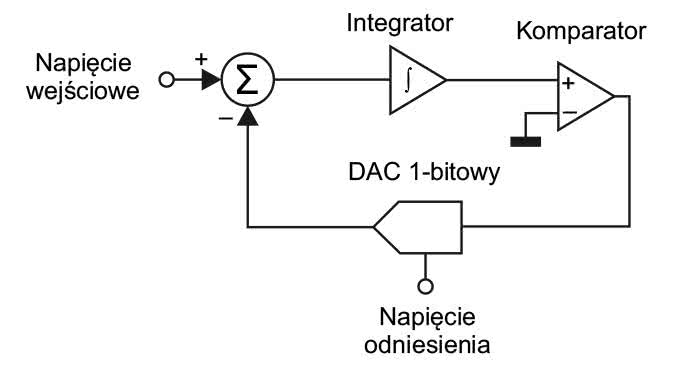

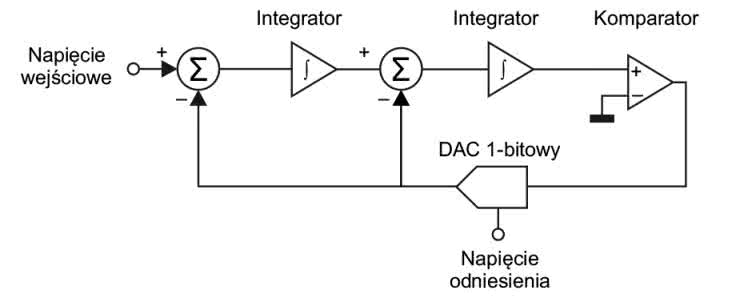

Na rysunku 13 pokazano modulator delta sigma pierwszego rzędu. W praktyce stosuje się bardziej rozbudowane modulatory wyższych rzędów, ale najłatwiej jest wytłumaczyć działanie na najprostszym przykładzie.

Modulator jest zbudowany z:

- sumatora,

- integratora,

- komparatora sterującego wejściem 1-bitowego przetwornika DAC,

- 1-bitowego konwertera DAC.

Modulator jest taktowany zegarem, który wyznacza kolejne etapy pracy. Sumator sumuje napięcie wejściowe z napięciem sprzężenia zwrotnego, które trafia na sumator z wyjścia 1-bitowego przetwornika DAC.

Integrator dodaje napięcie z wyjścia sumatora do napięcia z poprzedniego kroku integracji. Tak wytworzone napięcie jest pamiętane w integratorze. Jeżeli aktualny potencjał na wyjściu integratora jest większy lub równy zero, to na wyjściu komparatora panuje stan wysoki, który następnie trafia na wejście 1-bitowego przetwornika DAC. Jeżeli na wejściu tego ostatniego także panuje stan wysoki, to na wyjściu DAC pojawia się napięcie odniesienia VREF – w przeciwnym przypadku na wyjściu DAC panuje napięcie zerowe.

Jak już wiemy, napięcie z wyjścia DAC jest napięciem sprzężenia zwrotnego. Modulator nie konwertuje zatem bezwzględnej wartości napięcia na wejściu, ale jego zmiany względem poprzedniego cyklu konwersji.

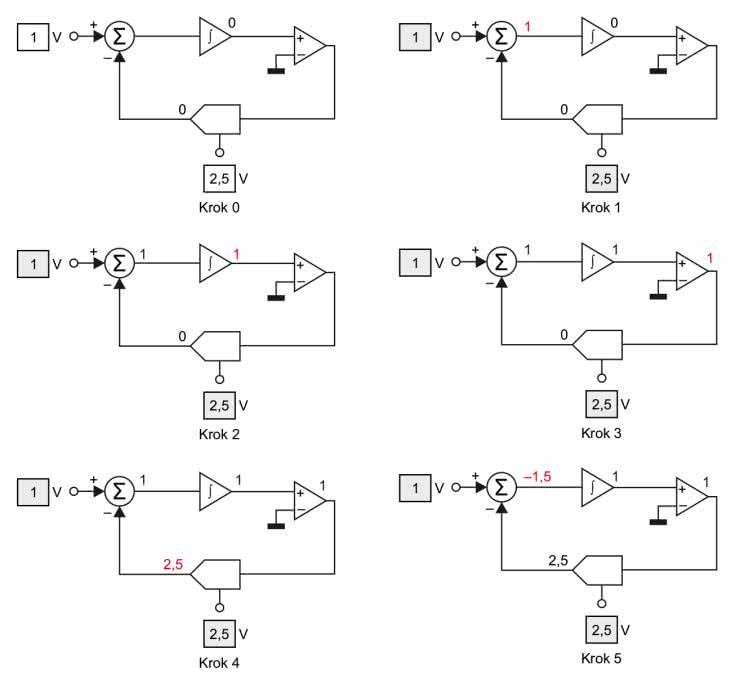

Na rysunku 14 pokazano kolejne działania modulatora delta-sigma, pracującego jako przetwornik analogowo-cyfrowy. W stanie początkowym (krok „0”) na wejście trafia napięcie +1 V, napięcie na wyjściu DAC jest równe zeru, podobnie jak wartość napięcia z poprzedniej integracji. Napięcie odniesienia wynosi +2,5 V. W pierwszym kroku napięcie wejściowe jest sumowane z zerowym napięciem sprzężenia zwrotnego i na wyjściu sumatora pojawia się napięcie +1 V. W drugim kroku przechodzi ono na wyjście integratora. Komparator wykrywa napięcie +1 V na wejściu i wystawia stan wysoki na wyjściu (krok „3”). Ten zaś, trafiając na wejście 1-bitowego DAC powoduje, że na wyjściu przetwornika pojawi się napięcie odniesienia +2,5 V (krok „4”). W kroku „5” od napięcia wejściowego +1 V zostanie w sumatorze odjęte +2,5 V napięcia odniesienia, zatem na wejściu integratora pojawi się napięcie –1,5 V. W kolejnym kroku – niepokazanym już na rysunku – integrator doda napięcie +1 V (z poprzedniej integracji) do napięcia –1,5 V (z wyjścia sumatora) i na wyjściu integratora pojawi się stan niski.

Na wyjściu modulatora pojawiają się zatem wartości opisujące zmianę wartości wejściowej, a nie sama wartość wejściowa jako taka.

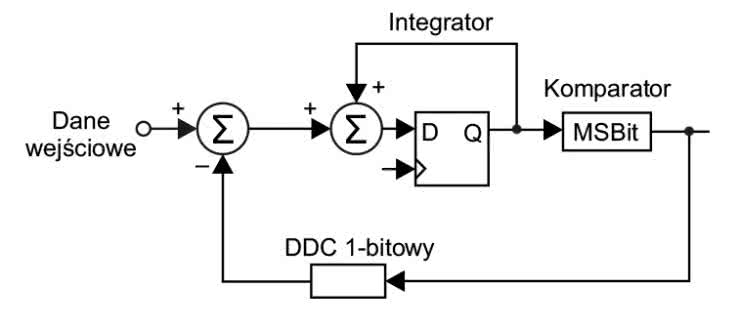

Konwerter cyfrowo-analogowy typu delta-sigma został schematycznie pokazany na rysunku 15. Równoległe dane wejściowe są podawane na sumator, gdzie od ich wartości odejmowana jest wartość z pętli sprzężenia zwrotnego. Następnie są one sumowane w integratorze z danymi z poprzedniej konwersji. Wyjście integratora trafia na komparator MSB. Jeżeli najstarszy bit danych jest jedynką, to na wyjściu komparatora (i jednocześnie modulatora) panuje stan wysoki, zaś w przypadku bitu zerowego – stan niski. Dalej dane z wyjścia komparatora są podawane na przetwornik DDC, który kompletuje z nadchodzących bitów wyjścia komparatora słowo wielobitowe – odejmowane następnie w sumatorze. W ten sposób cały cykl powtarza się przez cały czas pracy przetwornika.

Dane wejściowe mają zazwyczaj długość kilku bitów i są wydzielane ze słowa o długości próbki (na przykład 16-bitowego) przez układ filtrów.

Pokazane na rysunkach 13 i 15 układy są modulatorami pierwszego rzędu. Można uzyskać lepsze parametry konwersji stosując modulatory wyższych rzędów. Przykład idei modulatora drugiego rzędu pokazano na rysunku 16.

Modulatory wyższych rzędów, z powodu problemów z fazą sygnałów, mogą być niestabilne i potrzebują dodatkowych układów korekcji fazy.

Jak już wiemy, konwersja cyfrowo-analogowa charakteryzuje się błędem (szumem) kwantyzacji, zależnym od długości słowa konwersji. W modulatorach delta-sigma mamy konwertery o małej długości słowa (od jednego do kilku bitów). Taka konwersja charakteryzuje się dużym poziomem błędu kwantyzacji. Dodatkowo sama modulacja delta-sigma niesie ze sobą błąd modulacji, bo strumień wyjściowy jest zawsze pewnym przybliżeniem sygnału wejściowego. Ten błąd ogranicza się przez stosowanie modulatorów wyższego rzędu i większej długości słowa wejściowego (w przypadku DAC). Aby uzyskać dobre parametry sygnału wyjściowego, przetworniki cyfrowo-analogowe z modulatorami delta-sigma muszą mieć wbudowane filtry interpolatora, wielokrotnie nadpróbkujące dane wejściowe, a sygnał wyjściowy musi podlegać kształtowaniu szumu (noise shaping). Jak wspomniano we wcześniejszym artykule z tej serii, kształtowanie szumu nie usuwa szumów konwersji z sygnału, tylko przesuwa ich energię poza pasmo użyteczne (słyszalne). Potem taki sygnał jest poddawany filtrowaniu dolnoprzepustowemu i szum jest usuwany z sygnału użytecznego.

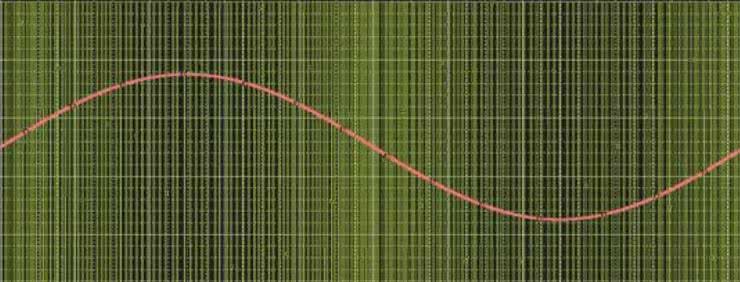

Na wyjściu modulatora delta-sigma dostajemy zmodulowany przebieg o zmiennej gęstości zer i jedynek, reprezentujący analogowy sygnał – doskonale widać to na rysunku 17.

Przebieg ten przypomina modulację PWM, ale modulator delta-sigma daje lepszą jakość konwersji w porównaniu do klasycznego sygnału PWM. Aby z takiego ciągu impulsów uzyskać analogowy sygnał, należy go odfiltrować dolnoprzepustowo.

Przetworniki z modulatorami delta-sigma prawie całkowicie wyparły rozwiązania wielobitowe. Swój sukces zawdzięczają dużej łatwości implementacji w strukturach scalonych. Mimo że praktyczne układy modulatorów są o wiele bardziej skomplikowane, to mają one charakter układów cyfrowych, a niezbędne bloki analogowe są dzięki temu stosunkowo proste. Okazało się, że nawet konieczność wbudowania w układ kompletnych, zaawansowanych filtrów decymatora (nadpróbkujących dane wejściowe) jest tańsze i łatwiejsze, niż na przykład stosowanie trymowanych laserowo drabinek R-2R.

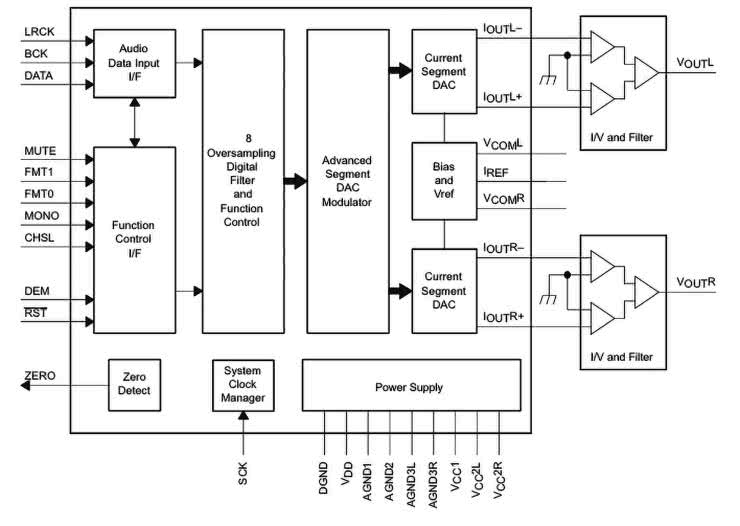

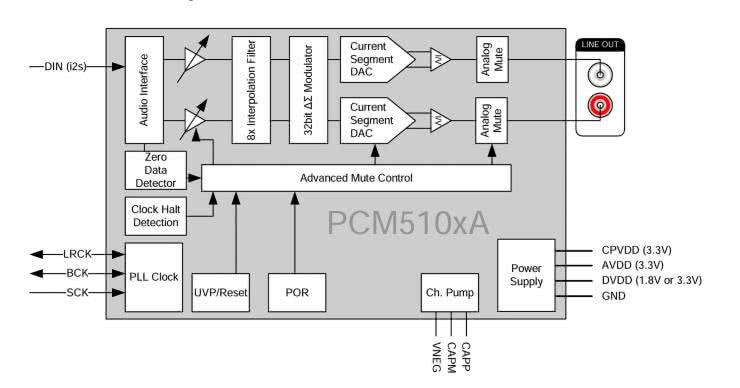

Dzisiejsze konwertery DAC typu delta-sigma potrafią osiągać parametry lepsze od przetworników wielobitowych. Jako przykład weźmiemy bardzo dobry i stosunkowo tani przetwornik PCM1794A firmy Burr Brown (obecnie Texas Instruments).

Producent chwali się imponującymi parametrami układu: zakres dynamiki to 132 dB dla najlepszych warunków pomiarowych: sygnału wyjściowego 9 Vrms i konfiguracji mono (DAC konwertuje tylko jeden kanał). W gorszych warunkach dynamika wynosi 129 dB w konfiguracji stereo i przy sygnale 4,5 V (RMS). Zniekształcenia harmoniczne z szumem (THD+N) wynoszą 0,0004%. Przetwornik ma rozdzielczość 24 bitów i może pracować z częstotliwościami próbkowania od 10 kHz do 200 kHz. PCM1794A zapewnia zbalansowane wyjścia prądowe. Różnicowy sygnał wyjściowy ma wartość 7,8 mA (pk-pk).

Na rysunku 18 pokazano schemat blokowy przetwornika. Przed konwerterem DAC umieszczono blok filtra 8-krotnego nadpróbkowania.

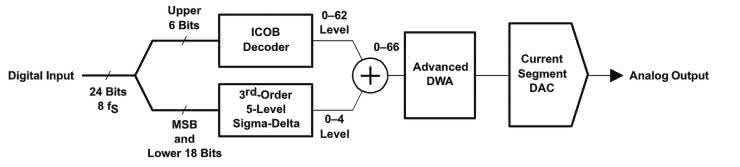

Nadpróbkowanie jest elementem niezbędnym dla prawidłowego działania funkcji kształtowania szumów kwantyzacji modulacji delta-sigma. Widoczny na schemacie blok o nazwie Advanced Segment DAC Modulator został pokazany na rysunku 19.

Cyfrowe dane wejściowe o długości 24 bitów i częstotliwości próbkowania 8·fS z wyjścia filtra oversamplingu są – za pomocą filtra cyfrowego – rozdzielane na sześć najbardziej znaczących bitów (MSB) i 18 bitów pozostałych. MSB są konwertowane na odwrócony, komplementarny kod binarny offsetowy (ICOB). 18 mniej znaczących bitów, łącznie z najstarszym bitem MSB, jest przetwarzanych przez pięciopoziomowy modulator delta-sigma trzeciego rzędu, domyślnie działający z częstotliwością 64·fs. Grupy danych przetwarzane w konwerterze ICOB i modulatorze delta-sigma trzeciego rzędu są sumowane (w celu utworzenia kodu cyfrowego) do 66 poziomów, a następnie przetwarzane przez uśrednianie ważone danymi (DWA) w celu zmniejszenia szumu wytwarzanego przez niedopasowanie elementów. Dane do 66 poziomów z DWA są konwertowane na wyjście analogowe w sekcji przetwornika różnicowo-prądowego.

Tyle – dość ogólnych – informacji podaje producent w danych technicznych. Niestety informacje na temat szczegółów działania przetworników z modulatorami delta-sigma jest bardzo mało – na przykład w przypadku TDA1541 można sobie tylko pomarzyć o szerszym opisie. Jest to trend widoczny nie tylko w dokumentacjach przetworników DAC, ale ogólnie większości współczesnych elementów i układów elektronicznych. Brak szczegółów działania, niekompletne dokumentacje czy niedostępne instrukcje serwisowe (w przypadku gotowych urządzeń) to już norma. W konsekwencji często nie wiemy czy i jakiego modulatora użyto w przetworniku.

PCM1794A to oczywiście jeden z przykładów bardzo dobrego przetwornika z modulatorem delta-sigma. Na rynku jest kilku producentów oferujących konwertery o podobnych lub nawet lepszych parametrach.

Układy ESS Sabre DAC są wysoko cenione wśród audiofilów ze względu na wyjątkową jakość dźwięku i możliwości reprodukcji audio o wysokiej rozdzielczości. Na przykład układy ES9038PRO są jednymi z liderów rynku przetworników o najwyższych parametrach technicznych i odsłuchowych. Charakteryzują się imponującym zakresem dynamiki rzędu 138 dB (tryb MONO) i bardzo niskimi całkowitymi zniekształceniami harmonicznymi (THD+N=–122 dB), co pozycjonuje je jako silnych graczy w dziedzinie konwersji cyfrowo-analogowej. Układy te nie tylko obsługują wysokie częstotliwości próbkowania, ale także zapewniają zaawansowane opcje filtrowania cyfrowego, dając użytkownikom elastyczność w dostosowywaniu wrażeń słuchowych.

Układ firmy AKM (Asahi Kasei Microdevices) AK4499EQ również słynie z bardzo dobrych parametrów (zakres dynamiki: 138 dB, THD+N: –124 dB) i wysokiej jakości dźwięku, stając się dobrą opcją dla audiofilów poszukujących dźwięku o wysokiej wierności. Układ DAC obsługuje szeroką gamę formatów danych i rozdzielczości, zapewniając kompatybilność z różnymi, wysokiej klasy systemami audio. Układ został zaprojektowany tak, aby obsługiwać wysokie częstotliwości próbkowania (do 768 kHz) oraz formaty danych wejściowych PCM i DSD. AK4499EQ nie jest jednak samodzielnym przetwornikiem – do działania potrzebuje układu AK4199, który zawiera modulator delta-sigma.

Nieistniejąca już firma Wolfson (przejęta przez Cirrus Logic) oferowała swego czasu przetworniki WM8740, WM8741 i WM8742. Miały one trochę gorsze parametry (zakres dynamiki: 128 dB, THD+N: –104 dB), ale były cenione za subiektywnie bardzo dobrą jakość dźwięku. Autor sam używa przetwornika z dwoma układami WM8741 i może te opinie tylko potwierdzić.

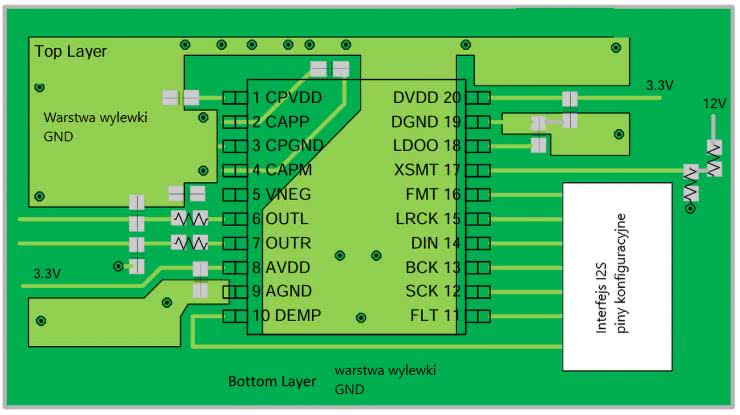

Tych kilka konstrukcji to tylko mała próbka możliwości nowoczesnych przetworników cyfrowo-analogowych. Na rynku można znaleźć wiele układów o zróżnicowanych parametrach i cenach, co pozwala dostosować wybrany układ do wymagań technicznych i posiadanego budżetu. Jednym z przykładów może być przetwornik PCM5102A (Texas Instruments) – patrz rysunek 20. Układ ten wyznacza nowy trend w układach DAC charakteryzujących się świetnymi parametrami i bardzo prostą implementacją. Rozbudowane przetworniki wymagają wielonapięciowego zasilania (w tym zasilania ujemnego dla wzmacniaczy operacyjnych filtrów analogowych). W niektórych urządzeniach, na przykład zasilanych bateryjnie, taki wymóg będzie zawsze problemem. Układ PCM5102A jest natomiast bardzo prosty w aplikacji – może być zasilany pojedynczym napięciem +3,3 V (zaś jego sekcja cyfrowa akceptuje napięcia z zakresu +1,8...3,3 V). Nadpróbkowanie umożliwia zastosowanie bardzo prostego filtra dolnoprzepustowego, zbudowanego z dwóch elementów: rezystora i kondensatora. Nacisk na elastyczność aplikacyjną widać chociażby po budowie interfejsu wejściowego I²S. Przetworniki delta-sigma potrzebują – oprócz standardowych trzech sygnałów (danych, zegara taktującego przesył bitów BCK oraz identyfikacji kanałów PRCK) również sygnału master clock o wielokrotności częstotliwości próbkowania (standardowo od 128·fS do 512·fS). Jeżeli źródło danych audio nie dostarcza przebiegu master clock, to PCM5102A potrafi go sobie wewnętrznie wygenerować w układzie PLL, na podstawie zegara BCK. Można to wykorzystać np. przy budowie przetwornika DAC połączonego interfejsem I²S z Raspberry Pi.

Jak już wspomniałem, przetworniki DAC są obecne we wszystkich nowoczesnych układach audio. Z wyjątkiem transmisji analogowego radia FM wszystkie współczesne media są cyfrowe i konwersja cyfrowo-analogowa okazuje się nieodzowna. Oprócz klasycznych płyt CD także radio DAB, telewizja naziemna DVB-T2, streaming, odtwarzanie plików z nośników wymiennych (np. pamięci USB), czy wreszcie połączenia Bluetooth (na przykład ze słuchawkami) korzystają z cyfrowej reprezentacji materiału audio, który musi zostać przekonwertowany na postać analogową przez przetwornik cyfrowo-analogowy. Dlatego niezbędne są rozwiązania łatwe w produkcji, a w konsekwencji – tanie. Ten warunek spełnia topologia oparta na konwerterach z modulatorem delta-sigma. Przetworniki najwyższej klasy, używane w konstrukcjach audiofilskich, to zapewne ważna, ale niezbyt duża część rynku.

Budowa przetwornika o doskonałych parametrach przez amatora – entuzjastę dobrego brzmienia – nie jest zadaniem szczególnie trudnym. Trzeba jednak znać kilka zasad i konsekwentnie ich przestrzegać. Dwie chyba najważniejsze, to zastosowanie odpowiedniego projektu płytki oraz wybór właściwego układu zasilania. Można próbować różnych rozwiązań – od wspominanych już NOS DAC, aż po klasyczne przetworniki z filtrem cyfrowym interpolatora i analogowym filtrem rekonstruującym.

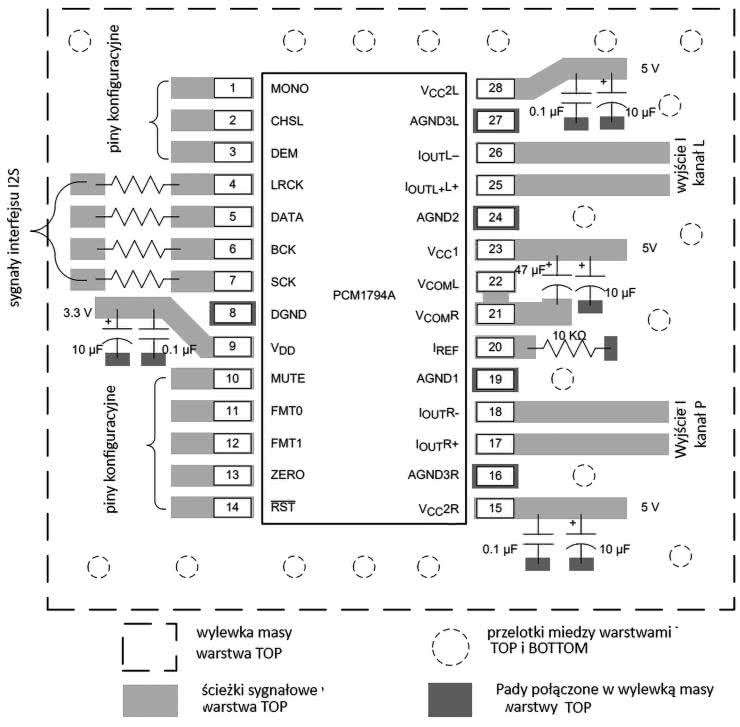

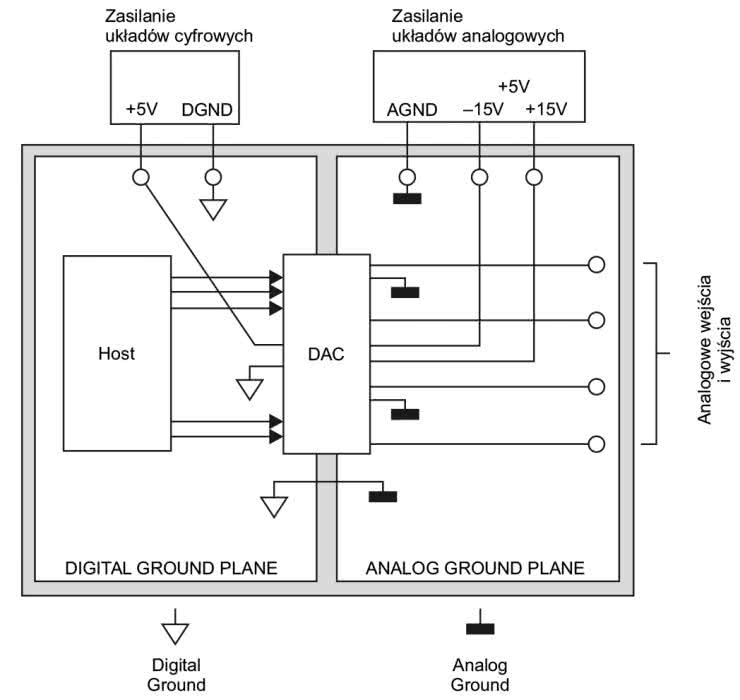

Ważną cechą wpływającą na prawidłową aplikację przetworników jest ich specyficzna budowa. Są to układy typu mixed-signal, czyli zawierające w swojej strukturze zarówno obwody cyfrowe, jak i analogowe. Niestety komplikuje to konstrukcję urządzenia, bo układy cyfrowe mogą wprowadzać do części analogowej zakłócenia, przenoszone głównie przez obwody zasilania i masy. Trzeba bowiem pamiętać, że układy cyfrowe – w trakcie przełączania wewnętrznych obwodów z jednego stanu logicznego na przeciwny – pobierają z obwodów zasilania impulsy prądowe, które generują zakłócenia napięciowe na zasilaniu czułych obwodów analogowych. Aby ten efekt maksymalnie zneutralizować, stosuje się rozdzielanie mas: cyfrowej (DGND) i analogowej (AGND), a także osobne ich wyprowadzenie w układzie scalonym. Podobnie ma się sprawa z liniami zasilającymi obwody cyfrowe oraz analogowe przetwornika.

Niestety i tak obie masy – cyfrowa i analogowa – muszą być ze sobą galwanicznie połączone, żeby układ konwertera mógł działać prawidłowo. Jedną z metod radzenia sobie z tym problemem jest stosowanie jednej wylewki masy, połączonej w wyprowadzeniami DGND i AGND. Takie podejście sugeruje producent układu PCM1794A – rysunek 21. Wylewka masy jest położona na warstwie wierzchniej (TOP), żeby wyprowadzenia układu mogły być do niej bezpośrednio przylutowane. Na warstwie spodniej (pod układem) również znajduje się wylewka masy. Obie płaszczyzny miedzi są połączone ze sobą szeregiem przelotek.

Bardzo podobne rozwiązanie jest sugerowane także w przypadku układu PCM5102A. Użyto wspólnej masy dla całego urządzenia. Masę GND można uznać za połączone AGND i DGND. Podobnie jak w przypadku PCM1794A, kluczowe jest takie ułożenie elementów, żeby zakłócenia z układów cyfrowych nie przenikały do części analogowej (rysunek 22).

Nie jest to oczywiście jedyne rozwiązanie. Inną możliwością jest stosowanie na płytce dwóch oddzielnych mas: analogowej i cyfrowej (na przykład w formie oddzielnych wylewek połączonych w jednym wybranym miejscu tak, by ewentualne prądy masy obwodów cyfrowych nie płynęły przez obwody analogowe). Projektant musi się tu zdać na własne doświadczenie. Idea takiego rozwiązania została pokazana na rysunku 23. Rozdzielenie mas pozwala na stosowanie układów zasilania, które również mają swoje „własne” masy (analogową i cyfrową) niepołączone ze sobą poza wspomnianym punktem wspólnym.

Bardzo ważnym aspektem prawidłowego działania przetworników DAC jest zasilanie. O masach już co nieco powiedzieliśmy. W przetwornikach wyższej klasy sekcje cyfrowa i analogowa powinny być zasilane z osobnych stabilizatorów, nawet jeżeli pracują one z tym samym napięciem (np. +5 V). Przykładem może być nakładka przetwornika DAC przeznaczona do komputerów Raspberry Pi. Mamy tu do dyspozycji jedno napięcie +5 V, które w dodatku zaśmiecone jest zakłóceniami z układów cyfrowych Raspberry Pi. Można sobie częściowo poradzić z tym problemem stosując szeregowe dławiki na liniach zasilania, ale bardzo dobrym rozwiązaniem jest zastosowanie dwóch stabilizatorów dla sekcji cyfrowej i analogowej, jeżeli przetwornik jest zasilany niższym napięciem np. +3,3 V. Tak jest np. w przypadku PCM5102A. W bardziej rozbudowanych konstrukcjach stosuje się nawet oddzielne uzwojenia transformatorów, mostki prostownicze i filtry.

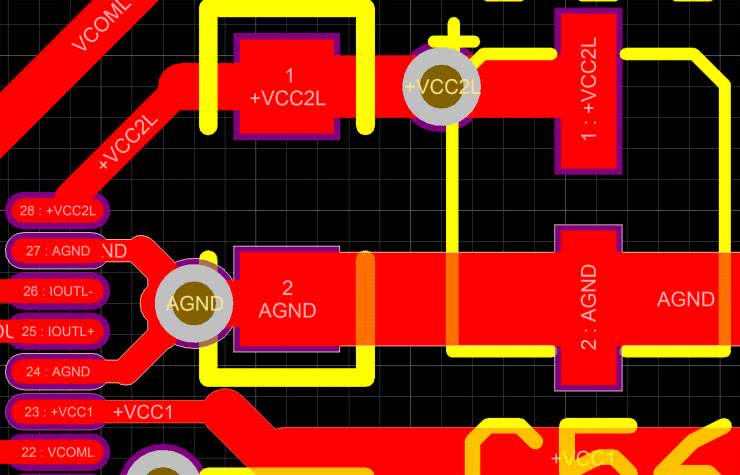

Bardzo ważnymi aspektami w projekcie układu zasilania są kondensatory blokujące i doprowadzenie ścieżek do wyprowadzeń układu przetwornika. Najczęściej spotykana jest para kondensatorów: ceramiczny 100 nF (tłumiący zakłócenia o wyższych częstotliwościach) i elektrolityczny (aluminiowy lub tantalowy) 1...10 μF, pełniący rolę lokalnego magazynu energii dla współpracującego układu. Kondensatory blokujące powinny być umieszczone jak najbliżej wyprowadzeń układu scalonego, a ścieżki łączące kondensatory i wyprowadzenia zasilania układu – jak najgrubsze. Nowoczesne obudowy mają gęsty raster i stosunkowo cienkie wyprowadzenia, dlatego często jest to zadanie nietrywialne. Na rysunku 24 pokazano ścieżki zasilania napięcia analogowego 5 V (+VCC2L) wraz z kondensatorami blokującymi w układzie z przetwornikiem PCM1794A. Najbliżej wyprowadzeń znajduje się kondensator ceramiczny SMD w obudowie 1206, a równolegle do niego – kondensator elektrolityczny 10 μF, również w obudowie do montażu powierzchniowego.

Na rysunku 25 widać podłączenie napięcia +3,3 V sekcji cyfrowej układu PCM1794A. Tu zasada jest bardzo podobna. Kondensator SMD 100 nF znajduje się jak najbliżej wyprowadzeń zasilania układu. Równolegle do niego dołączono kondensator elektrolityczny SMD 10 μF.

Co jakiś czas w Internecie pojawiają się dyskusje na temat wartości pojemności kondensatorów blokujących. Niektórzy twierdzą, że standardowa para 100 nF – 10 μF nie jest odpowiednia i trzeba stosować inne wartości, a najlepiej trzy lub więcej kondensatorów o równych wartościach, połączonych równolegle. Żeby rozstrzygnąć kto ma rację, trzeba byłoby eksperymentować z różnymi wartościami i mierzyć na przykład szumy na wyjściu przetwornika. Często pojawia się argument: „tak brzmi lepiej”, którego niestety nie można przyjąć w praktyce inżynierskiej. Ja nie zaobserwowałem mierzalnej poprawy parametrów przy eksperymentowaniu z wartościami kondensatorów, podanymi w jednym z wpisów internetowych – mimo że jego autor opisywał wyraźny wpływ na brzmienie. Tego również nie zarejestrowałem.

Para kondensatorów 100 nF około 10 μF to bezpieczny wybór w zdecydowanej większości przypadków. W obwodach analogowych można zwiększyć pojemność do 22 μF czy nawet do 47 μF, a w obwodach cyfrowych zastosować kondensator tantalowy. A jeżeli ktoś z Czytelników dysponuje odpowiednimi możliwościami pomiarowymi, to może również eksperymentować z innymi wartościami elementów.

Oprócz prawidłowego odsprzęgania zasilania powinniśmy dysponować także dobrze stabilizowanym źródłem napięcia. Najlepiej do tego celu zastosować stabilizatory niskoszumne. Na rynku jest ich bardzo dużo i można je dobrać zależnie od potrzebnego napięcia wyjściowego, dopuszczalnego prądu i poziomu szumów. Ja stosuję na przykład układy LT1763 o bardzo przyzwoitych parametrach. Można je stosować zarówno w układach cyfrowych, jak i analogowych.

Co ciekawe, w sieci krążą schematy układów zasilających przetworniki o topologiach rodem z początku lat 70., oparte na diodach Zenera w roli źródeł napięcia odniesienia. Czasami są to nawet stabilizatory parametryczne bez pętli ujemnego sprzężenia zwrotnego. Takie układy mają kiepskie parametry stabilizacyjne i równie słabo wypadają pod względem szumów. Zasilanie nowoczesnych przetworników (a nawet tych starszych) za pomocą takich prymitywnych stabilizatorów zupełnie mija się z celem. I znów – za ich stosowaniem stoi argument, że podobno... poprawiają brzmienie.

Zasilacz przetwornika często musi dostarczać napięcia symetryczne (na przykład ±15 V czy ±12 V) do zasilania wzmacniaczy operacyjnych konwertera prąd-napięcie. To napięcie powinno być również dobrze stabilizowane, pozbawione tętnień sieciowych i szumów szerokopasmowych. Niezłym pomysłem jest zastosowanie układów LM317 i LM337. To już leciwe konstrukcje, ale do zasilania układów analogowych nadają się zaskakująco dobrze. Trzeba pamiętać, by układy nabywać ze sprawdzonego źródła, gdyż na rynku można znaleźć mnóstwo słabej jakości podróbek.

Niezależnie od zastosowanego rozwiązania jako absolutne minimum należy przyjąć przestrzeganie zaleceń producenta układu stabilizatora. Zawsze aktualne są zasady dotyczące prowadzenia mas na obwodach drukowanych tak, by nie tworzyć pętli masy. Dobrym pomysłem jest stosowanie wylewek miedzi i jak najszerszych ścieżek prądowych. Trzeba stosować dobre elementy ze sprawdzonego źródła. Dotyczy to szczególnie stabilizatorów i kondensatorów elektrolitycznych.

W większości dobrych przetworników analogowy sygnał wyjściowy ma postać prądową. W takich przypadkach będzie potrzebny zewnętrzny konwerter prąd-napięcie. Klasycznie do tego celu stosowany jest układ wzmacniacza transimpedancyjnego – rysunek 26.

Ten układ można bardzo łatwo zrealizować za pomocą wzmacniaczy operacyjnych. Z reguły wymaga się, żeby były to układy miały z tranzystorami polowymi, o jak najmniejszym prądzie polaryzacji wejść. Klasykiem jest wzmacniacz OPA627 z wejściami JFET, stosowany w najlepszych konstrukcjach przetworników. Dzisiaj jest to wybór bardzo drogi i niestety często podrabiany. Ale można zastosować wzmacniacz OPA828, wskazywany przez producenta jako następca OPA627. OPA828 jest bieżąco produkowany i dostępny u sprawdzonych dystrybutorów elementów elektronicznych. Co ciekawe, firma Texas Instruments poleca też do pracy w konwerterach bardzo dobre wzmacniacze z wejściami bipolarnymi typu OPA6211 lub OPA1612. Mają one typowy prąd polaryzacji wejścia na poziomie ±60 nA, zaś w przypadku OPA828 parametr ten plasuje się na poziomie 1 pA.

Mimo że rozwiązanie z rysunku 26 ma bardzo dobre parametry, to i tutaj nie brakuje opinii, że lepiej jest zastosować zwykły rezystor o określonej rezystancji, włączony w prądowy obwód wyjścia przetwornika. Spadek napięcia na tym rezystorze stanowi napięciowy sygnał wyjściowy. Stosowane są też rozbudowane układy tranzystorowe, mające podobno doskonałe walory brzmieniowe. Oczywiście eksperymentowanie nie jest niczym złym – tym bardziej, jeżeli efekt końcowy zadowala konstruktora. Jednak klasyczny układ z rysunku 26 jest zawsze godny polecenia i powinien dawać bardzo dobre rezultaty, oczywiście pod warunkiem zastosowania dobrego wzmacniacza i dobrej jakości pozostałych elementów (szczególnie kondensatora).

Jedną z popularnych metod „poprawiania” dźwięku przetwornika jest stosowanie na wyjściu układów lampowych (buforów, SRPP itp.) które w założeniu mają dawać „lampowe brzmienie”. Jednak według mnie lepszym sposobem jest zbudowanie przetwornika pracującego zgodnie z teorią i zaleceniami producenta, a następnie podanie sygnału z jego wyjścia na dobry wzmacniacz lampowy. Ja stosuję opisywany na łamach EP wzmacniacz Sansuix i jeden z przetworników mojej konstrukcji z układem PCM1794A. Efekty są znakomite.

Należy też pamiętać, że nie zawsze są nam potrzebne najlepsze dostępne na rynku układy DAC. Na początek nie musimy sięgać po topowe, bardzo drogie konstrukcje. Żeby w pełni wykorzystać ich potencjał, trzeba mieć naprawdę duże doświadczenie w konstruowaniu tego typu układów. Warto zacząć np. od wspominanego już układu PCM5102A. Jest on zasilany napięciem +3,3 V (sekcja cyfrowa i sekcja analogowa). Wbudowany układ przetwornicy napięcia (pompa ładunkowa) umożliwia – przy pojedynczym napięciu zasilania +3,3 V – uzyskanie na wyjściu układu sygnału o napięciu 2,1 V (RMS). Nadpróbkowanie powoduje znaczące uproszczenie wyjściowego, dolnoprzepustowego filtra rekonstruującego. Może to być chociażby zwykły, pasywny filtr RC. Obecnie używam przetwornika DAC zbudowanego na bazie tego układu i pracującego jako nakładka HAT do komputera Raspberry Pi 4B (połączenie przez interfejs I²S). Układ ten, mimo swojej prostoty aplikacyjnej, generuje zaskakująco dobry dźwięk, co potwierdzają również pomiary.

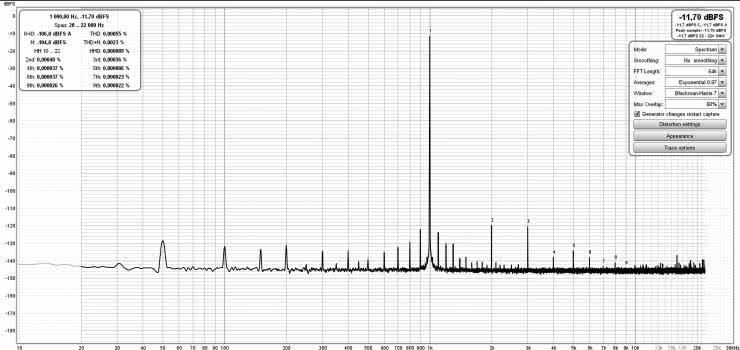

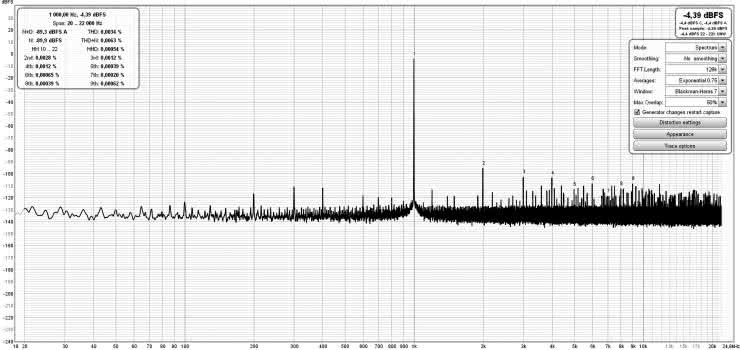

Bardziej zaawansowani użytkownicy mogą się pokusić o zmierzenie parametrów budowanego przetwornika. Trzeba jednak pamiętać, że katalogowe parametry większości popularnych konwerterów wyższej klasy są na takim poziomie, że amatorski tor pomiarowy oparty na karcie muzycznej może nadmiernie degradować pomiar. Wobec tego – czy warto mierzyć? Oczywiście, że warto. Jeżeli otrzymamy parametry bliskie parametrom karty pomiarowej, to jest duże prawdopodobieństwo, że nasz przetwornik pracuje poprawnie. Poza tym w pomiarach – oprócz parametrów THD, THD+N i IMD – można ocenić poziom składowych częstotliwości sieciowej 50 Hz i jej wyższych harmonicznych. To może nam dać odpowiedź na pytanie, czy dobrze zaprojektowaliśmy układ pod względem zasilania sieciowego. Zbyt duży poziom szumów może być wynikiem złego prowadzenia mas, a zniekształcenia IMD zwiastują problemy z filtrowaniem dolnoprzepustowym. Ja staram się mierzyć swoje konstrukcje. Używam programu REW i karty Scarlett 2i2. Do pomiarów niezbędny jest konwerter USB-I²C, na przykład typu Amanero – po to, by na wejście przetwornika można było podać strumień danych reprezentujący sygnał sinusoidalny o częstotliwości 1 kHz. Wyjście audio przetwornika łączymy z wejściem karty – i już można wykonać pomiar. Na rysunkach 27 i 28 zostały pokazane wyniki pomiarów przetworników z układami PCM1794A i PCM5102.

Pierwszy to dość rozbudowany przetwornik z wielosekcyjnym zasilaczem, konwerterem i filtrem dolnoprzepustowym na wzmacniaczach operacyjnych. THD+N jest równe 0,0023%. Katalogowo układ powinien mieć THD+N równe 0,0004%. Różnica jest wyraźna, jednak – jak już powiedziałem – ograniczeniem może być układ pomiarowy z kartą muzyczną. W danych technicznych karty producent podaje THD+N na poziomie 0,002%, więc za pomocą tego zestawu nie da się wiarygodnie zmierzyć THD+N = 0,0004%. Poza tym podawane przez producenta parametry potrafią być wyśrubowane w firmowym laboratorium i w rzeczywistości trudno je powtórzyć. W naszej sytuacji nie sposób zatem rozstrzygnąć tej kwestii.

Drugi przetwornik jest o wiele prostszy, w trakcie pomiaru zasilany za pomocą zasilacza impulsowego – bo taki był cel tego pomiaru. THD jest na poziomie 0,0034% co odpowiada wartości –89 dB. Katalogowo THD tego przetwornika wynosi –92 dB, więc jak na tę prostą konstrukcję i zasilanie uzyskany wynik jest dość bliski parametrów nominalnych.

Podsumowanie

Temat konstrukcji przetworników cyfrowo-analogowych jest bardzo szeroki. W niniejszym artykule zaprezentowałem kilka bardzo ogólnych zaleceń dotyczących zasilania, projektu płytki PCB czy układów wyjściowych. Nic jednak nie zastąpi doświadczenia konstruktora, które każdy musi nabyć sam tworząc własne konstrukcje. Mamy do wyboru wiele nowoczesnych przetworników o rewelacyjnych parametrach, a do tego dochodzi łatwa dostępność bardzo dobrych elementów pasywnych, wzmacniaczy operacyjnych, stabilizatorów itp. Możemy – za naprawdę niewielkie kwoty – zamówić profesjonalnie wykonane płytki drukowane dwuwarstwowe, a w uzasadnionych przypadkach czterowarstwowe. Nawet amatorzy mogą sobie pozwolić na zakup przyrządów pomiarowych, o których kilkanaście lat temu można było tylko pomarzyć. I wreszcie – można konstruować własne przetworniki, czerpiąc z tego niemałą satysfakcję.

Tomasz Jabłoński, EP

Zaloguj

Zaloguj