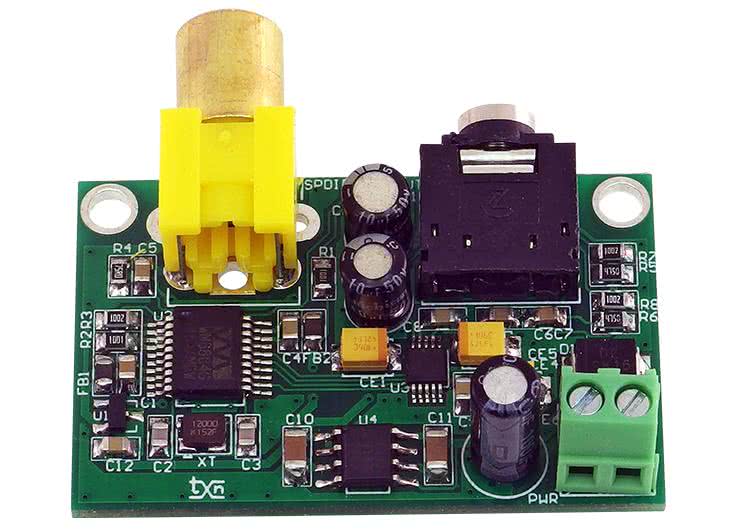

- wejście SPDIF,

- przetwornik audio o parametrach: 192 kHz/24 bity,

- niewielkie wymiary płytki,

- zasilanie 4,5…6 V/100 mA.

W module zastosowano układ odbiornika/dekodera sygnału SPDIF do standardu I2S typu WM8804 oraz układ CS4344 firmy Cirrus Logic, który jest kompletnym rozwiązaniem przetwornika D/A audio 192 kHz/24 bity. Przetwornik pochodzi z linii produktów znajdujących zastosowanie w sprzęcie przenośnym powszechnego użytku.

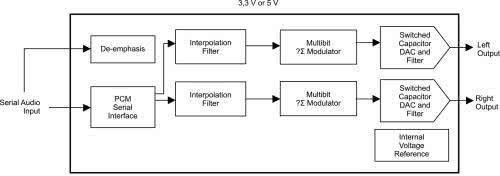

Schemat wewnętrzny CS4344 został pokazany na rysunku 1. Układ zawiera wszystkie elementy konieczne do odbioru sygnału I2S i przetwarzania D/A. Do poprawnej pracy wymaga kilku elementów zewnętrznych tj. kondensatorów odprzęgających zasilanie i prostego filtra wyjściowego RC. Sygnał I2S poddany zostaje cyfrowej interpolacji i filtrowaniu w bloku filtrów cyfrowych (taktowanych sygnałem MCLK), stąd poprzez modulatory delta-sigma trafia na przetwornik z przełączanymi pojemnościami, konwertujący sygnał do postaci analogowej, który filtrowany jest dolnoprzepustowym filtrze analogowym RC.

Przetwornik CS4344 został wybrany ze względu na przyzwoite parametry, prostotę aplikacji, łatwą w montażu obudowę MSOP10 oraz niski koszt aplikacji. W tej samej obudowie dostępne są też przetworniki ze standardem LJ (CS4345) i RJ (CS4334).

Budowa i działanie

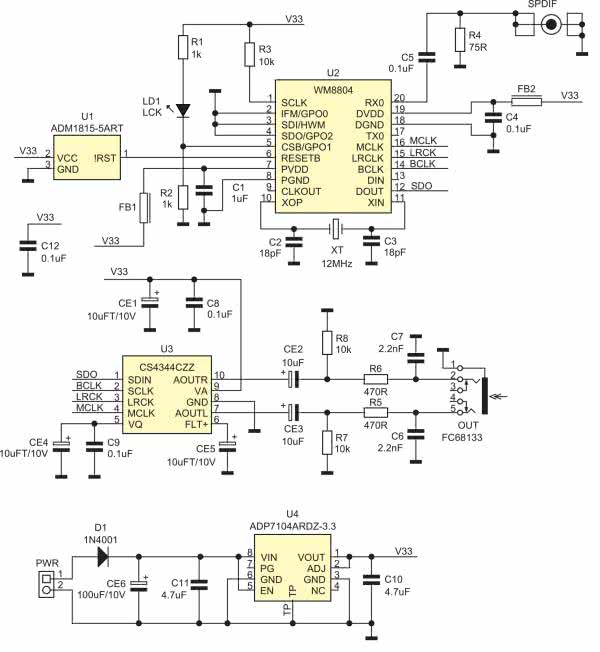

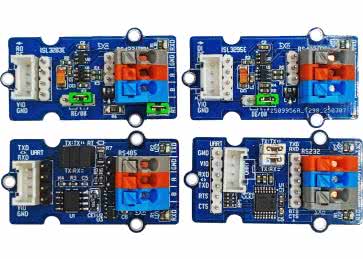

Schemat modułu został pokazany na rysunku 2. Sygnał cyfrowy audio z wejścia SPDIF typu RCA jest doprowadzony do odbiornika SPDIF U2, typu WM8804. Odbiornik pracuje z konfiguracją ustalaną sprzętowo, za pomocą wyprowadzeń SCLK, HWM, GPO0, GPO1, GPO2. Po zdekodowaniu sygnału SPDIF wyjście w standardzie I2S jest doprowadzone do przetwornika D/A U3 typu CS4344.

Układ WM8804 pracuje w trybie master, generując sygnały taktujące magistrali I2S: LRCK, BCLK oraz sygnał zegarowy MCLK. Układ resetu U1 ADM1815 zapewnia poprawny start U2 po załączeniu zasilania. Napięcie zasilające odbiornik dodatkowo filtrowane jest poprzez FB1/C1 dla obwodu wbudowanego PLL i FB2/C4 dla części cyfrowej. Układ U2 jest taktowany kwarcem XT o częstotliwości 12 MHz. Dioda LD1 sygnalizuje poprawne dekodowanie sygnału SPDIF.

Sygnał wyjściowy z przetwornika D/A poprzez kondensatory separujące składową stałą CE2, CE3 jest doprowadzony do prostego filtru dolnoprzepustowego z elementami R6, C7 i R5, C6 eliminując ego pozostałości przetwarzania D/A. Układ odbiornika U2 i przetwornika U3 zasilany jest napięciem 3,3 V pochodzącym z niskoszumnego stabilizatora U4 typu ADP7104. Moduł wymaga zasilania napięciem stałym o wartości 4,5...6 V/100 mA poprzez złącze PWR. Dioda D1 zabezpiecza przed uszkodzeniem w przypadku odwrotnego podłączenia zasilania, kondensatory C10, C11, CE6 odsprzęgają zasilanie.

Montaż i uruchomienie

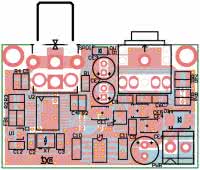

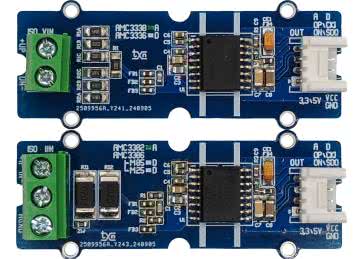

Układ jest zmontowany na niewielkiej płytce drukowanej pokazanej na rysunku 3.Sposób montażu jest klasyczny i nie wymaga szczegółowego opisu. Układ nie wymaga uruchomienia, po poprawnym zmontowaniu i sprawdzeniu poprawności można podłączyć źródło SPDIF, zasilanie i cieszyć się muzyką.

Ze względu na niewielki rozmiar i pobór mocy możliwe jest zastosowanie „mobilne” przetwornika i zasilanie go z pakietu 4 akumulatorów Ni-MH połączonych szeregowo.

Adam Tatuś

adam.tatus@ep.com.pl

- R1, R2: 1 kΩ SMD0805, 1%

- R3, R7, R8: 10 kΩ SMD0805, 1%

- R4: 75 Ω SMD0805, 1%

- R5, R6: 470 Ω SMD0805, 1%

- C1: 1 µF SMD0805

- C2, C3: 18 pF SMD0805

- C4, C5, C8, C9, C12: 0,1 µF SMD0805

- C6, C7: 2,2 nF SMD0805

- C10, C11: 4,7 µF SMD1206

- CE1, CE4, CE5: 10 µFT/10 V SMA tantalowy

- CE2, CE3: 10 µF/10 V elektrolityczny

- CE6 100 µF/10 V elektrolityczny

- LD1: LED SMD0805

- D1: 1N4001 SMD

- U1: ADM1815-5ART (SOT-23)

- U2: WM8804 (SSOP20)

- U3: CS4344CZZ (TSSOP10)

- U4: ADP7104ARDZ-3.3 (SO8TP)

- FB1, FB2: dławik ferrytowy 600 R/100 mA SMD0805

- XT: rezonator kwarcowy 12 MHz 3,2×2,5 mm

- OUT: gniazdo mini jack 3,5 mm stereo

- PWR: złącze śrubowe 3,5 mm 2 pin

- SPDIF: gniazdo RCA do druku

Zaloguj

Zaloguj