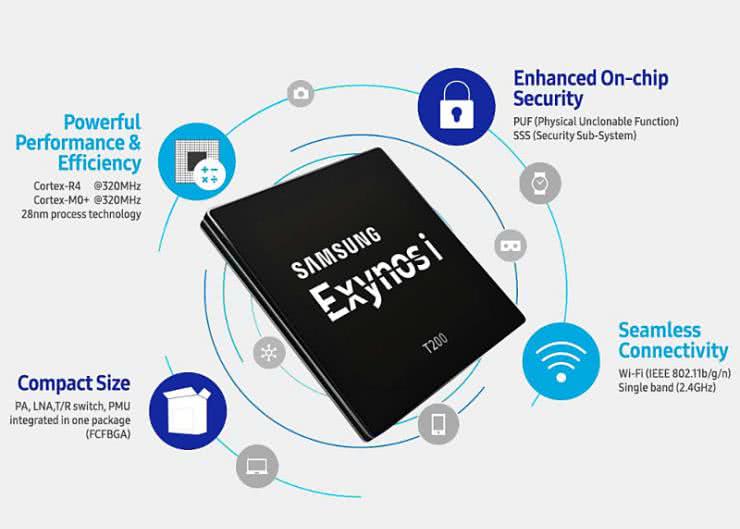

Zawiera on jeden rdzeń Cortex-R4 i jeden Cortex-M0+, które mogą pracować jednocześnie. Ma zintegrowany transceiver Wi-Fi (2,4 GHz) oraz wzmacniacz, dzięki czemu nie wymaga stosowania wielu dodatkowych komponentów nawet przy budowie urządzeń korzystających z zaawansowanych protokołów sieciowych. Dostępne jest też 1,4 MB pamięci SRAM.

Układ wykonano w 28-nanometrowym procesie technologicznym. Dwa rdzenie zapewniają dobrą wydajność uzyskiwaną m.in. poprzez podział zadań. Przykładowo, Cortex-M0+ może odpowiadać za kontrolę wejść i wyjść oraz sygnalizację za pomocą LED, natomiast Cortex-R4 za pozostałe obliczenia. Oba rdzenie taktowane są zegarem 320 MHz.

Dla wielu aplikacji będą istotne także wbudowane mechanizmy zabezpieczeń oraz szyfrowania PUF (Physically Unclonable Functions), które praktycznie uniemożliwiają podrabianie urządzeń opartych o nowego Exynosa. Zestaw interfejsów obejmuje SDIO, I²C, SPI, UART, PWM i I²S. Układ ma byś stosowany przede wszystkim w aplikacjach Internetu Rzeczy.

Zaloguj

Zaloguj