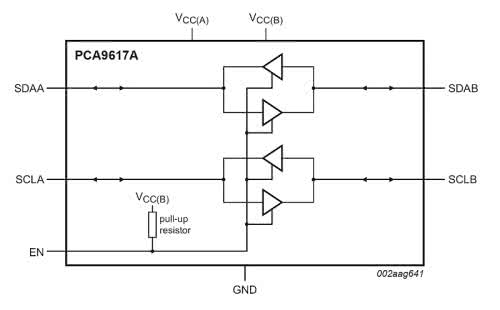

Oprócz zapewnienia przesunięcia poziomów logicznych, układ umożliwia również wydłużenie połączeń magistrali I²C lub dołączenie większej liczby układów - pojemność dołączana do wyjścia może wynosić 540 pF przy częstotliwości sygnału SCL do 1 MHz lub do 4 nF przy mniejszej częstotliwości.

Zastosowanie PCA9617A zapewnia możliwość "odizolowania" systemu hosta od napięcia i pojemności dołączanej magistrali modułu rozszerzenia. Doprowadzenia sygnałów SDA i SCL są odporne na przepięcia i gdy układ nie jest zasilany są w stanie wysokiej impedancji.

Drivery portu B mają ustalone na stałe poziom niski (maks. 0,4 V) i poziom wysoki (0,7×VCC(B), maksymalnie 5,5 V), natomiast dla driverów portu A poziom niski ustalono na 0,25×VCC(A), a poziom wysoki na 0,7×VCC(A), maksymalnie 5,5 V. Statyczny zakres portu B zabezpiecza drivery od dołączenia do stałego lub rosnącego offsetu buforów innej magistrali. Porty A dwóch lub więcej układów PCA9617A mogą być połączone razem, co pozwala na użycie topologii gwiazdy z portem A na wspólnej magistrali.

|

Wiele układów PCA9617A może być połączonych szeregowo, port A do portu B, bez konieczności uwzględniania offsetu - rozważenia wymaga jedynie czas propagacji. Drivery układu nie pracują, jeśli napięcie VCC(A) jest powyżej 0,8 V i VCC(B) powyżej 2,2 V. Napięciem odniesienia dla wejścia EN jest napięcie VCC(B). To wejście może być również użyte do załączenia i wyłączania driverów pod kontrolą hosta. Należy jedynie uważać, aby zmieniać poziom na wyprowadzeniu EN jedynie wtedy, gdy magistrala jest w spoczynku. Najważniejsze parametry:

- 2-kanałowy, dwukierunkowy bufor odseparowuje pojemność i napięcie magistrali wejściowej i wyjściowej, 540 pF z każdej strony układu przy częstotliwości SCL do 1 MHz i do 4 nF przy mniejszej częstotliwości.

- Translacja poziomów logicznych z zakresu 0,8...5,5 V i 2,2...5,5 V.

- Wyprowadzenia, obudowa oraz funkcje kompatybilne z układem PCA9517A w trybie Fast.

- Zakres zasilania portu A (VCC(A)): 0,8...5,5 V, zakres zasilania portu B (VCC(A))2,2...5,5 V.

- Doprowadzenia interfejsu I²C oraz wejście EN tolerujące napięcie 5 V.

- Częstotliwość sygnału zegarowego SCL od 0...1000 kHz (maksymalna częstotliwość może być mniejsza od 1000 kHz, ponieważ repeater wprowadza opóźnienie).

- Wejście EN aktywowane poziomem wysokim, odniesione do VCC(B).

- Wejścia/wyjścia typu otwarty dren.

- Wsparcie dla arbitrażu oraz wydłużania sygnału zegarowego przez repeater.

- Możliwość pracy w trybie Standard, Fast, Fast Mode+ układów I²C oraz SMBus (tryb standardowy i podwyższonego poboru mocy), PMBus, z dołączonymi wieloma układami master.

- Dostępny w obudowach TSSOP8 oraz HWSON8.

Zaloguj

Zaloguj