- Jesteśmy optymistami i uważamy, że rentowność próbnej produkcji w drugiej połowie 2023 roku osiągnie 90%, co pomoże nam w przyszłości nadal zdobywać duże zamówienia od głównych producentów, takich jak Apple i Huida - powiedział dyrektor TSMC. Ponadto wskazał, że masowa produkcja rozpocznie się w 2024 roku.

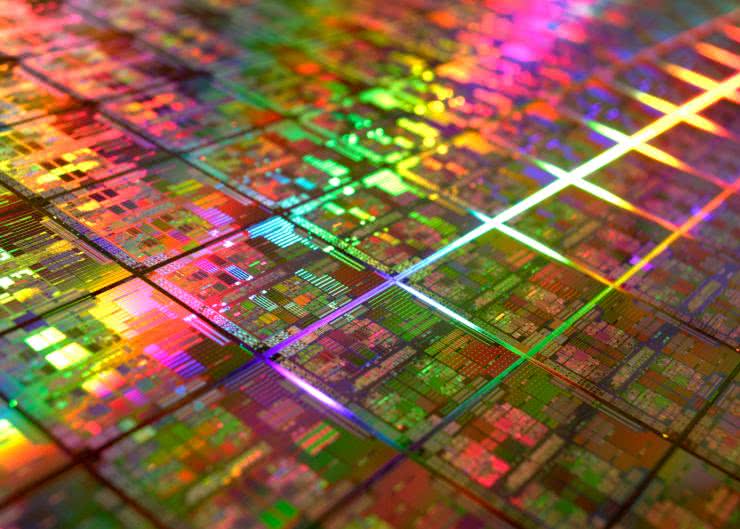

W roku ubiegłym TSMC utworzyło zespół badawczo-rozwojowy procesu 2 nm, aby znaleźć wykonalną ścieżkę rozwoju. Biorąc pod uwagę koszt, kompatybilność sprzętu, dojrzałość technologii i wydajność oraz inne warunki, litografia ta zostanie wdrożona do tranzystorów typu MBCFET wykorzystujących architekturę bramek typu GAA. Architektura rozwiązuje fizyczną granicę upływu prądu spowodowanego skurczem procesu FinFET.

Udoskonalenie procesu w ekstremalnym ultrafiolecie (EUV) sprawiło, że kluczowa technologia układania w stosy nanoarkuszy opracowana przez TSMC przez wiele lat stała się bardziej dopracowana i poprawiła wydajność.

Prezes TSMC, Wei Zhejia, ujawnił kilka dni temu podczas specjalnego spotkania w Yushan Science and Technology Association, że z każdą generacją postępu procesu TSMC efektywność układów scalonych wzrasta o 30 do 40%, a zużycie energii redukowane jest o 20 do 30%.

Firma Apple opublikowała w kwietniu raport zatytułowany "TSMC is already working on 2nm Processors for 2024, they've actually begun Exploratory Studies for nodes beyond 2nm". Tajwański raport wskazuje, że TSMC ogłosiło dalszy rozwój półprzewodników zgodny z prawem Moore'a. Firma jest bardziej pewna możliwości przejścia do 1-nanometrowego procesu w przyszłości. To z pewnością zwiększy różnicę poziomu technologicznego w porównaniu z Samsungiem, który obecnie pozostaje daleko za TSMC.

Takie firmy, jak Apple, Huida, Qualcomm i Supermicro skorzystają w przyszłości z 3- 2- i 1-nanometrowej litografii opracowanej przez TSMC.

źródło: Patently Apple

Zaloguj

Zaloguj