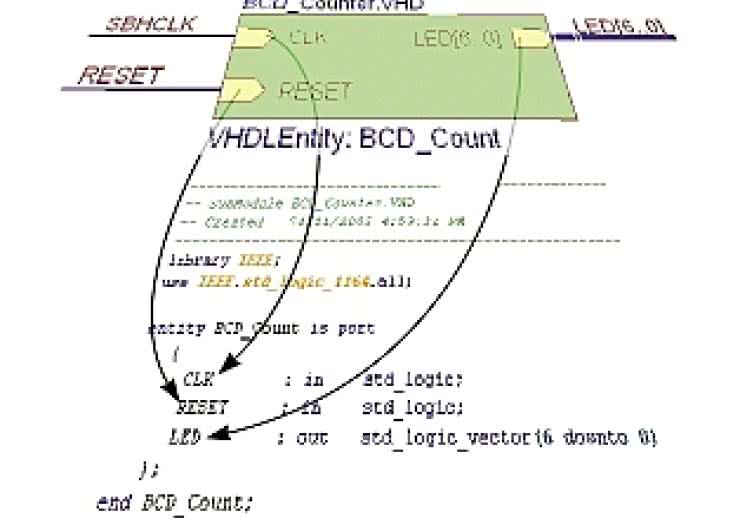

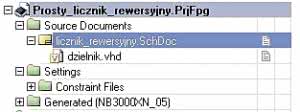

Rysunek 1. Idea projektowania hierarchicznego przedstawiająca symbol arkusza i powiązane z nim dokumenty (schemat lub dokument VHD)

Plik projektu FPGA (* PrjFpg) łączy w sobie różne dokumenty źródłowe w jeden projekt. Projekt hierarchiczny jest zazwyczaj podzielony na moduły logiczne, przy czym każdy z nich jest reprezentowany na arkuszu "rodzica" za pomocą symbolu arkusza (Sheet Symbol). Atrybut Filename symbolu arkusza wiąże go z odpowiadającym mu plikiem. Pliki te mogą występować jako:

- Arkusze schematu.

- Dokumenty Systemu OpenBus.

- Pliki VHDL.

- Pliki Verilog.

Dowolny arkusz schematu może zawierać kolejne symbole arkuszy odnoszące się do kolejnych plików projektowych. Używając takiego podejścia, hierarchia projektu może mieć dowolną "głębokość", dzięki czemu tworzenie złożonych projektów nie nastręcza większych trudności.

Porty wejścia/wyjścia na arkuszu nadrzędnym schematu typu "rodzic" odpowiadają wejściom portom (Sheet Entries) na symbolu arkusza umieszczonego na tym schemacie. Pokazano to na rysunku 1, na którym schemat jest arkuszem nadrzędnym typu "rodzic" natomiast plik VHD jest arkuszem podrzędnym w stosunku do arkusza schematu - jego "córką".

W naszym podstawowym projekcie licznika rewersyjnego zauważyliśmy, iż sygnał zegarowy, którego użyliśmy ma zbyt dużą częstotliwość, aby móc zaobserwować zaświecanie się diod LED. Aby obniżyć tę częstotliwość musimy dodać dzielnik częstotliwości. Zamiast dodawać taki obwód na naszym schemacie, zrobimy to na oddzielnym arkuszu: najpierw jako arkusz schematu, a następnie jako arkusz VHD. Opiszemy ten dzielnik za pomocą języka opisu sprzętu VHDL i pokażemy ideę tworzenia projektów hierarchicznych FPGA. Dzięki temu nasz projekt stanie się bardziej przejrzysty, a poszczególne arkusze będą mogły być użyte w innych projektach jako gotowe bloki funkcjonalne.

Dzielnik częstotliwości sygnału zegarowego na arkuszu schematu

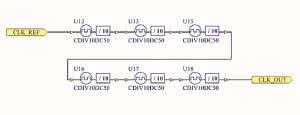

Rysunek 3. Schemat licznika rewersyjnego z symbolem arkusza Dzielnik.SchDoc jako arkusza podrzędnego

W kolejnych krokach dodamy nowy arkusz schematu, który będzie podrzędnym w stosunku do istniejącego arkusza licznik_rewersyjny.SchDoc.

- Otworzyć arkusz schematu licznik_rewersyjny. SchDoc.

- Położyć na wolnym miejscu na schemacie symbol arkusza (Sheet Symbol) za pomocą Place -> Sheet Symbol. Ten symbol arkusza będzie reprezentował arkusz podrzędny, na którym narysujemy dzielnik częstotliwości.

- Kliknąć dwukrotnie na tym symbolu arkusza - otworzy się okno dialogowe Sheet Symbol, w którym wpisujemy następujące parametry (rysunek 2):

- Designator: U_Dzielnik.

- Filename: Dzielnik.SchDoc.

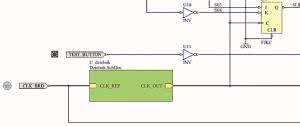

- Teraz zajmiemy się definicją interfejsu dla tego symbolu. W tym celu należy dodać porty wejścia/wyjścia arkusza (Place -> Add Sheet Entry), po jednym z lewej i z prawej strony symbolu. Następnie ustawić parametry:

- Lewy port symbolu arkusza: Name: CLK_REF, I/O Type: Input.

- Prawy port symbolu arkusza: Name: CLK_OUT, I/O Type: Output.

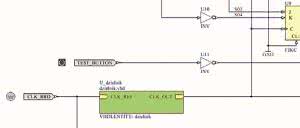

- Umieść symbol arkusza, jak pokazano na rysunku 3, łącząc wyjście z istniejącym obwodem, natomiast do wejścia dołączyć port CLK_BRD.

|

Kolejne etapy przedstawiają krok po kroku proces definiowania schematu Dzielnik.SchDoc. Aby pominąć ten proces , należy kliknąć prawym przyciskiem na Prosty_licznik_rewersyjny.PrjFpg i z panelu Project wybrać Add Existing to Project. Za pomocą okna Choose Documents to Add to Project odszukać plik Dzielnik.SchDoc znajdujący się w materiałach dodatkowych (do pobrania z serwera FTP) i dołączyć go do projektu. Teraz należy zapisać cały projekt, wszystkie zmodyfikowane pliki źródłowe i przejść do etapu kompilowania projektu. |

Mamy już umieszczony symbol arkusza na schemacie nadrzędnym. Teraz musimy stworzyć arkusz podrzędny z takim samym interfejsem i umieścić na nim potrzebne odwody.

- Kliknąć prawym przyciskiem na symbolu arkusza i wybrać Sheet Symbol Actions -> Create Sheet From Sheet Symbol. W wyniku tego powstanie nowy dokument Dzielnik.SchDoc. Zostanie on automatycznie otwarty i stanie się on dokumentem aktywnym. Na arkuszu zostaną automatycznie położone dwa porty CLK_REF i CLK_OUT, które są odpowiednikami portów z symbolu schematu umieszczonego na arkuszu nadrzędnym.

- Otworzyć panel Libraries, odszukać i położyć na pustym arkuszu schematu 6 dzielników zegarowych (CDIV10DC50 - dzielnik przez 10 o 50% współczynniku wypełnienia). Dzielniki te znajdują się w bibliotece FPGA Generic.IntLib. Połączyć je szeregowo pomiędzy dwoma istniejącymi portami, jak pokazano na rysunku 4.

- Ponumerować elementy za pomocą Tools -> Annotate Schematics Quietly.

- Zapisać wszystkie pliki źródłowe oraz projekt za pomocą File -> Save All. Umieść je w domyślnej lokalizacji (t.j. w tym samym katalogu, w którym znajduje się schemat nadrzędny) pod nazwą Dzielnik.SchDoc.

- Skompilować projekt, sprawdzić czy nie ma błędów, skorygować je, jeśli występują. Po skorygowaniu błędów, ponownie zapisać i skompilować projekt.

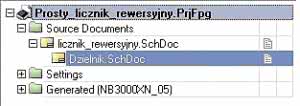

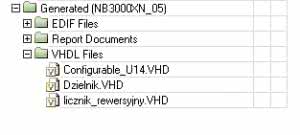

- Po skompilowaniu można sprawdzić hierarchię projektu w panelu Projects. Dotychczasowy arkusz schematu jest teraz arkuszem nadrzędnym (rodzicem), natomiast nasz arkusz dzielnika (Dzielnik.SchDoc) jest teraz arkuszem podrzędnym (córką). Pokazano to na rysunku 5.

Teraz kiedy już mamy gotowy projekt, należy go przetestować na naszej płycie uruchominiowej NB3000.

- Otworzyć Devices, upewnić się, że opcja Live jest załączona i kontrolka stanu połączenia Connection ma kolor zielony.

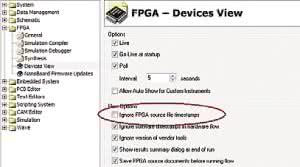

- Układ FPGA pozostaje nadal zaprogramowany. Na belce Flow Control widzimy, że wszystkie pośrednie etapy są kompletne, tzn. wszystkie kontrolki są koloru zielonego. Jeżeli tak, to czemu nie ma sygnalizacji, że pliki źródłowe zostały zmodyfikowane? Odpowiedź na to pytanie znajduje się na rysunku 6. Kiedy jest opcja Ignore FPGA source jest załączona, wtedy informacja o tym że pliki źródłowe zostały zmodyfikowane nie jest przenoszona do panelu Device. Należy tę opcję ustawić jak pokazano na rysunku 7.

- Zaprogramować układ FPGA. Aby to zrobić, należy kliknąć bezpośrednio na Program FPGA. Wszystkie wcześniejsze etapy zostaną uruchomione automatycznie, ponieważ zmodyfikowano pliki źródłowe. Po zakończeniu etapu syntezy pojawi się w katalogu VHDL Files nowy plik automatycznie wygenerowany na podstawie nowego schematu Dzielnik. SchDoc.

|

W kolejnych punktach pokażemy krok po kroku sposób utworzenia pliku podrzędnego w języku opisu sprzętu. Aby pominąć ten etap, należy kliknąć prawym przyciskiem na Prosty_Licznik_Rewersyjny.PrjFpg na panelu Project i wybierać Add Existing to Project. W oknie Choose Documents to Add to Project dodać plik Dzielnik.vhd znajdujący się w materiałach dodatkowych (do pobrania z serwera FTP). Następnie należy zapisać projekt i ewentualnie usunąć dodany wcześniej plik arkusza schematu Dzielnik.SchDoc. |

Po zaprogramowaniu układu FPGA licznik rozpoczyna zliczanie (ustaw 7 lub 8 sekcję przełącznika DIP w pozycji ON) i obserwuj LED na NanoBoard. Widać, że częstotliwość taktowania znacznie spadła i możemy zobaczyć sekwencję zaświecania się diod LED.

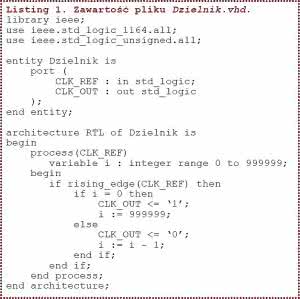

Dzielnik z użyciem pliku HDL

Koncepcja projektowania oparta na projektach hierarchicznych może być bardzo wygodna, gdy stosujemy w projekcie zarówno pliki w postaci arkuszy schematu, jak i pliki źródłowe w językach opisu sprzętu. Przy czym językiem opisu sprzętu może być VHDL i Verilog. Przy odwoływaniu się do arkusza podrzędnego VHD połączenie jest realizowane za pomocą jednostki projektowej entity. Dlatego symbol arkusza VHD zawiera dodatkowo parametr VHDLENTITY.

W przykładzie zastąpimy dzielnik narysowany za pomocą symboli umieszczonych na schemacie programem w języku opisu sprzętu. Tak jak poprzednio, dzielnik będzie dzielił częstotliwość sygnału zegarowego przez 1000000. Utwórzmy teraz plik źródłowy w języku VHDL.

- Kliknąć prawym klawiszem myszy na Prosty_licznik_rewersyjny.PrjFpg na panelu Projects i wybierać Add New to Project -> VHDL Document. Zostanie utworzony nowy dokument VHD (VHDL1.vhd). Zapisać ten plik pod nazwą Dzielnik.vhd w tej samej lokalizacji, co projekt.

- Przepisać kod źródłowy z listingu 1.

- Zapisać istniejący dokument Dzielnik.vhd

Teraz kiedy mamy już plik źródłowy typu VHD, możemy utworzyć symbol schematu bezpośrednio na jego podstawie. Ale zanim to zrobimy, musimy usunąć istniejący symbol arkusza ze schematu nadrzędnego oraz skojarzony z nim arkusz schematu Dzielnik.SchDoc (jeżeli istnieją):

- Usunąć arkusz podrzędny schematu Dzielnik.SchDoc z projektu FPGA - klikając prawym klawiszem na panelu Projects wybierać Remove from Project.

- Otworzyć schemat Licznik_rewersyjny.SchDoc. Kliknąć na symbolu arkusza i usunąć go klawiszem Delete.

- Z menu wybierać Design -> Create Sheet Symbol From Sheet Or HDL. Gdy pojawi się Choose Document to Place, wybrać plik Dzielnik.vhd i kliknąć OK.

- Położyć nowy symbol arkusza i połączyć w sposób pokazany na rysunku 8.

- Parametry Designator i Filename automatycznie zostaną ustawione na: U_dzielnik i dzielnik.vhd. Zostanie również automatycznie dodany parametr VHDLENTITY z wartością "= dzielnik" (jest to nazwa jednostki projektowej naszego z arkusza VHDL).

- Zapisać schemat i projekt.

- Skompilować projekt, sprawdzić czy nie ma błędów. Jeżeli występują, należy jej poprawić, zapisać pliki i ponownie skompilować projekt.

- Po skompilowaniu można sprawdzić hierarchię projektu w panelu Projects. Dotychczasowy arkusz schematu jest teraz arkuszem nadrzędnym (rodzicem), natomiast arkusz dzielnika (Dzielnik.Vhd) jest teraz arkuszem podrzędnym (córką), jak to pokazano na rysunku 9.

Po zmodyfikowaniu projektu polegającym na dodaniu dzielnika w postaci pliku VHD, należy przetestować poprawność rozwiązania:

- Otworzyć panel Devices i zaprogramować układ FPGA klikając na Program FPGA w oknie Flow Control.

- Po zaprogramowaniu układu FPGA licznik rozpoczyna zliczanie (ustawić 7 lub 8 sekcję przełącznika DIP w pozycji ON) i obserwować diody LED na płytce NanoBoard. Można zauważyć, że częstotliwość taktowania znacznie spadła i jest widoczna sekwencja zaświecania się LED.

Wojciech Pietrasina

Evatronix SA

Zaloguj

Zaloguj