PGA450-Q1

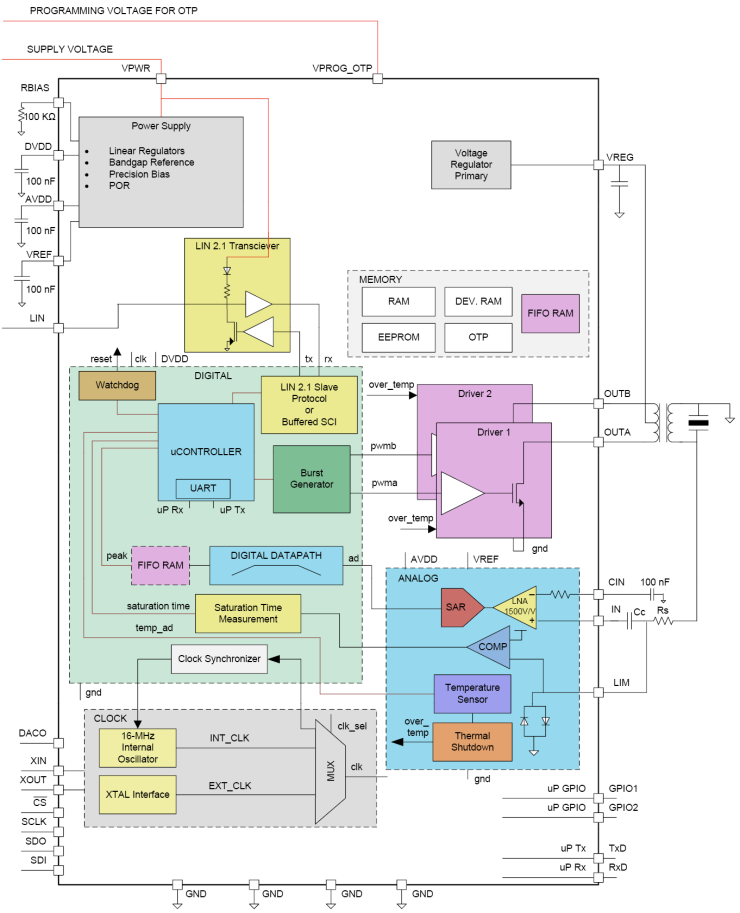

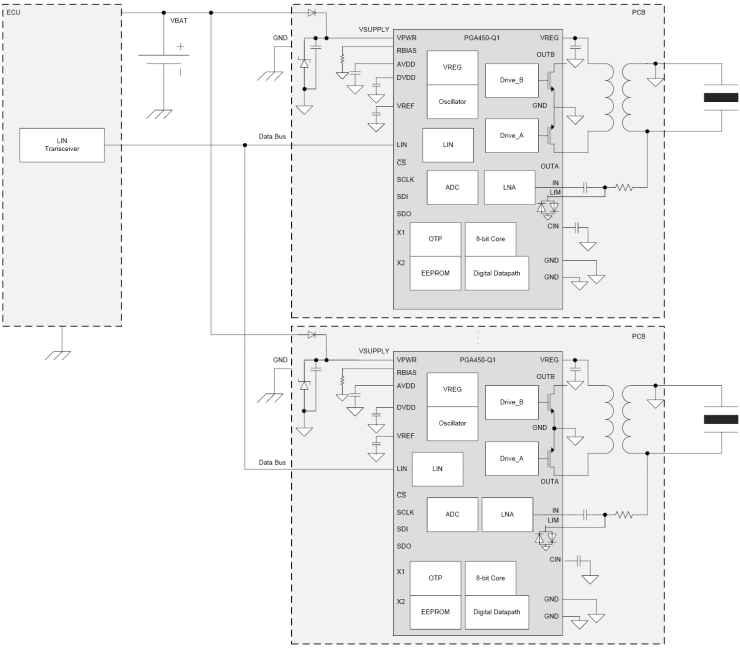

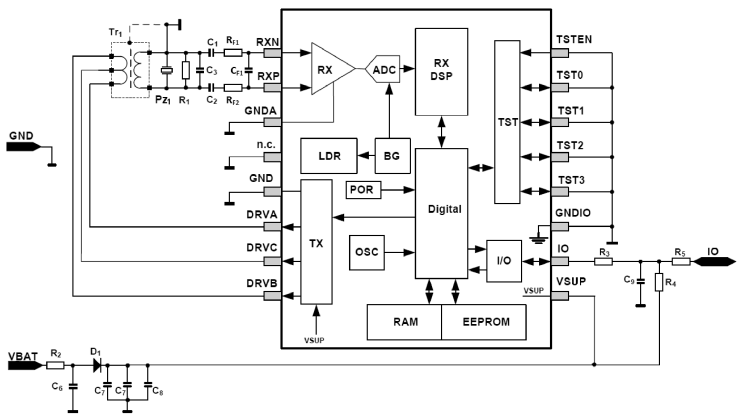

Kolejny interesujący przykład wysoce zintegrowanego rozwiązania z oferty Texas Instruments stanowi układ PGA450-Q1, którego schemat blokowy pokazano na rysunku 1. Układ jest przeznaczony do aplikacji pomiaru odległości metodą ToF – z uwagi na zastosowane rozwiązania techniczne w zakresie zasilania i komunikacji z kontrolerem nadrzędnym, liczba niezbędnych do pracy elementów dyskretnych oraz liczba zewnętrznych połączeń zostały zminimalizowane, przez co front-end świetnie nadaje się do budowy wielokanałowych systemów echolokacyjnych dla branży automotive (czujniki parkowania), dronów (systemy wspomagania lądowania oraz zabezpieczenia antykolizyjne), robotyki mobilnej (detekcja odległości od przeszkód) itp. Układ – według zapewnień producenta – umożliwia pracę w zakresie od 1 do 7 metrów, przy rozdzielczości 1 cm i to zarówno z przetwornikami ultradźwiękowymi o konstrukcji otwartej, jak i zamkniętej (closed-top).

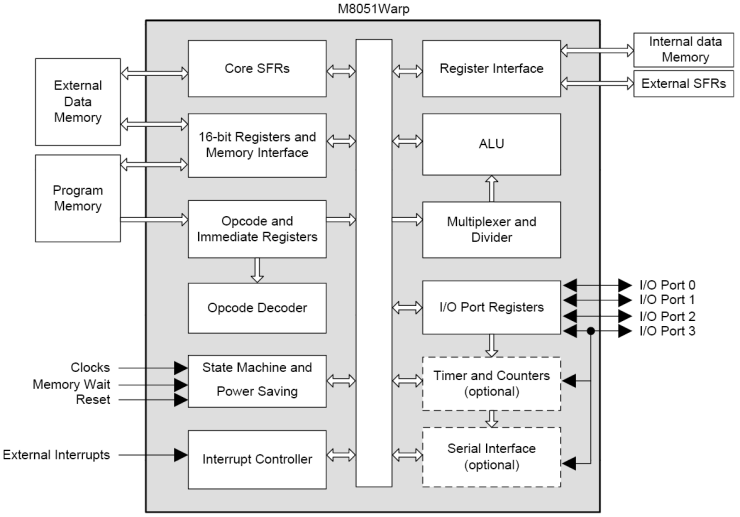

Układ PGA450-Q1 należy do stosunkowo wąskiej (choć z roku na rok coraz szerszej) grupy front-endów wyposażonych we wbudowany mikrokontroler. W tym przypadku mamy do czynienia – co ciekawe – ze architekturą 8051W (8051 WARP), choć nie da się ukryć, że sam MCU stanowi zaledwie niewielki (pod względem funkcjonalnym) fragment struktury układu. W budowie front-endu możemy wyróżnić kilka głównych bloków, które kolejno omówimy.

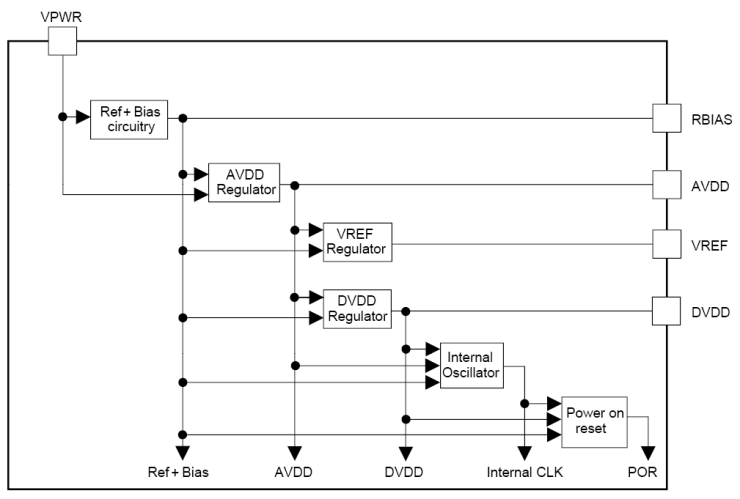

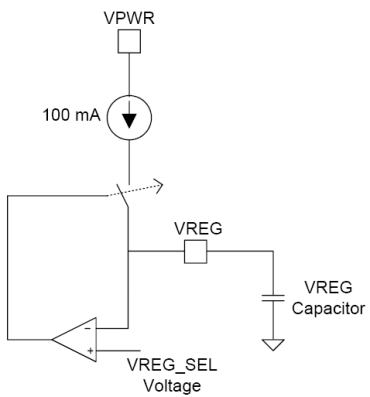

Blok zasilania (rysunek 2) jest złożony z szeregu stabilizatorów napięcia (osobnych dla domeny cyfrowej i analogowej), źródła napięcia odniesienia, układu POR (Power-On Reset) oraz osobnego, impulsowego regulatora napięcia dla uzwojenia pierwotnego transformatora, o konstrukcji znanej z poprzednio opisanych front-endów (rysunek 3).

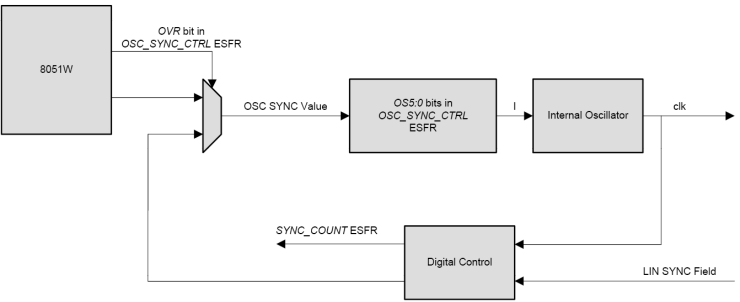

Blok taktowania zawiera 16-megahercowy oscylator wewnętrzny oraz generator przystosowany do pracy z zewnętrznym rezonatorem kwarcowym. Typowa dokładność oscylatora wbudowanego (równa ±4%) może być poprawiona 8-krotnie (do ±0,5%) za pomocą bloku synchronizacji (rysunek 4), który otrzymuje dane z interfejsu LIN jako – teoretycznie – idealny wzorzec częstotliwości (przy założeniu, że ramki zostały odebrane z prędkością dokładnie 19200 bps).

Blok kontrolera cyfrowego stanowi serce całego układu i oprócz wymienionego już mikrokontrolera (odpowiedzialnego za dalsze przetwarzanie danych pomiarowych, obsługę rejestrów konfiguracyjnych, a także komunikację za pośrednictwem transceivera LIN 2.1/SCI lub interfejsu UART – schemat blokowy MCU można zobaczyć na rysunku 5), obejmuje także cyfrowy blok kondycjonowania i przetwarzania sygnałów echa, wspomniany wcześniej układ synchronizacji sygnałów zegarowych, blok pomiaru czasu saturacji przetwornika, generator impulsów pobudzających, a także układ watchdog oraz kontroler protokołu LIN/SCI.

Z częścią cyfrową współpracuje także rozbudowany blok pamięci, w tym wypadku obejmujący aż pięć jej rodzajów:

- FIFO RAM (768 B) – służy jako bufor dla próbek sygnału przetworzonego przez tor DSP,

- Scratchpad RAM (256 B) – główna pamięć operacyjna MCU,

- EEPROM (32 B) – przeznaczona na dane konfiguracyjne,

- OTP (8 kB) – przechowuje kod programu procesora,

- DEVELOPMENT RAM (8 kB) – zastępuje pamięć OTP podczas pracy nad programem MCU.

Tor odbioru echa jest zbudowany na bazie wzmacniacza LNA o wzmocnieniu regulowanym w zakresie od około 100 V/V do 1750 V/V, połączonego bezpośrednio z 12-bitowym przetwornikiem SAR. Niezależnie od głównego toru sygnałowego pracuje komparator, przeznaczony do pomiaru czasu saturacji przetwornika oraz blok zabezpieczeń termicznych z wbudowanym czujnikiem temperatury o czułości 1,75°C/LSB, przeciętnej dokładności równej ±5°C, ale dość szerokim zakresie pracy (od –40 do +140°C).

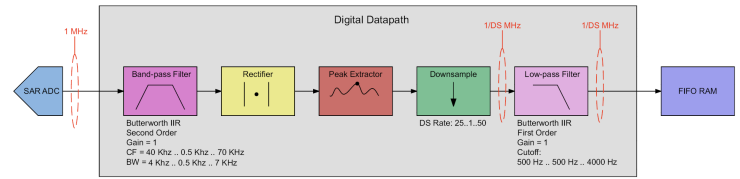

Tor kondycjonowania DSP (rysunek 6) rozpoczyna się tuż za wyjściem przetwornika SAR, będącego źródłem danych pomiarowych o częstotliwości próbkowania równej 1 MHz. Próbki są wstępnie kierowane do filtra pasmowoprzepustowego drugiego rzędu o częstotliwości środkowej ustawianej w zakresie od 40 kHz do 70 kHz i szerokości pasma od 4 kHz do 7 kHz (w obydwu przypadkach z krokiem co 500 Hz).

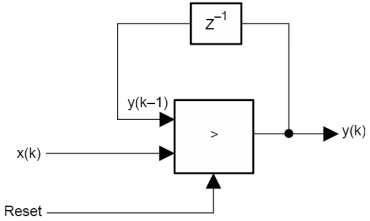

Przefiltrowany sygnał jest następnie prostowany i podawany na prosty detektor szczytowy, przepuszczający nową wartość wejściową tylko pod warunkiem, że aktualna próbka jest większa lub równa poprzedniej wartości wyjściowej detektora (rysunek 7). Ciąg danych wyjściowych detektora szczytowego jest następnie poddawany procesowi podpróbkowania (downsampling) ze współczynnikiem ustawionym w zakresie od 25 do 50 (z krokiem co 1). Tak przygotowany sygnał ponownie ulega filtracji, tym razem z użyciem dolnoprzepustowego filtra pierwszego rzędu o częstotliwości progowej w zakresie od 500 Hz do 4 kHz (z krokiem co 500 Hz). Próbki trafiają następnie do dwuportowego bufora FIFO, skąd odbiera je procesor 8051W i przetwarza zgodnie z zapisanym w pamięci OTP programem.

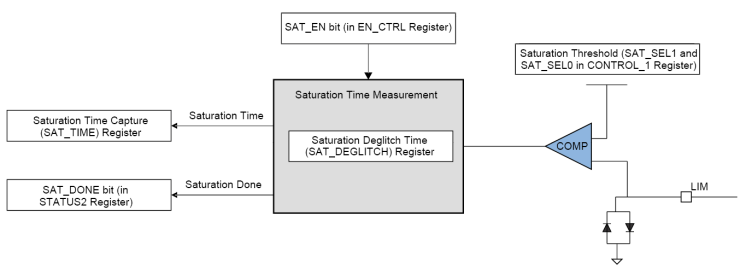

Front-end PGA450-Q1 jest wyposażony w sprzętowy blok pomiaru czasu saturacji przetwornika, którego schemat pokazano na rysunku 8. Układ współpracuje z przetwornikiem za pośrednictwem osobnego wejścia LIM, połączonego – poprzez komparator o progu ustalanym w sekwencji 200, 300, 400, 600 mV – ze specjalnie do tego celu przeznaczonym timerem.

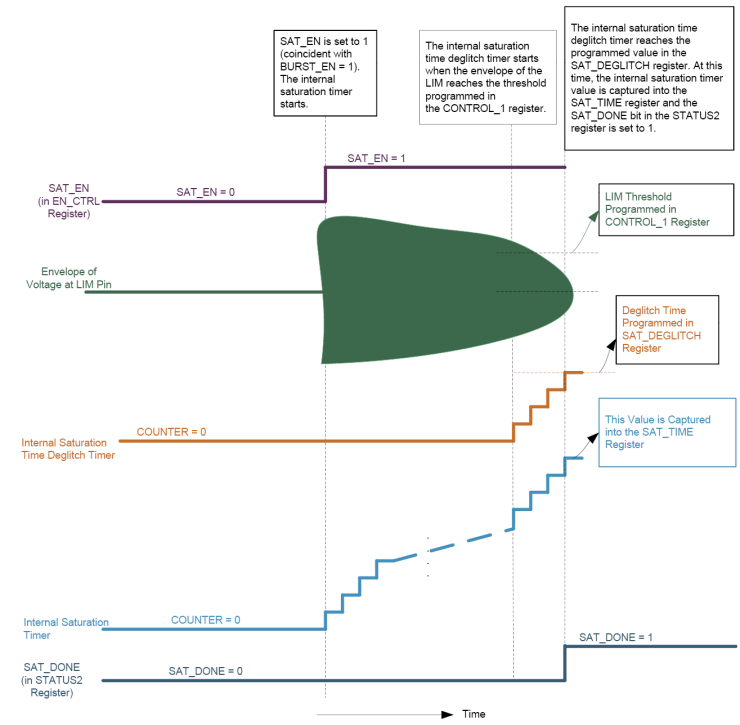

Przykład działania bloku pomiaru czasu nasycenia przetwornika ultradźwiękowego zobrazowano na rysunku 9 – bit SAT_EN jest ustawiany automatycznie w momencie przekroczenia przez napięcie na wejściu LIM zadanego progu detekcji. Wewnętrzny licznik rozpoczyna odmierzanie czasu saturacji i jest zatrzymywany po obniżeniu napięcia na wejściu LIM poniżej progu detekcji, jednak nie bezpośrednio, ale dopiero po upłynięciu dodatkowego czasu, zaprogramowanego w rejestrze SAT_DEGLITCH. Takie rozwiązanie pozwala jednoznacznie stwierdzić fakt wyjścia przetwornika ze stanu nasycenia, nawet podczas pracy z sygnałami silnie zaszumionymi (np. przy dużych wzmocnieniach LNA), przydaje się zatem zwłaszcza w urządzeniach o dużym zasięgu detekcji.

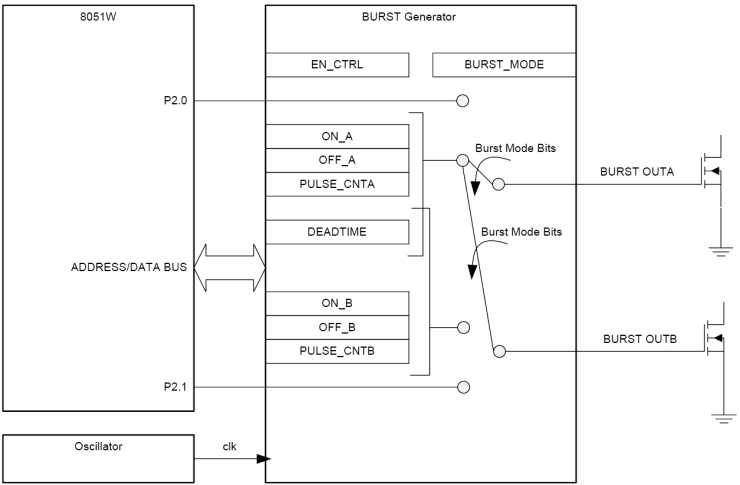

Generator impulsów pokazany na rysunku 10 umożliwia sterowanie wyjściami (więcej informacji na ich temat w dalszej części artykułu) w jednym z trzech możliwych trybów:

- single-ended – jedno z wyjść (OUTA lub OUTB) jest sterowane sprzętowo za pomocą generatora, bazującego na rejestrach EN_CTRL, DEADTIME oraz ON_A, OFF_A oraz PULSE_CNTA w przypadku wyjścia OUTA (lub ON_B, OFF_B oraz PULSE_CNTB w przypadku wyjścia OUTB); w tym samym czasie drugie wyjście można obsługiwać za pomocą oprogramowania wbudowanego mikrokontrolera poprzez jedną z wewnętrznych linii GPIO,

- push-pull – obydwa wyjścia są sterowane z przesunięciem fazowym 180o za pomocą zestawu rejestrów ON_A, OFF_A, DEADTIME, PULSE_CNTA oraz PULSE_CNTB,

- 8051W port drive – obydwa wyjścia są sterowane w pełni programowo za pomocą wewnętrznych linii P2.0 i P2.1 mikrokontrolera, bez użycia sprzętowego generatora i ww. rejestrów.

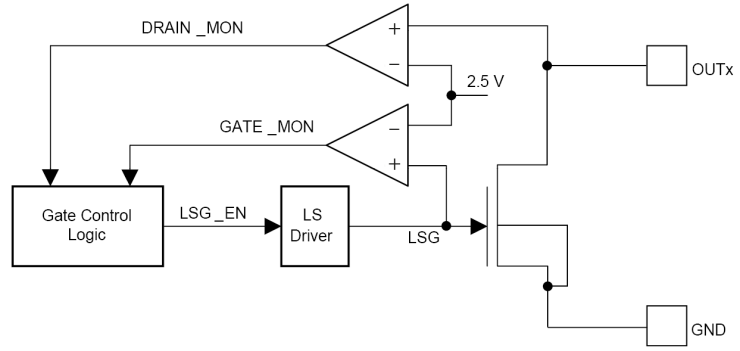

Generator współpracuje ze stopniem wyjściowym złożonym z dwóch bliźniaczych kanałów z wyjściami typu otwarty dren, wyposażonych w podwójne komparatory diagnostyczne (rysunek 11) i przeznaczonych do bezpośredniego sterowania uzwojeniem pierwotnym transformatora dopasowującego. Poszczególne komparatory na bieżąco monitorują potencjały bramek oraz drenów tranzystorów MOSFET. Jeżeli napięcia VGS i VDS będą utrzymywały się na poziomie powyżej 2,5 V przez czas równy lub dłuższy, niż nastawa dokonana za pomocą bitu LS_FAULT_TIMER_SEL (znajdującego się w rejestrze CONTROL_1 – możliwe do ustawienia wartości to 1 μs lub 2 μs), układ automatycznie wyłączy problematyczny tranzystor oraz zgłosi awarię przez podniesienie odpowiedniej flagi w rejestrze STATUS2.

Warto dodać, że front-end PGA450-Q1 ma, także wbudowany przetwornik cyfrowo-analogowy, którego wyjście dostępne jest na linii DAC. W zależności od konfiguracji, wyprowadzenie DAC może zostać przełączone na wyjście wzmacniacza LNA – w ten sposób projektanci układu umożliwili obserwację działania głównego układu pomiarowego, zarówno przed, jak i za cyfrowym blokiem kondycjonowania sygnału echa.

Przykładowy schemat aplikacyjny front-endu PGA450-Q1 pokazano na rysunku 12, doskonale ilustrującym jak prosty może być podstawowy układ pracy opisywanego AFE: szeroki zakres napięć zasilania na linii VPWR (od 7 V do 18 V) ułatwia podłączenie urządzenia np. do samochodowej sieci zasilania, bez konieczności stosowania dodatkowych przetwornic DC/DC czy też zewnętrznych stabilizatorów liniowych.

MSP430FR6043 wyposażony w blok Ultrasonic Sensing Solution

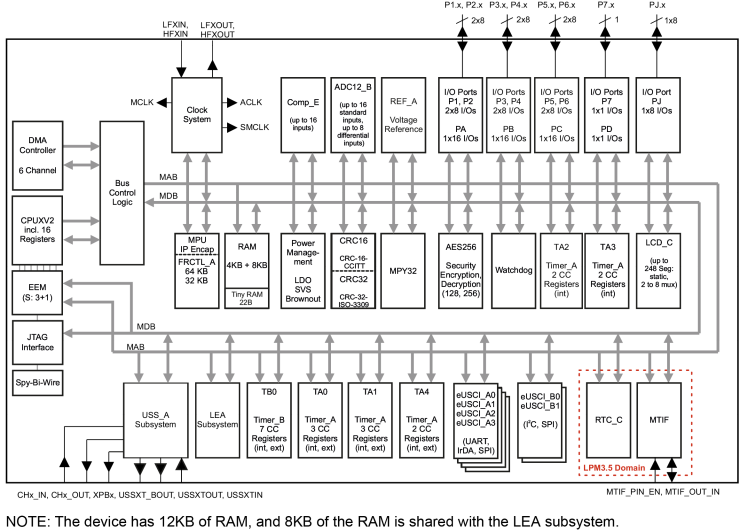

Kolejna propozycja ze stajni Texas Instruments należy do dość szerokiej gamy niskomocowych mikrokontrolerów MSP430 z wbudowanym front-endem ultradźwiękowym, przeznaczonym głównie do przepływomierzy. Z tego też względu zastosowany w omawianej rodzinie układ peryferyjny – nazwany skrótem USS (Ultrasonic Sensing Solution) umożliwia pomiary ToF z bardzo przyzwoitą dokładnością – na poziomie 12,5 ps (!) i rozdzielczość aż 5 ps. Schemat blokowy całego mikrokontrolera z tej serii – na przykładzie modelu MSP430FR6043, został pokazany na rysunku 13.

Jak przystało na „dużych” przedstawicieli rodziny MSP430, także w tym przypadku mamy do czynienia z naprawdę solidnym zestawem uniwersalnych bloków peryferyjnych, w tym z 6-kanałowym kontrolerem DMA, 32-bitowym mnożnikiem sprzętowym, peryferium do obliczania sum kontrolnych CRC, aż 12-kanałowym komparatorem analogowym, 12-bitowym przetwornikiem ADC, koprocesorem kryptograficznym (wspierającym szyfrowanie AES-128 i AES-256) oraz kontrolerem segmentowych wyświetlaczy LCD. W ramach Poradnika Implementacji nie będziemy jednak zajmować się mikrokontrolerem jako takim, skupimy się bowiem wyłącznie na właściwym front-endzie.

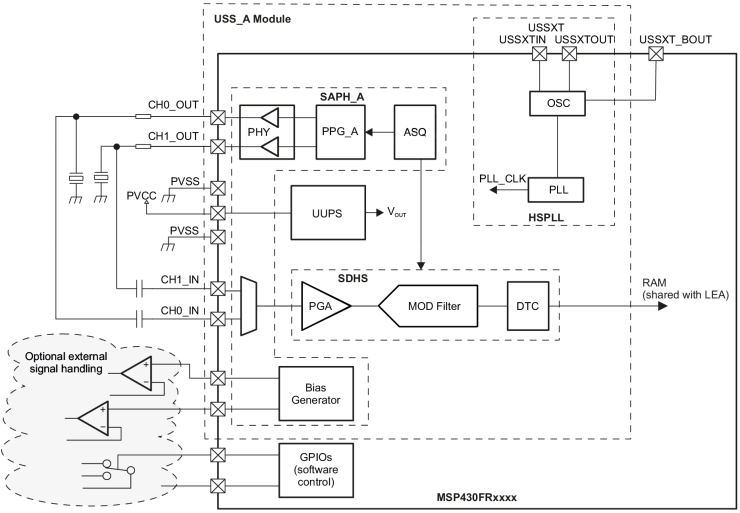

Schemat blokowy modułu USS_A, który jest rozbudowaną wersją oryginalnego USS – został pokazany na rysunku 14. Front-end składa się z kilku zasadniczych bloków:

- UUPS (Universal USS Power Supply) – blok zasilania front-endu, odpowiedzialny za wytwarzanie napięć i prądów odniesienia oraz napięć zasilania wszystkich obwodów układu pomiarowego, a także generowanie sekwencji niezbędnych do prawidłowego załączania i wyłączania USS/USS_A;

- HSPLL (High-Speed PLL) – pętla synchronizacji fazowej o zakresie częstotliwości wyjściowych od 68 do 80 MHz i niskim poziomie jitteru. Sygnałem odniesienia dla pętli HSPLL jest USSXT – specjalny oscylator przeznaczony do pracy z HSPLL, obsługujący zewnętrzne rezonatory ceramiczne bądź kwarcowe o częstotliwości 4 lub 8 MHz;

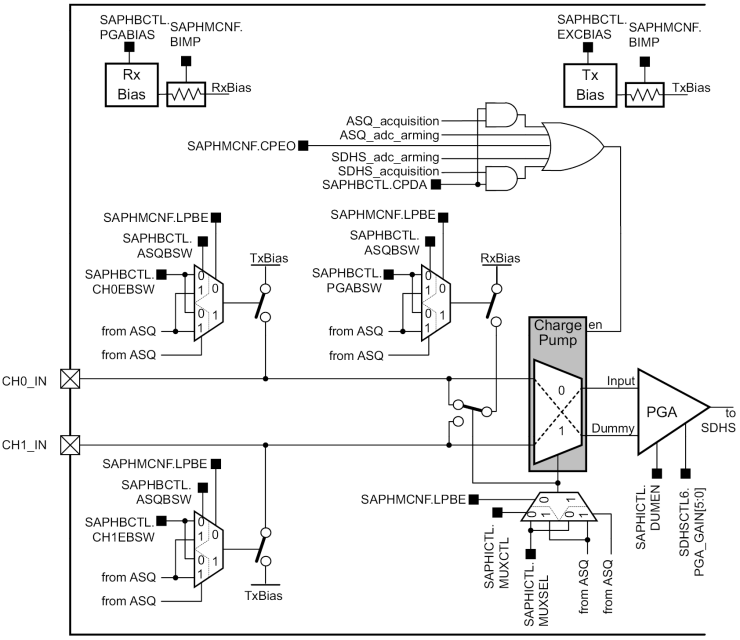

- SAPH/SAPH_A (Sequencer for Acquisition, Programmable Pulse Generator, and Physical Interface) – jak sama nazwa wskazuje, blok ten jest odpowiedzialny za generowanie impulsów wyjściowych oraz akwizycję i kondycjonowanie sygnału echa. Wyjścia sterujące przetwornikami (CH0_OUT i CH1_OUT) zapewniają niską impedancję wewnętrzną na poziomie 3...4 Ω. Oprócz wspomnianego wcześniej sekwencera akwizycji (ASQ – Acquisition Sequencer), SAPH/SAPH_A zawiera także blok programowalnego generatora impulsów (PPG/PPG_A) oraz stopień wyjściowy, oznaczony skrótem PHY (Physical Interface). Dodatkowe wyjścia XPB0/1, dostępne w wersji SAPH_A, umożliwiają podanie napięć polaryzujących dla zewnętrznych obwodów, np. dodatkowych wzmacniaczy wejściowych (LNA) lub wyjściowych.

- SDHS (Sigma-Delta High Speed) – szybki przetwornik ADC, wyposażony we wbudowany wzmacniacz PGA oraz własny kontroler DMA (nazwany przez producenta mianem DTC – Data Transfer Controller).

Podobnie, jak w przypadku opisanego wcześniej układu PGA450-Q1, także tutaj mamy do czynienia z trzema trybami pracy – front-end może pracować niejako autonomicznie (czyli z automatyczną sekwencją – normalną bądź energooszczędną, w obu przypadkach obsługiwaną przez blok ASQ), jak i z pełną kontrolą programową, ułatwiającą tworzenie oprogramowania czy też realizację zadań autodiagnostycznych w ramach docelowego urządzenia.

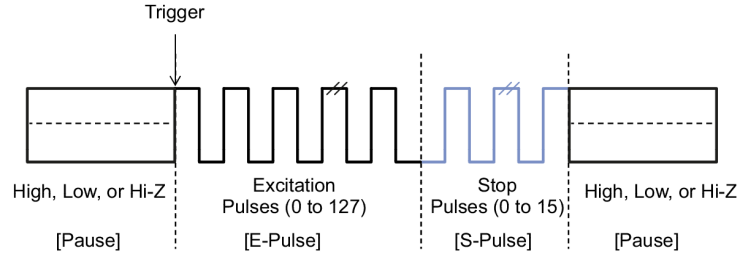

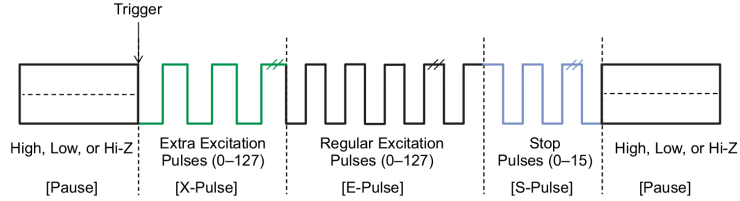

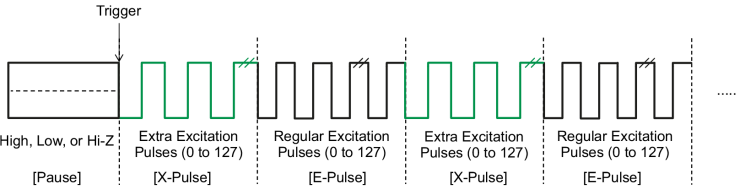

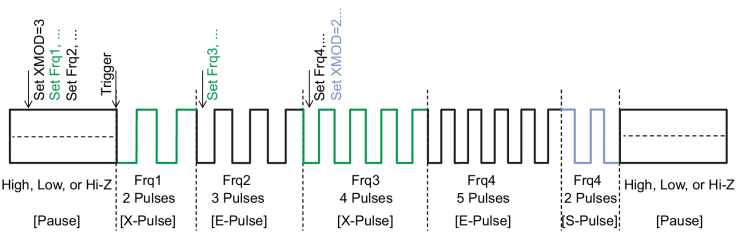

Podczas gdy podstawowa wersja USS zawiera blok PPG, umożliwiający pracę tylko z sygnałami pobudzającymi o jednej, określonej programowo częstotliwości – single tone (rysunek 15), to rozszerzona odmiana modułu generatora – PPG_A – pozwala także na generowanie przebiegów określanych jako dual tone – ton podwójny (rysunek 16), trill tone – tryl (rysunek 17) oraz multi tone – chirp (rysunek 18).

Rozbudowany blok toru wejściowego (rysunek 19) zawiera m.in. przełączniki ustalające warunki polaryzacji wejść, wzmacniacz PGA o wzmocnieniu od –6,5 dB do 30,8 dB, a także… pompę ładunkową, generującą napięcie zasilania dla głównego multipleksera. Napięcie to jest równe 3,2 V i powstaje w wyniku podwojenia napięcia wyjściowego stabilizatora LDO modułu USS. Wyjście PGA jest skierowane na modulator delta-sigma trzeciego rzędu, współpracujący z zespołem filtrów CIC, zapewniających decymację na poziomie od 10 do 160. Modulator wraz z filtrami tworzy wysokiej jakości przetwornik ADC o częstotliwości próbkowania do 8 MSps, z którego dane trafiają do 64-pozycyjnego bufora. Zastosowanie wspomnianego wcześniej kontrolera DTC wraz z buforem pozwala na bezstratną akwizycję danych z szybkością nieosiągalną dla głównego kontrolera DMA – układ jest zatem zoptymalizowany pod kątem maksymalnej wydajności pomiarowej przy dość ograniczonych możliwościach 16-megahercowego, energooszczędnego rdzenia RISC.

NCV75215 produkcji onsemi

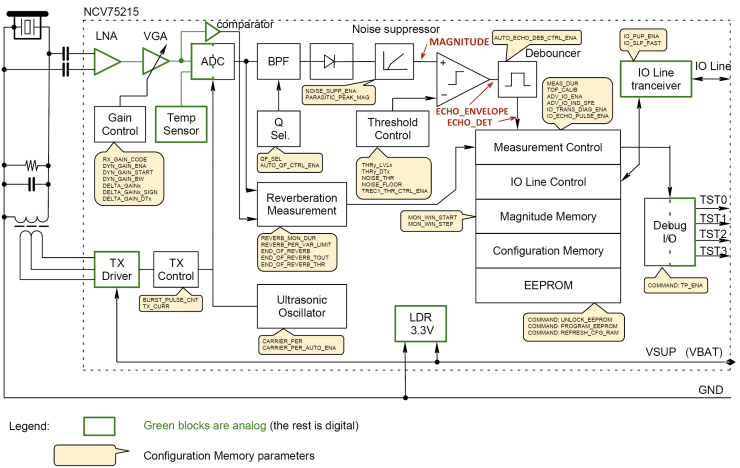

Ostatnim front-endem, który pozostał nam do omówienia w tej części naszego cyklu, jest propozycja firmy onsemi – NCV75215, jedyny w jej ofercie układ AFE przeznaczony do aplikacji ultradźwiękowych. NCV75215 umożliwia pomiary dystansu w zakresie od 0,25 m do 4,5 m za pomocą przetworników o częstotliwości rezonansowej od 35 kHz do 90 kHz. Schemat funkcjonalny front-endu NCV75215 pokazano na rysunku 20.

Podobnie jak w przypadku opisanych wcześniej propozycji Texas Instruments, także ten układ bazuje w większości na cyfrowym przetwarzaniu danych pomiarowych, podczas gdy domena analogowa została zredukowana do minimum. Tor odbiorczy rozpoczyna się kaskadowym połączeniem niskoszumnego wzmacniacza LNA oraz przestrajanego z krokiem 0,476 dB/LSB wzmacniacza VGA. 7-bitowe pole konfiguracyjne pozwala na osiągnięcie zakresu wzmocnienia całkowitego równego 50...110 dB. Tuż za sekcją wzmacniaczy znajduje się (połączony także z wbudowanym czujnikiem temperatury) przetwornik ADC – co ciekawe, producent nie podaje żadnych szczegółowych informacji na temat jego parametrów. Sygnał z wyjścia VGA trafia także na komparator, służący do pomiaru czasu rezonansu własnego przetwornika (rozwiązanie to jest zbliżone do obecnego w PGA450-Q1 bloku pomiaru czasu saturacji).

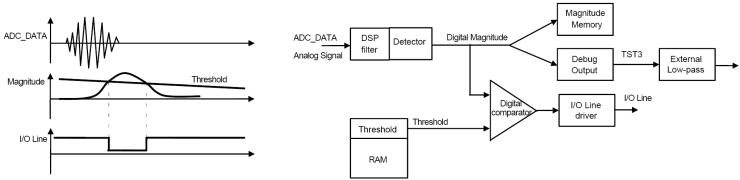

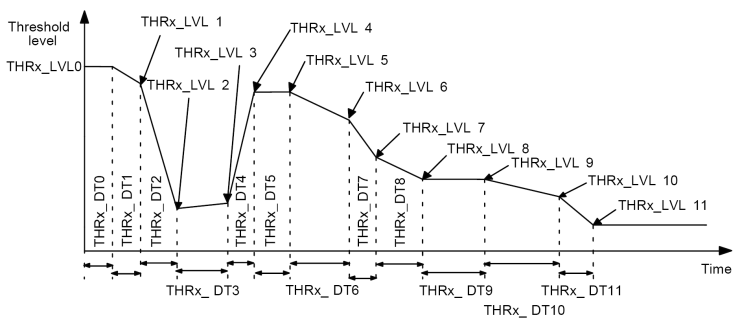

Koncepcja cyfrowego kondycjonowania sygnałów jest także nieco zbliżona do technik zastosowanych w AFE marki Texas Instruments – schematycznie pokazano ją na rysunku 21. Dane z przetwornika ADC trafiają najpierw do pasmowoprzepustowego filtra cyfrowego, następnie do detektora (prostownika) i po odfiltrowaniu szumów są porównywane w komparatorze cyfrowym – co ciekawe, producent użył uderzająco podobnych rozwiązań w stosunku do bardziej zaawansowanych front-endów TI. Po pierwsze, próg odniesienia dla komparatora jest zmienny w czasie i w pełni programowalny za pomocą obszernego zestawu rejestrów, ustalających długości poszczególnych odcinków czasowych oraz kolejne wartości progu (rysunek 22).

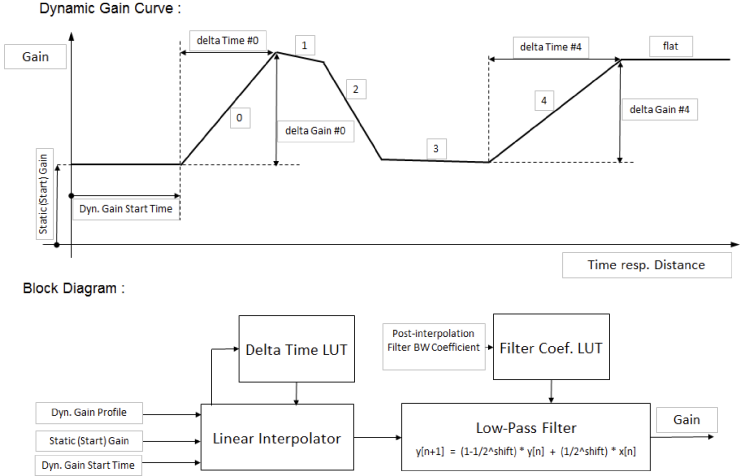

Po drugie – zbliżone rozwiązanie zastosowano też w przypadku wzmocnienia (rysunek 23), choć w przypadku omawianego front-endu producent zadbał o „wygładzenie” cyfrowego przebiegu sterującego wzmacniaczem LNA – funkcja sklejana, utworzona za pomocą rejestrów delta Time i delta Gain, jest dodatkowo przetwarzana za pomocą filtra dolnoprzepustowego – oczywiście już za blokiem interpolatora, zamieniającego definicje przedziałów czasowych i poszczególnych przyrostów wzmocnienia, na jego liniowe zmiany w funkcji czasu.

Konstrukcja układu NCV75215, jest – podobnie, jak w przypadku PGA450-Q1 – silnie zoptymalizowana pod kątem ogólnego uproszczenia konstrukcji urządzenia bazującego na omawianym front-endzie, a także minimalizacji liczby elementów zewnętrznych. Stąd też na schemacie aplikacyjnym (rysunek 24) zobaczymy raczej niewiele komponentów dyskretnych – oprócz transformatora dopasowującego mamy zatem trzy rezystory i cztery kondensatory w obwodzie toru wejściowego oraz kilka dodatkowych elementów formujących obwód zasilania i otoczenie dwukierunkowej linii komunikacyjnej interfejsu szeregowego (IO). Co więcej – konstruktorzy z firmy onsemi zadbali nawet o uproszczenie podłączenia uzwojenia pierwotnego transformatora, przewidując trzy linie (DRVA, DRVB i DRVC) do bezpośredniego podłączenia końcówek uzwojenia oraz jego środkowego odczepu.

Podsumowanie

W kolejnym odcinku Poradnika Implementacji omówiliśmy trzy przykłady front-endów ultradźwiękowych – dwa z nich, silnie zintegrowane, przeznaczone do autonomicznej pracy w wielokanałowych systemach dalmierzy ultradźwiękowych (głównie w aplikacjach czujników parkowania) oraz jeden, będący wbudowanym blokiem peryferyjnym zaawansowanego mikrokontrolera metrologicznego, opracowanego pod kątem nowoczesnych przepływomierzy. Jak widać, producenci stosują często bardzo zbliżone rozwiązania techniczne, przerzucając większość operacji (w zakresie przetwarzania sygnału echa oraz generacji sygnałów pobudzających przetwornik) na cyfrową część sprzętową układu lub oprogramowanie. Stopniowo maleje zatem udział bloków analogowych w strukturach współczesnych układów AFE – i choć nie można przecenić zasług wysokiej jakości wzmacniaczy wejściowych czy przetworników ADC i DAC, to bez wątpienia trend cyfryzacji znakomitej większości funkcjonalności AFE będzie z czasem stawał się coraz wyraźniejszy.

inż. Przemysław Musz, EP

Zaloguj

Zaloguj