Podstawowe środowisko pomiarowe

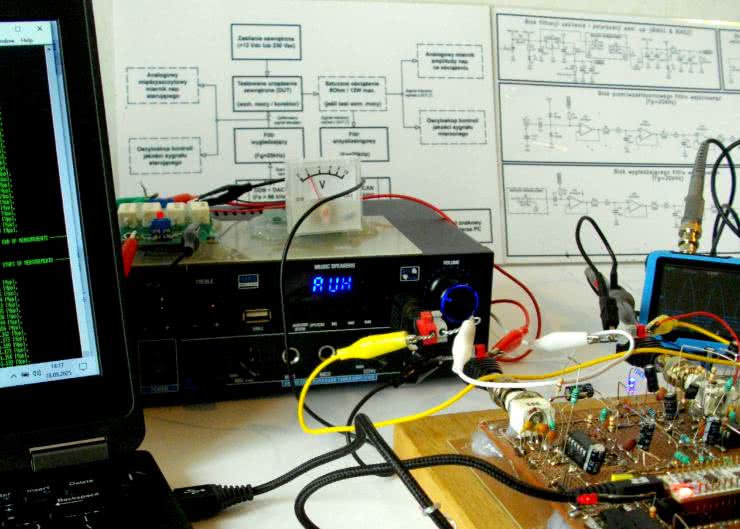

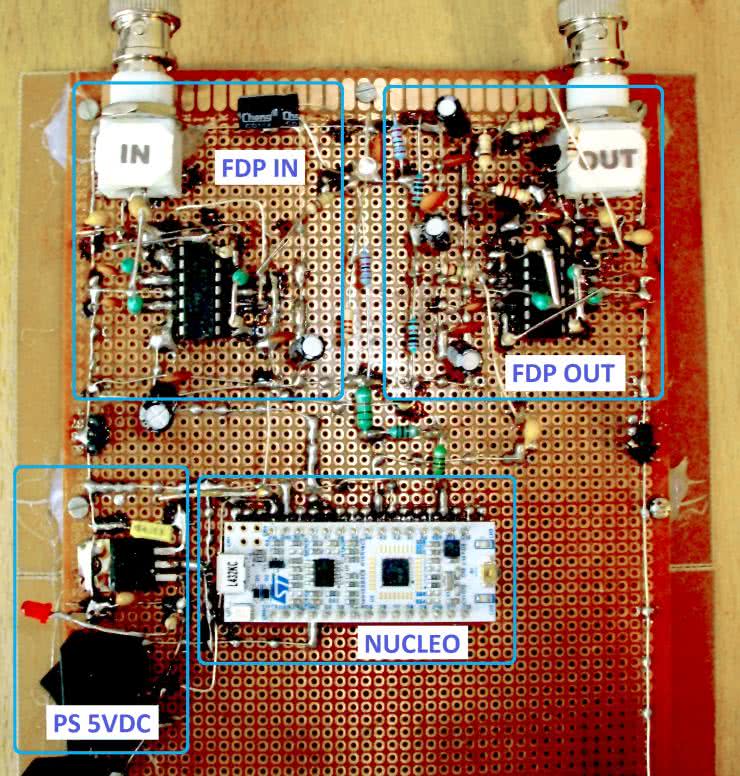

Część sprzętowa podstawowego środowiska pomiarowego, wykorzystanego do przeprowadzenia opisanych dalej testów, została oparta na koncepcji platformy sprzętowej zaimplementowanej w testach filtrów cyfrowych FIR oraz filtrów IIR, przedyskutowanych w poprzednich dwóch częściach tego cyklu publikacji. W szczególności do cyfrowego przetwarzania sygnałów zastosowano ponownie moduł NUCLEO z mikrokontrolerem STM32L432KC oraz bloki analogowych filtrów: wygładzającego i antyaliasingowego, które zostały istotnie zmodernizowane.

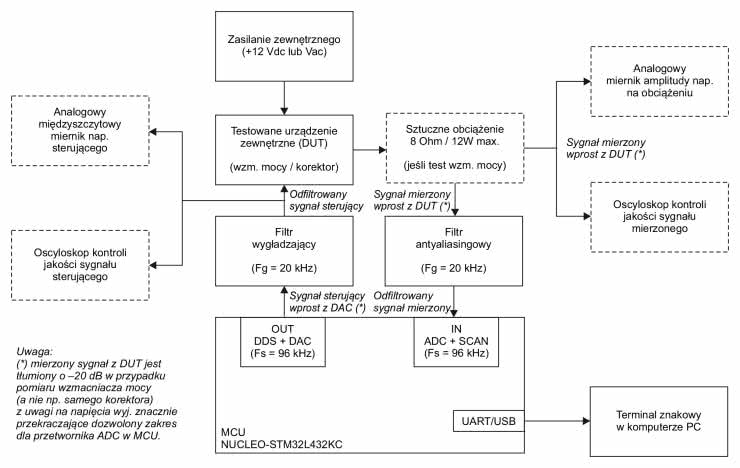

Schemat blokowy sprzętowej części podstawowego środowiska pomiarowego pokazano na rysunku 69. Z zasobów oferowanych przez mikrokontroler, oczywiście poza jednostką centralną i układami taktującymi, wykorzystano przede wszystkim: przetwornik cyfrowo-analogowy (DAC), przetwornik analogowo-cyfrowy (ADC) oraz blok interfejsu UART – który za pomocą dostępnego na zastosowanej płytce NUCLEO konwertera UART-USB – posłużył do wyprowadzania rezultatów pomiarów na terminal znakowy w komputerze PC. Algorytm i dalsze szczegóły działania zaimplementowanego oprogramowania sterującego pracą mikrokontrolera zostały opisane w końcowej części artykułu. W tym miejscu skupiono się przede wszystkim na sprzętowych aspektach funkcjonowania omawianego środowiska pomiarowego. Na wspomnianym wcześniej rysunku 69 zaprezentowano kilka bloków funkcjonalnych, połączonych strzałkami, które ilustrują kierunki przepływu sygnałów pomiędzy nimi. Bloki narysowane linią ciągłą reprezentują niezbędne elementy minisystemu pomiarowego, natomiast bloki nakreślone linią przerywaną obrazują elementy opcjonalne. Do bloków obowiązkowych, oprócz wymienionego wcześniej, kluczowego w tym zastosowaniu, modułu NUCLEO wraz z towarzyszącymi filtrami analogowymi, należą oczywiście: blok testowanego urządzenia zewnętrznego DUT (ang. Device Under Test) oraz blok zewnętrznego zasilania przedmiotowego urządzenia DUT (+12 VDC albo 230 VAC – w zależności od konkretnego DUT). Jakkolwiek w przeprowadzonych doświadczeniach pomiarowych przetestowano także jedno urządzenie aktywne, które z zasady nie wymagało zasilania. Do obligatoryjnych bloków w przyjętym rozwiązaniu systemu pomiarowego należy m.in. terminal znakowy w komputerze PC, na który mikrokontroler STM32L432KC wysyłał przez interfejs UART/USB rezultaty pomiarów w prostym formacie tekstowym (do dalszej obróbki – np. w arkuszu kalkulacyjnym lub za pomocą dedykowanego skryptu w języku perl, python itp.)

Do bloków opcjonalnych należy w pierwszej kolejności sztuczne obciążenie 8 Ω/12 W (max.), które było niezbędne wyłącznie do testowania wzmacniaczy mocy m.cz., ale nie było potrzebne np. do testów samodzielnego korektora audio (bez wzmacniacza mocy). Mniej istotnymi, chociaż w ocenie autora tego opracowania, bardzo przydatnymi w trakcie przeprowadzonych pomiarów blokami, są: analogowe, zgrubne mierniki napięcia sterującego oraz napięcia na obciążeniu (wraz z dedykowanymi układami prostowniczymi) a także oscyloskopy, przeznaczone do wizualnej kontroli jakości tychże napięć. Sygnał wytworzony w wewnętrznym, programowym generatorze DDS, pracującym z częstotliwością próbkowania Fs=96 kHz, przekonwertowany na sygnał analogowy w przetworniku DAC (zlokalizowanym w MCU STM32L432KC na płytce NUCLEO) jest podawany na filtr wygładzający górnej częstotliwości granicznej Fg=20 kHz. Stamtąd dalej trafia na wejście testowanego urządzenia zewnętrznego (DUT). Z wyjścia urządzenia DUT sygnał mierzony dociera na wejście filtra antyaliasingowego (istotnego m.in. z uwagi na możliwość powstawania w DUT pasożytniczych częstotliwości harmonicznych) i dalej na wejście przetwornika ADC (także zlokalizowanego w MCU STM32L432KC na płytce NUCLEO), pracującego z tą samą częstotliwością próbkowania (Fs=96 kHz). W przypadku pomiaru sygnałów na wyjściu wzmacniaczy mocy, przebiegi te były wstępnie tłumione o –20 dB, by nie przekroczyły dozwolonego zakresu przetwarzania napięć przez przetwornik ADC. Następnie zmierzone przez ADC próbki sygnału były skanowane i analizowane pod kątem wyznaczenia ich minimalnych i maksymalnych wyników (osobno dla każdej częstotliwości pomiarowej Fpom), wartości skrajne były z kolei wykorzystywane do wyliczenia napięcia [Vp-p] na wyjściu testowanego DUT. Finalnie, kolejne pary wartości: (Fpom [Hz], Upom [Vp-p]), gdzie zachodziło Upom=f(Fpom), były wysyłane do terminala tekstowego w komputerze PC – celem ich wizualizacji i dalszej obróbki przez operatora opisanego minisystemu pomiarowego.

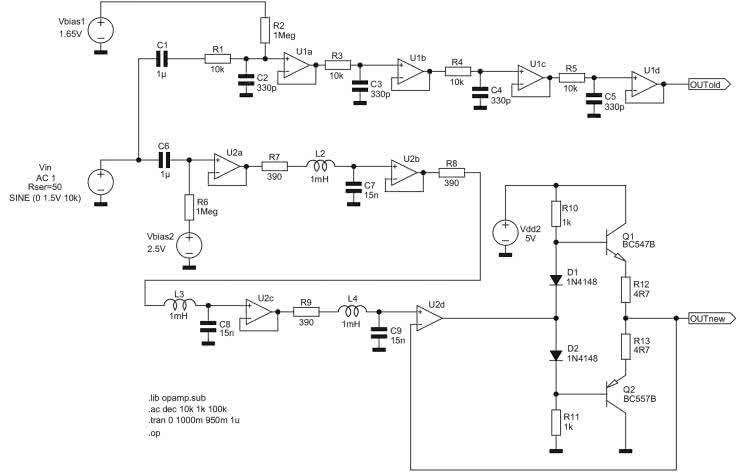

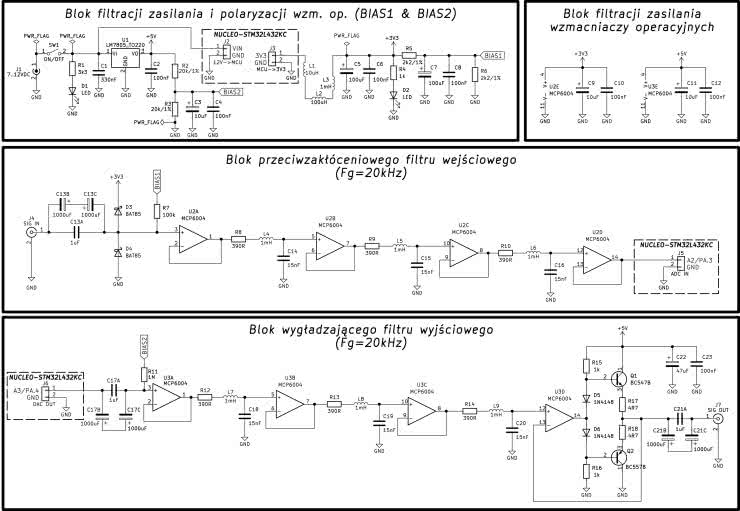

Jak wspomniano wcześniej, wykorzystane tutaj środowisko pomiarowe w części sprzętowej zostało w znacznej mierze oparte o koncepcję platformy sprzętowej, użytej w testach filtrów cyfrowych, jednak istotnej modernizacji zostały poddane przede wszystkim bloki analogowych filtrów: wygładzającego i antyaliasingowego. W szczególności czterostopniowe, połączone łańcuchowo, proste filtry RC (czwartego rzędu) zastąpiono trzystopniowymi, połączonymi łańcuchowo filtrami RLC (szóstego rzędu). Zabieg ten pozwolił jednocześnie zwiększyć impedancje wejściowe omawianych bloków filtrów (z uwagi na brak obciążających źródła sygnałów członów RC na wejściach filtrów), a także poprawić stromość opadania ich charakterystyk częstotliwościowych w okolicach górnych częstotliwości granicznych Fg=20 kHz tychże filtrów. Dodatkowo na wyjściu układu filtra wygładzającego dodano niskoimpedancyjny wtórnik z komplementarną parą tranzystorów, pracującą w klasie 2×AB. Zabieg ten miał na celu zmniejszenie impedancji wyjściowej i zwiększenie wydajności prądowej układu, którego przeznaczeniem było wysterowanie testowanego urządzenia zewnętrznego DUT o nieznanej impedancji wejściowej. Rysunek 70 prezentuje schematy dwóch wariantów omawianych filtrów dolnoprzepustowych, przygotowanych na potrzeby wykonania symulacji porównawczych w środowisku LTspice: starej wersji „4×RC” z filtrów cyfrowych oraz nowej wersji „3×RLC” z omawianego tutaj minisystemu pomiarowego.

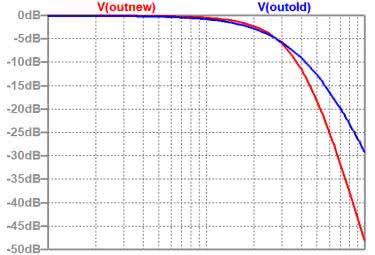

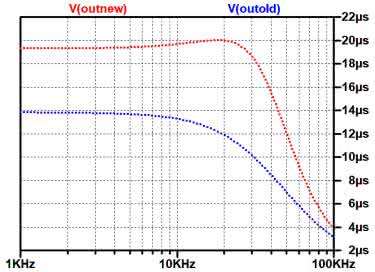

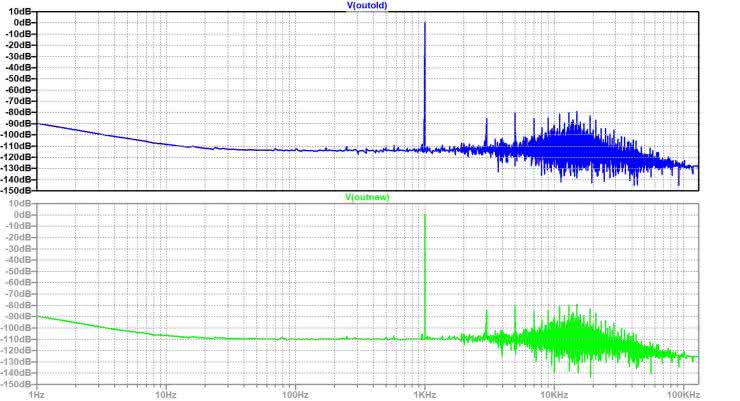

Oba tory filtrów były pobudzane z tego samego źródła sygnału sinusoidalnego, a ich napięcia wyjściowe były dostępne na portach oznaczonych etykietami: OUTold oraz OUTnew. Na rysunku 71 przedstawiono charakterystyki amplitudowe przenoszenia obu torów w zakresie częstotliwości od F=1 kHz do F=100 kHz.

Rezultaty symulacji komputerowych jednoznacznie potwierdziły zasadność wprowadzonych modyfikacji: zmodyfikowany projekt filtra miał nieco bardziej płaską charakterystykę amplitudową w pasmie przenoszenia, a także oferował znaczącą poprawę tłumienia poza tym pasmem (przy niezmiennie zachowanej monotoniczności tej charakterystyki). Z kolei na rysunku 72 zaprezentowano charakterystyki opóźnienia grupowego obu filtrów.

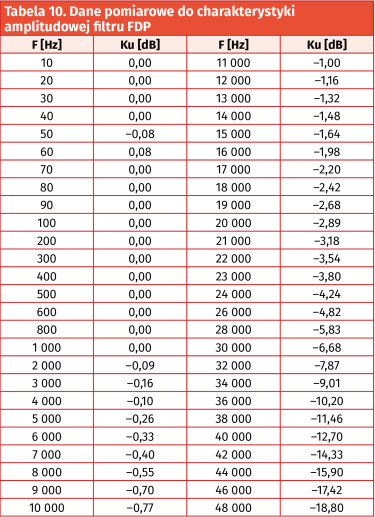

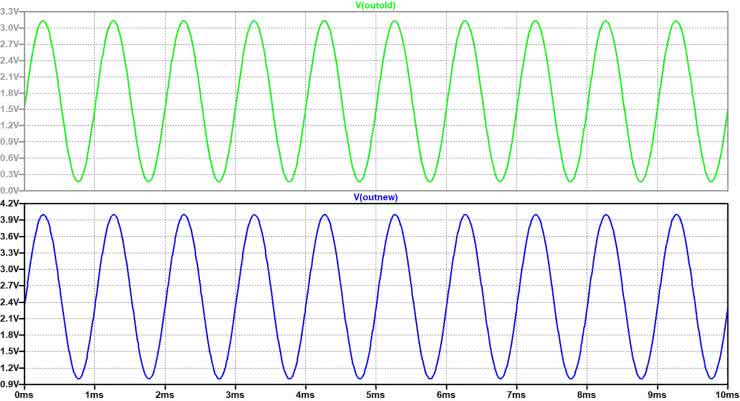

Co prawda nowe rozwiązanie wprowadza nieco większe opóźnienia grupowe do toru przetwarzania sygnału, jednak nie ma to żadnego istotnego wpływu na uzyskiwane w systemie pomiarowym wyniki. Natomiast opóźnienie grupowe w pasmie przenoszenia dla nowego rozwiązania filtra jest nawet nieco bardziej wyrównane, niż to miało miejsce w przypadku filtra stosowanego wcześniej, co należy uznać za korzystną zmianę. Rysunek 73 prezentuje wykres uzyskanej pomiarowo charakterystyki amplitudowej jednego z nowo zaprojektowanych filtrów (dane źródłowe do tego wykresu zawiera tabela 10).

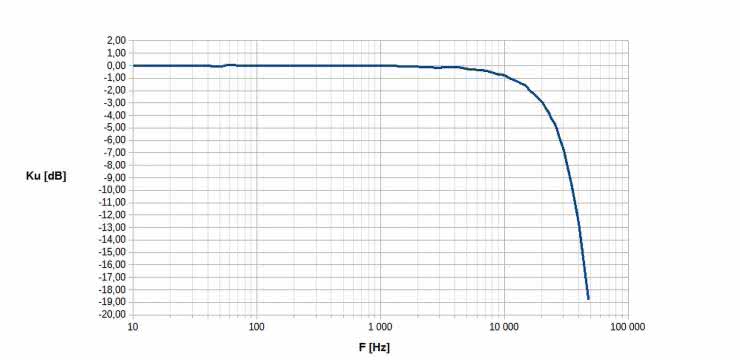

Jak nie trudno zauważyć, obie charakterystyki (symulowana oraz zdjęta pomiarowo) są ze sobą zgodne, co dodatkowo potwierdza poprawność nowego projektu pomocniczych filtrów analogowych. Ponieważ w torze filtra wygładzającego na wyjściu dodano wtórnik z komplementarną parą tranzystorów bipolarnych (stopień z zasady nieliniowy) pracujących w klasie 2×AB, autor postanowił dodatkowo przeprowadzić symulację komputerową w dziedzinie czasu. I tak oba tory filtrów, stary i nowy, były pobudzane tym samym sygnałem sinusoidalnym Vin o amplitudzie 1,5 V (3,0 Vp-p) i częstotliwości F=1 kHz. Rysunek 74 prezentuje 10-cio milisekundowe wycinki sinusoidalnych przebiegów napięć wyjściowych V(OUTold) oraz V(OUTnew).

Co prawda wizualna ocena ich czystości widmowej nie budzi żadnych zastrzeżeń, ale powszechnie przyjmuje się, że harmoniczne zniekształcenia nieliniowe przebiegów sinusoidalnych na poziomie ≤5% są niezwykle trudne do wychwycenia gołym okiem. Mając na uwadze szczególnie wysokie wymagania jakościowe stawiane torom pomiarowym, uzyskane pełne, jednosekundowe przebiegi wyjściowe V(OUTold) oraz V(OUTnew) poddano dodatkowo obliczeniowej analizie Fouriera, której wyniki pokazano na rysunku 75. Wnioski z nich są takie, że przyjmując główne składowe widma obu przebiegów V(OUTold) oraz V(OUTnew) na umownym poziomie 0 dB, w obu przypadkach otrzymano widma sygnałów pasożytniczych (zniekształceń nieliniowych) o bardzo zbliżonych kształtach i na poziomach praktycznie nieprzekraczających –80 dBc (względem poziomu podstawowej harmonicznej). Dodatkowo w widmie zakłóceniowym występują praktycznie jedynie nieparzyste harmoniczne (3 kHz, 5 kHz, 7 kHz, …), co korzystnie świadczy o symetrycznej pracy obu instancji filtrów (także nowego projektu – ze wzmacniaczem tranzystorowym na wyjściu).

Rysunek 76 przedstawia schemat elektryczny opracowanych filtrów wraz z towarzyszącymi obwodami zapewniającymi prawidłowe zasilanie całego systemu pomiarowego. Układ zasilany jest z zewnętrznego źródła stałoprądowego o napięciu Uzas=7...12 VDC i wydajności prądowej nie mniejszej niż 1 A (bezpieczna wartość) przez złącze koncentryczne J1. Zasilanie jest załączane przełącznikiem SW1, a obecność napięcia sygnalizuje dioda LED D1, której maksymalny prąd roboczy ogranicza rezystor R1. Napięcie Uzas jest podawane wprost na złącze wejścia zewnętrznego zasilania na płytce NUCLEO, oznaczone na schemacie jako J2 (piny VIN oraz GND na płytce NUCLEO), a także na wejście stabilizatora scalonego U1 (LM7805), który – wraz z rekomendowanymi przez producenta tego układu kondensatorami C1 i C2 – zapewnia napięcie stabilizowane +5 VDC, niezbędne do zasilenia niskoimpedancyjnego wtórnika wyjściowego z komplementarną parą tranzystorów Q1-Q2. Elementy R2, R3, C3 i C4 zapewniają wysokostabilne, precyzyjne i dobrze odfiltrowane źródło napięcia +2,5 VDC (oznaczone etykietą BIAS2 na omawianym schemacie), niezbędne do prawidłowej polaryzacji wzmacniaczy operacyjnych i wspomnianego stopnia wyjściowego w bloku wygładzającego filtra wyjściowego. Aby uprościć omawianą konstrukcję, napięcie zasilające +3,3 VDC, niezbędne do prawidłowego zasilania bloku przeciwzakłóceniowego filtra wejściowego, zostało pobrane wprost z płytki NUCLEO (piny 3V3 i GND, oznaczone jako złącze J3 na schemacie). Jest to jak najbardziej prawidłowe rozwiązanie, zgodne z zaleceniami producenta zastosowanej płytki NUCLEO (obciążenie prądowe wyjścia 3V3 modułu NUCLEO przez zaimplementowane obwody zewnętrzne jest znacznie poniżej wartości dozwolonych, podanych w nocie katalogowej tegoż modułu). Napięcie zasilające +3,3 VDC zostało wyprowadzone poprzez rozbudowany bierny zespół filtra dolnoprzepustowego z dławikami L1, L2 i L3 oraz kondensatorami C5 i C6, by zakłócenia impulsowe z modułu NUCLEO nie przedostawały się do obwodów zasilania i polaryzacji wzmacniaczy operacyjnych U2A...U2D. Dioda LED D2 z rezystorem szeregowym R4 sygnalizuje obecność zasilania +3,3 VDC w minisystemie pomiarowym. Natomiast precyzyjne rezystory R5 i R6 z pojemnościami C7 i C8, blokującymi do masy szczątkowe zakłócenia impulsowe, realizują układ dzielnika oporowego i dostarczają napięcie +1,65 VDC (na schemacie oznaczone etykietą BIAS1) polaryzujące wzmacniacze operacyjne U2A...U2D. Pojemności C9...C12 blokują zakłócenia i szumy w napięciach +3,3 VDC oraz +5 VDC zasilania wzmacniaczy operacyjnych U2 i U3 i zgodnie z obowiązującymi regułami projektowania, są umieszczone w bezpośrednim sąsiedztwie wyprowadzeń zasilania (piny nr 4) i masy (piny nr 11) wymienionych wcześniej układów scalonych.

Sygnał mierzony jest wprowadzany na wejście bloku przeciwzakłóceniowego filtra wejściowego poprzez koncentryczne złącze BNC J4, które jest sprzężone z resztą układu zespołem kondensatorów C13A/C13B/C13C (rozwiązanie podyktowane potrzebą zapewnienia odpowiednio niskiej impedancji sprzężenia pojemnościowego w całym pasmie akustycznym). W przypadku pomiaru urządzeń DUT (przede wszystkim wzmacniaczy), w których żadne z wyprowadzeń wyjściowych (mocy) nie pracuje na potencjale masy badanego układu, może być konieczne dodatkowe zastosowanie szerokopasmowego transformatora separującego. Aspekt ten został poruszony szczegółowo w dalszej części tego opracowania.

Diody Schottky’ego D3 i D4 mają zadanie zapobiegać przesterowaniu (czy wręcz uszkodzeniu) obwodu pomiarowego przez sygnał wejściowy o zbyt dużej amplitudzie. Rezystor R7 podaje napięcie BIAS1, polaryzujące wejście nieodwracające wzmacniacza operacyjnego U2A i – wobec stałoprądowych sprzężeń pomiędzy kolejnymi stopniami wtórnikowymi ze wzmacniaczami operacyjnymi U2A...U2D – ustala także punkty pracy wszystkich tych wzmacniaczy. Pomiędzy czterema stopniami wtórników-separatorów z U2A...U2D wstawiono trzy czwórniki RLC (z elementami: R8-L4-C14, R9-L5-C15 oraz R10-L6-C16), które stanowią dolnoprzepustowe filtry RLC drugiego stopnia. Ostatecznie uzyskano wypadkowy, dolnoprzepustowy filtr RLC szóstego stopnia – zgodnie z koncepcją i charakterystykami przedstawionymi na rysunkach 70...73 – omówionymi szczegółowo we wcześniejszej części artykułu. Odfiltrowany dolnoprzepustowo sygnał z wyjścia wzmacniacza operacyjnego U2D jest podawany wprost na pin A2 modułu NUCLEO (sprzężenie stałoprądowe – złącze oznaczone na schemacie jako J5), czyli pin PA.3 mikrokontrolera STM32L432KC, który z kolei jest fizycznym wejściem przetwornika ADC. Warto w tym miejscu podkreślić fakt, że zastosowane sprzężenie stałoprądowe sprawia, że stałe napięcie polaryzujące BIAS1 przeniesione wprost na wejście ADC, ustala punkt pracy przetwornika w bardzo bliskim sąsiedztwie połowy (środka) zakresu przetwarzania tego przetwornika.

Na wejście bloku wygładzającego filtra wyjściowego podano sygnał z wyjścia przetwornika DAC mikrokontrolera (złącze NUCLEO oznaczone na schemacie jako J6 – pin A3 NUCLEO i jednocześnie pin PA.4 MCU). W tym przypadku zastosowano sprzężenie pojemnościowe (kondensator C17), ponieważ zakres przetwarzania DAC w MCU, mieszczący się w zakresie od 0 V do 3,3 V (napięcie zasilania MCU), jest mniejszy od napięcia zasilania bloku wygładzającego filtra wyjściowego (+5 V). Punkt pracy tego bloku jest ustalany przez napięcie polaryzujące BIAS2 (+2,5 V), podawane przez rezystor R11 na wejście nieodwracające pierwszego w łańcuchu wtórnika-separatora ze wzmacniaczem operacyjnym U3A. Podobnie, jak w przypadku przeciwzakłóceniowego filtra wejściowego, wyjściowy filtr wygładzający składa się z czterech wzmacniaczy operacyjnych, pracujących w konfiguracji wtórników-separatorów (U3A...U3D), pomiędzy którymi włączone zostały trzy ogniwa dolnoprzepustowych filtrów RLC drugiego rzędu (z elementami: R12-L7-C18, R13-L8-C19 oraz R14-L9-C20) – zatem finalnie otrzymano filtr szóstego rzędu.

Istotna różnica względem omawianego wcześniej, wejściowego filtru przeciwzakłóceniowego jest taka, że ostatni z wtórników-separatorów (ze wzmacniaczem operacyjnym U3D) został wykorzystany do wysterowania niskoimpedancyjnego wyjściowego wzmacniacza tranzystorowego z komplementarną parą tranzystorów bipolarnych Q1-Q2. Wzmacniacz ten pracuje w dość popularnej, prostej konfiguracji wtórnikowej w klasie 2×AB (z niewielkim prądem spoczynkowym Q1 i Q2). Wyjście wzmacniacza operacyjnego U3D wysterowuje stopień polaryzacji tranzystorów Q1 i Q2 z elementami: R15-D5-D6-R16. Diody D5 i D6 zapewniają termiczną stabilizację punktów pracy Q1 i Q2, którą dodatkowo poprawiają rezystory R17 i R18 (o względnie niewielkich wartościach), włączone w obwody emiterów Q1 i Q2 jako elementy ujemnego, prądowo-szeregowego sprzężenia zwrotnego. Stabilność punktu pracy omawianego stopnia wyjściowego, a także bardzo dobrą liniowość, zapewnia jednak przede wszystkim silne, ujemne (napięciowe) sprzężenie zwrotne: z wyjścia stopnia z tranzystorami Q1 i Q2 wprost na wejście odwracające wzmacniacza operacyjnego U3D, który wysterowuje tenże stopień. Kondensatory C22 i C23 zapewniają miejscowo odsprzężenie zasilania stopnia z Q1 i Q2 (istotne w przypadku większych obciążeń prądowych tego stopnia), a zespół pojemności C21A/C21B/C21C wyprowadza odfiltrowany pomiarowy sygnał wyjściowy (sterujący DUT) przez złącze BNC (J7). Fotografia tytułowa oraz fotografia 7 przybliżają szczegóły wykonania prototypowej wersji prezentowanej, półautomatycznej platformy pomiarowej.

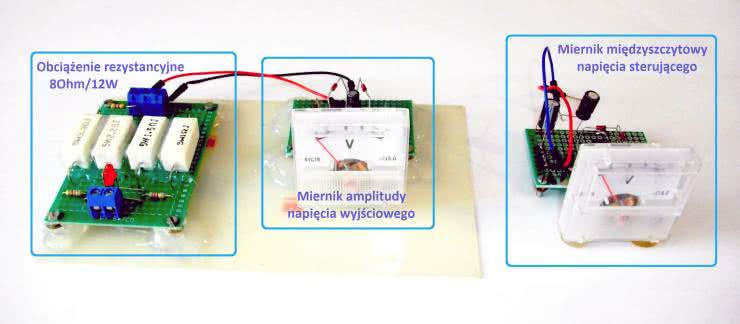

Na potrzeby zaplanowanych pomiarów opracowano trzy proste układy towarzyszące, pokazane na fotografii 8: sztuczne obciążenie rezystancyjne 8 Ω/12 W max., dedykowany do tego sztucznego obciążenia analogowy (zgrubny) miernik napięcia szczytowego na obciążeniu oraz analogowy (także zgrubny) miernik międzyszczytowej wartości napięcia sterującego (tzn. na wyjściu filtra wygładzającego sygnał z przetwornika DAC, zlokalizowanego w MCU na płytce NUCLEO).

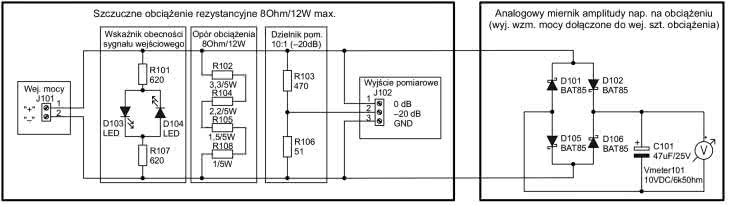

Na rysunku 77 zaprezentowano schematy elektryczne pierwszych dwóch z trzech wymienionych układów towarzyszących. Zasadniczą część sztucznego obciążenia rezystancyjnego stanowią cztery połączone szeregowo rezystory (R102, R104, R105 i R108) – każdy o maksymalnej dopuszczalnej mocy strat termicznych Pmax’=5 W. Z braku lepszych rozwiązań wykorzystano oporniki o różnych wartościach rezystancji (3,3 Ω, 2,2 Ω, 1,5 Ω oraz 1 Ω), jednak o łącznej wypadkowej wartości równej 8 Ω.

Z takiego rozwiązania wynika, że faktyczna maksymalna dopuszczalna moc strat dla całego kwartetu oporników, z uwagi na ich połączenie szeregowe, więc i taki sam prąd w każdym z elementów, jest limitowana przez ten opornik, w którym będzie wydzielała się największa moc strat termicznych. Jest nim rezystor R102 o wartości 3,3 Ω, dla którego maksymalna wartość skuteczna prądu wynosi:

I tak, dla całego zestawu oporników szeregowych w omawianym sztucznym obciążeniu, maksymalna dopuszczalna moc strat wyniesie:

Przyjęto, że całkowita, ciągła moc strat w opracowanym sztucznym obciążeniu nie powinna przekraczać wartości 12 W, choć w opisanej dalej praktyce pomiarów wzmacniaczy elektroakustycznych (długotrwałe, ciągłe testy) celowano w maksymalną wartość wydzielanej mocy czynnej na poziomie zaledwie 5 W. Minimoduł sztucznego obciążenia został wyposażony dodatkowo w: optyczną, prostą sygnalizację obecności wzmocnionego sygnału na wejściu J101 (złącze śrubowe typu ARK-2) z rezystorami R101 i R107 oraz diodami LED D103, D104, a także w dzielnik pomiarowy 10:1 z rezystorami R103 i R106, dzięki któremu na wyjściu pomiarowym J102 (złącze śrubowe typu ARK-3) był dostępny zarówno bezpośredni sygnał mocy, jak i jego replika, stłumiona o 20 dB (do dalszego pomiaru i analizy we wnętrzu omawianego minisystemu pomiarowego).

Przeznaczony do sztucznego obciążenia, analogowy miernik przybliżonej wartości napięcia szczytowego (schemat także na rysunku 77) został oparty o kwartet diod Schottky’ego (D101, D102, D105 i D106) w popularnym układzie prostownika dwupołówkowego z mostkiem Graetza i kondensatorem wygładzającym C101 oraz prostym ustrojem wychyłowego woltomierza o zakresie pomiaru 0...10 VDC i rezystancji wewnętrznej 6,5 kΩ. Stała czasowa rozładowania tego prostego miernika, wynikająca przede wszystkim z połączenia równoległego pojemności C101 i rezystancji wewnętrznej zastosowanego ustroju pomiarowego, wynosiła około τ≈47 μF·6,5 kΩ=305,5 ms.

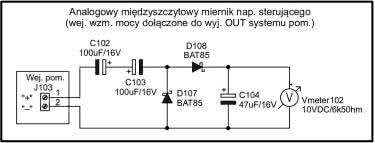

Do monitorowania obecności i przybliżonego poziomu sygnału sterującego na wyjściu filtra, wygładzającego sygnał z przetwornika DAC, wykorzystano miernik międzyszczytowej wartości tego napięcia (rysunek 78). Mierzony sygnał sterujący, doprowadzany na wejście J103 (złącze śrubowe typu ARK-2), poprzez połączoną szeregowo (i z przeciwnymi polaryzacjami) parę kondensatorów elektrolitycznych C102 i C103, trafiał na prosty układ podwajacza amplitudy napięcia wejściowego z diodami D107, D108 oraz kondensatorem wygładzającym C104. Podobnie jak w przypadku omówionego wcześniej ustroju pomiarowego, stała czasowa rozładowania miernika wynosiła około τ≈47 μF·6,5 kΩ=305,5 ms.

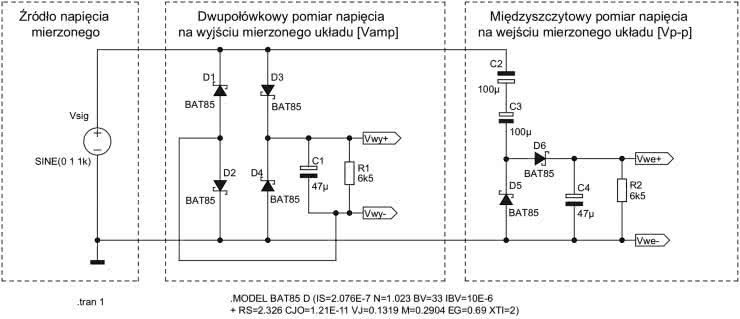

Na rysunku 79 zaprezentowano schemat obu omówionych prostych ustrojów pomiarowych, który posłużył do oszacowania ich charakterystyk przejściowych na drodze symulacji w środowisku LTspice. Dla uproszczenia prac oba układy były zasilane z tego samego źródła sygnału sinusoidalnego, którego amplituda była zmieniana ręcznie w trakcie kolejnych symulacji w dziedzinie czasu.

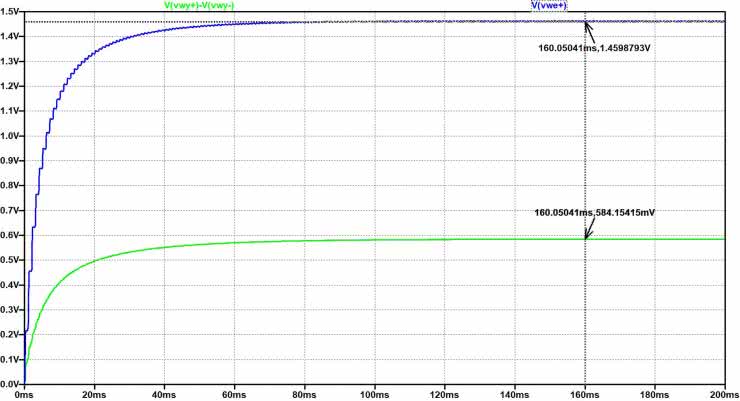

Na rysunku 80 przedstawiono przykładowe przebiegi czasowe podczas dochodzenia do stanu quasi-ustalonego dla sygnałów mierzonych na wyjściach obu układów pomiarowych – przy pobudzeniu ich na wejściach sygnałem sinusoidalnym o częstotliwości 1 kHz i amplitudzie 1,0 V.

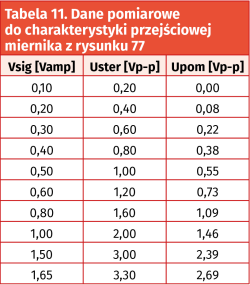

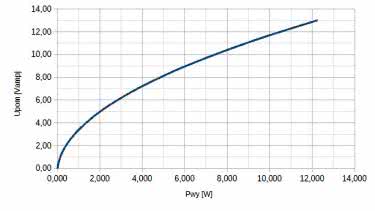

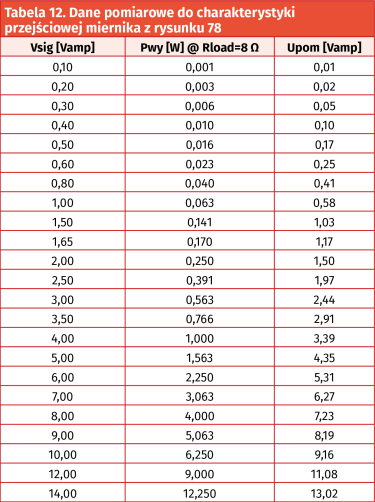

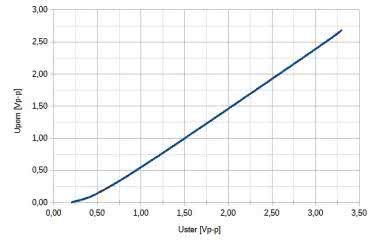

Jak wynika, z racji obecności w tych układach diod prostowniczych oraz obciążenia rezystancjami samych ustrojów pomiarowych, symulowane napięcia zmierzone są dość dalekie od spodziewanych odpowiednio: 1,0 V i 2,0 V. Właśnie dlatego autor postanowił wykonać dla układów z rysunku 79 szereg symulacji – dla sinusoidalnych napięć sterujących Vsig o amplitudzie zmienianej w zakresie od 0,1 V do 14 V. Rezultaty tych symulacji zostały ujęte w tabelach 11 i 12, a także na wykresach na rysunkach 81 i 82.

W szczególności, wymienione wykresy zostały opracowane w taki sposób, by za ich pomocą dało się w miarę wygodnie, dokładnie i szybko oszacować poziomy: sygnału sterującego na wejściu mierzonego urządzenia DUT oraz mocy na jego wyjściu. Opisana w drugiej części tego artykułu, obszerna praktyka pomiarowa, wykazała znaczną użyteczność opisanych tutaj prostych, zgrubnych ustrojów pomiarowych – głównie w zakresie zapobiegania przesterowaniom.

Do omówienia pozostały jeszcze szczegóły oprogramowania wykorzystanego w trakcie pomiarów – zarówno tego zaimplementowanego w wykorzystywanym mikrokontrolerze jak również w terminalu PC. Aspekty te zostaną poruszone bardziej szczegółowo w kolejnej części tego artykułu, poświęconej samym pomiarom oraz wszelkim warunkom operacyjnym ich realizacji.

Adam Sobczyk, EP

Zaloguj

Zaloguj