Do przeprowadzenia testów, oprócz zapoznania się z poprzednimi odcinkami kursu, konieczne będzie przygotowanie części sprzętowej, tj. płytki bazowej DSP1701A_DSP_MK2, modułów rozszerzeń, źródła sygnału cyfrowego i zewnętrznego przetwornika D/A. Dwa ostatnie z wymienionych urządzeń muszą być wyposażone w interfejs cyfrowy w standardzie przewodowym SPDIF lub optycznym Toslink. Niezbędne okażą się też wzmacniacz z głośnikami, okablowanie oraz oscyloskop.

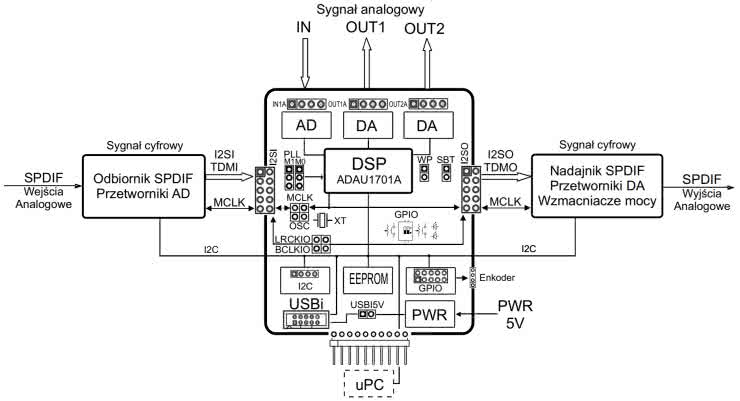

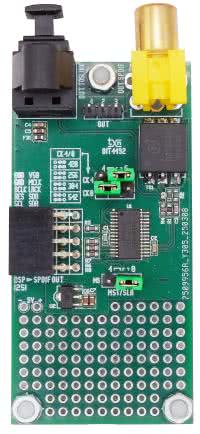

Na wstępie warto przypomnieć pełną konfigurację sprzętową zestawu DSP1701A_DSP_MK2, pokazaną na rysunku 1. Będziemy z niej korzystać w przykładowych aplikacjach.

Procesor DSP ADAU1701, zastosowany w zestawie DSP1701A_DSP_MK2, oprócz wbudowanych przetworników AD/DA ma także szeregowe, cyfrowe interfejsy audio: jeden ośmiokanałowy interfejs odbiorczy (4 kanały stereo) i jeden ośmiokanałowy interfejs nadawczy (także 4 kanały stereo). Oba mogą pracować w trybie multipleksowanym czasowo, czyli TDM (maksymalnie ośmiokanałowym). Sygnały interfejsów szeregowych współdzielone są z wyprowadzeniami GPIO. W zestawie DSP1701A_DSP_MK2 sygnały „zerowego” interfejsu wejściowego, wraz z zasilaniem 5 V, wyprowadzono na złącze I2SI, a wyjściowego – na złącze I2SO, zgodnie z tabelą 1.

UWAGA: GPIO pracują w standardzie napięciowym 3,3 V, przekroczenie tego napięcia trwale uszkodzi procesor DSP.

Interfejsy szeregowe służą do podłączenia zewnętrznych układów korzystających ze standardowej, 3-przewodowej magistrali audio zawierającej: linię danych SDx, linię zegara bitów BLCK i linię synchronizacji kanałów LRCK. Gdy liczba wejść/wyjść wbudowanych przetworników A/D lub D/A jest niewystarczająca, rozszerzenie o dodatkowe kanały konwerterów wymaga rozbudowy zestawu o zewnętrzne moduły przetworników, bazujących na interfejsie cyfrowym. Podobnie w przypadku konieczności obróbki sygnału w standardzie SPDIF/Toslink, konieczne jest dodanie modułu z odbiornikiem lub nadajnikiem konwertującym sygnał do formatu I²S/TDM, obsługiwanego przez ADAU1701 – który pozbawiony jest możliwości bezpośredniej obróbki ww. sygnałów. W przypadku projektowania własnych modułów należy zastosować interfejs TDM/I²S oraz zasilanie 5 V, zwracając uwagę na zapewnienie standardu napięciowego 3,3 V dla wyprowadzeń GPIO. Korzystając z interfejsów cyfrowych, można we własnym zakresie rozszerzyć możliwości DSP1701A_DSP_MK2 o obsługę odbiorników Bluetooth lub konwerterów USB/I²S, np. XMOS czy Amanero. Opis części sprzętowej użytych w kursie modułów rozszerzeń zaprezentowany został w EP 06/2025.

Szeregowy port wejściowy audio ADAU1701 zawsze pracuje w trybie slave, tj. sygnały zegara bitowego INPUT_BCLK i znacznika kanałów INPUT_LRCK muszą być generowane przez współpracujące z DSP urządzenie (przetwornik A/D, odbiornik SPDIF itp.). Wyprowadzenia INPUT_BCLK oraz INPUT_LRCK są wejściami i nie ma możliwości zmiany ich funkcji lub trybu pracy. Sygnał danych audio musi być doprowadzony do jednego z wyprowadzeń SDATA_IN0...3. Podczas opracowywania własnych modułów rozszerzeń tryb slave portu wejściowego jest pewnym utrudnieniem, gdyż za generację sygnałów BCLKI i LRCKI musi odpowiadać moduł rozszerzeń – co wymaga stosowania dodatkowego generatora przebiegów synchronicznych z sygnałem MCLK głównego oscylatora. Pewnym sposobem obejścia tego problemu, związanym z zablokowaniem dwóch pinów GPIO, jest generowanie BCLKI i LRCKI z użyciem szeregowego interfejsu wyjściowego i wyprowadzeń BCLKO oraz LRCKO. Zestaw DSP1701A_DSP_MK2 umożliwia ich bezpośrednie połączenie zworami oznaczonymi BCLK, LRCK.

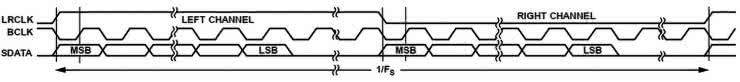

Do elastycznej konfiguracji pozostawiono natomiast format, w jakim przesyłane są dane wejściowe, co poszerza zakres współpracujących układów. Podczas konfiguracji procesora mamy możliwość wyboru formatu:

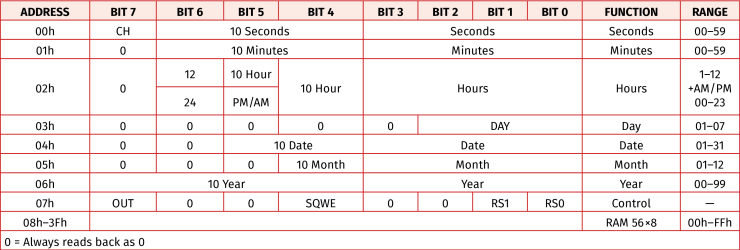

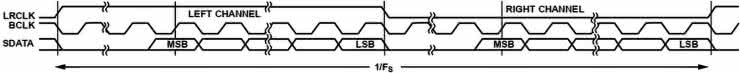

- I²S (Inter-IC Sound), standardowy interfejs audio zgodny ze specyfikacją magistrali opracowanej przez Philipsa. Przykładowe przebiegi pokazano na rysunku 2. Sygnały danych SDATA opóźnione są o jeden cykl zegara BCLK. Format I²S używany jest przez większość przetworników A/D i D/A (AD1955, TAA5xx, PCM51xx), interfejsów SPDIF (CS8416, DIT4096) i USB (Amanero, XMOS) oraz konwerterów częstotliwości próbkowania (SRC4192, AD1896).

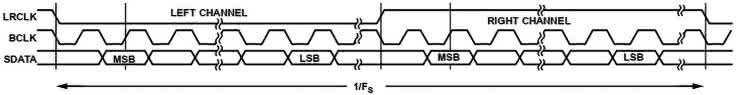

- LJ (Left Justified) – sygnały danych wyrównane są do lewej strony ramki audio, bez opóźnienia charakterystycznego dla I²S. Przykładowe przebiegi widać na rysunku 3.

- RJ (Right Justified), sygnały danych wyrównane są do prawej strony ramki audio, co uwidoczniono na rysunku 4. Formaty I²S, LJ, akceptują ramki o szerokości słów równej 16/18/20/24 bitów, zaś powyżej 24 bitów sygnał zostanie ograniczony do 24 bitów. Format RJ wymaga pełnej ramki 64-bitowej i określenia rozdzielczości przy konfiguracji DSP. Ja preferuję w projektach tryb I²S, jako standardowy dla połączeń cyfrowych audio. Dodatkowo przy konfiguracji DSP można określić aktywny stan sygnału LRCK (szybka zamiana kanałów L/R) i aktywne zbocze sygnału BCLK.

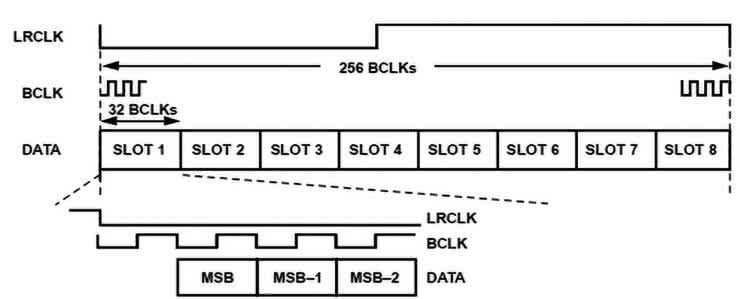

- TDM (TDM8), format z multipleksowaniem czasowym stosowany często, gdy konieczne jest ograniczenie ilości zajmowanych przez interfejs cyfrowy wyprowadzeń GPIO. W trybie tym maksymalnie osiem kanałów przesyłanych jest jedną linią danych (sygnały zegarowe BCLK, LRCK pozostają bez zmian), każdy w osobnym slocie czasowym o długości 32×BCLK. Położenie slotu w ramce jest ściśle określone, zgodnie z rysunkiem 5. Dane TDM mogą być synchronizowane poziomem sygnału LRCK lub impulsem. Pinem GPIO obsługującym TDM w ADAU1701 jest linia SDATA_IN0 (MP0), wyprowadzona – wraz z LRCK/BCLK – na złącze I2SI.

Format TDM używany jest przy współpracy z wielokanałowymi przetwornikami A/D i D/A (ADAU1966, ADAU1979, PCM4104), stosowanymi w systemach 5.1, 7.1, studyjnych oraz Car Audio. TDM zastosowano także do łączenia odpowiednio skonfigurowanych, dwukanałowych przetworników A/D i D/A, np. TAA5xxx, TAC5xxx w kaskady, ułatwiające projektowanie układów wielokanałowych przy użyciu typowych, tanich przetworników stereofonicznych.

Format TDM – oprócz zmniejszenia liczby wymaganych GPIO – upraszcza zaprojektowanie płytki z mniejszą liczbą połączeń sygnałowych, co ułatwia spełnienie wymogów EMC/EMI. Zawsze to 3 zamiast n×3 linii promieniujących zakłócenia – co prawda sygnały są o wyższych częstotliwościach, ale pozostają jeszcze względnie łatwe do opanowania. W aplikacjach, w których istotny jest koszt, TDM zwalnia dodatkowo piny GPIO DSP, co może być istotną zachętą do jego stosowania. Sygnał TDM musi być doprowadzony do MP0 (SDATAIN0) i nie ma możliwości jego przemapowania.

Niestety ADAU1701 nie obsługuje bezpośrednio interfejsu cyfrowego w formacie PDM, popularnego w mikrofonach MEMS. W tym przypadku pozostaje użycie mikrofonu z interfejsem I²S lub PDM, połączonym z konwerterem PDM/I²S (ADAU7002, ADAU7118, PCMD3140, FAN3852).

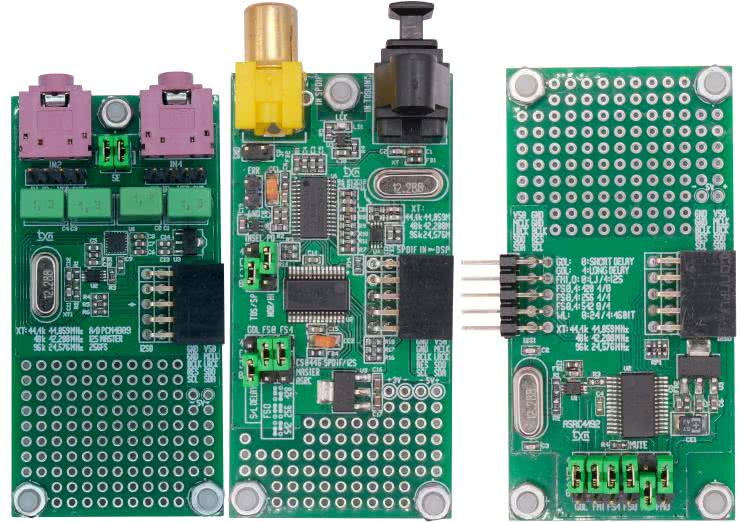

Pierwszy projekt testowy z użyciem wejściowego interfejsu szeregowego, skonfigurowanego w formacie I²S, umożliwia przetestowanie następujących modułów (fotografia 1):

- DSP1701A_AD_PCM1809 – dwa liniowe wejścia analogowe (z lewej),

- DSP1701A_SPDIF_IN_ASRC – moduł odbiornika SPDIF (środek), Toslink z konwerterem częstotliwości próbkowania ASRC

- DSP1701A_ASRC4192 – moduł ASRC (z prawej).

Wszystkie trzy moduły z fotografii 1 pracują w trybie master, tj. generują sygnały BCLK, LRCK oraz MCLK. Przed podłączeniem do płytki bazowej należy zdjąć z niej zwory OSC, BCLK, LRCK oraz zewrzeć zworę MCLK. Generator zegarowy zostanie odłączony, a sygnał zegarowy MCLK dla DSP – przełączony na sygnał MCLK z modułu rozszerzeń. Wyprowadzenia LRCK, MCLK zostaną odłączone od wyjściowego portu szeregowego.

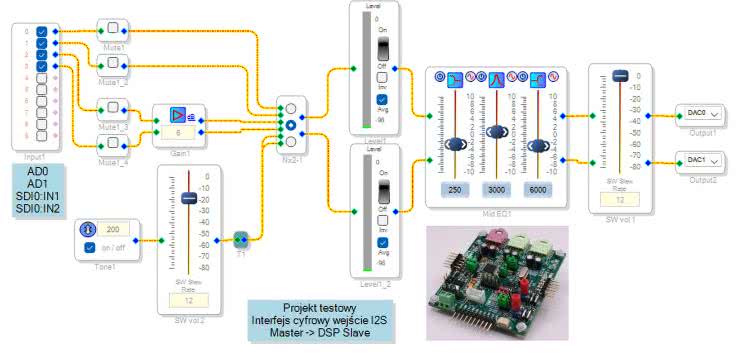

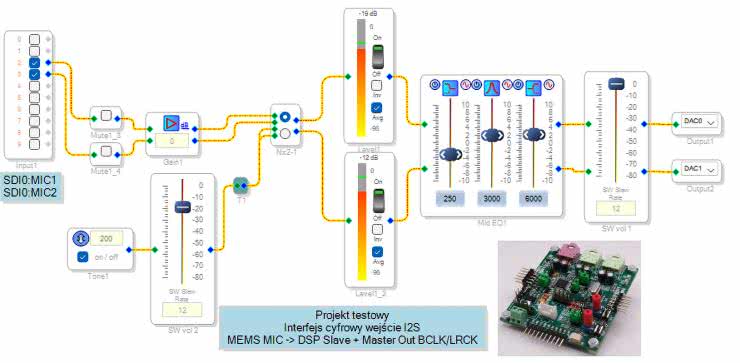

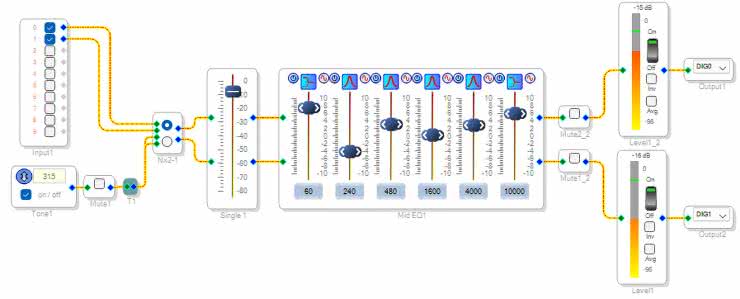

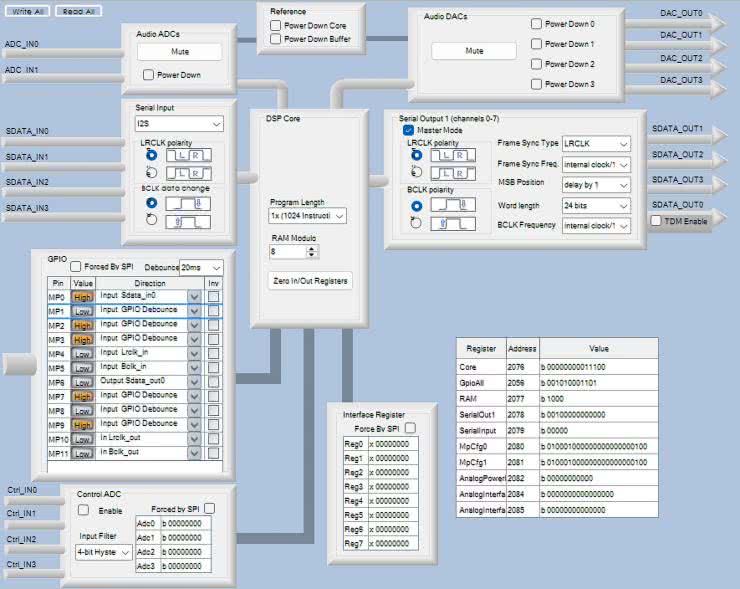

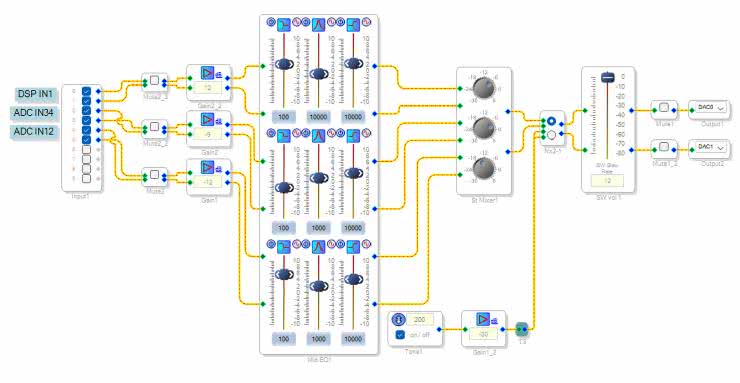

Do obsługi wszystkich trzech modułów opracowano jedną aplikację ADAU1701_MK2_Cz5_ProjektTestowyI2SMasterIn.dspproj, której schemat pokazano na rysunku 6.

Aby użyć wejść cyfrowych należy użyć bloku Input z biblioteki IO\Input. Wejścia cyfrowe nie mają oddzielnego bloku funkcjonalnego i w celu wprowadzenia sygnału używany jest blok wejść Input. Dwa pierwsze wejścia – oznaczone 0,1 – służą do wprowadzania sygnału z wbudowanego przetwornika A/D, co zostało już zastosowane w dotychczasowych projektach. Wejścia oznaczone numerami 2...8 służą do wprowadzania sygnału cyfrowego z interfejsu szeregowego, w kolejności SDI0...3 (tj. interfejs SDI0 to wejścia 2, 3, SDI1 to wejścia 4, 5 itd). Moduły rozszerzeń połączono z interfejsem SDI0, więc ich sygnały dostępne są na wyprowadzeniach 2, 3.

W pierwszej kolejności przetestowany zostanie moduł z dwukanałowym przetwornikiem A/D typu PCM1809. Wejściowy, różnicowy sygnał audio należy doprowadzić do gniazd monofonicznych IN1, 2 typu jack 3,5 mm (3 pin.). Jeżeli nie dysponujemy źródłem sygnału różnicowego, należy na module założyć zwory SE1,2, konfigurując w ten sposób obwody wejściowe PCM1809 do trybu niesymetrycznego, a monofoniczne sygnały doprowadzić do złączy jack IN1, 2. Do podłączenia można także użyć listew szpilkowych IN1A, 2A.

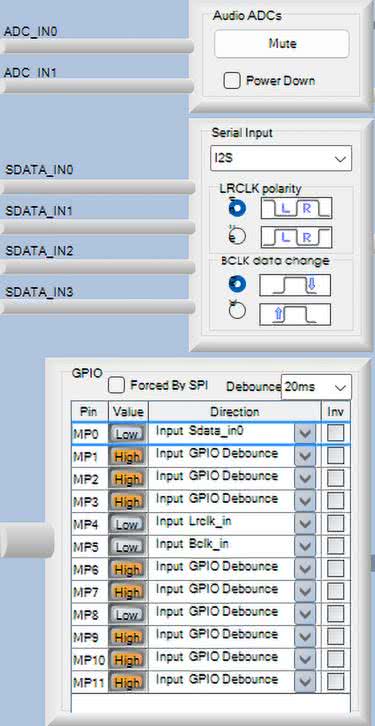

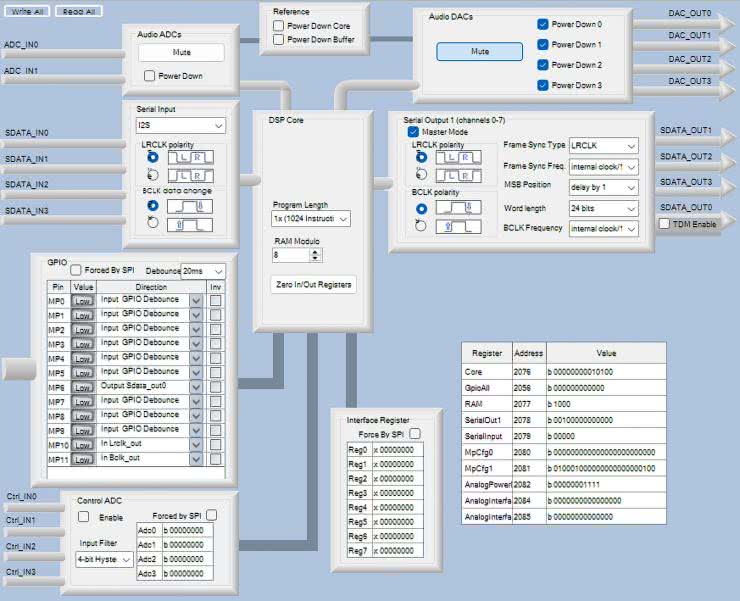

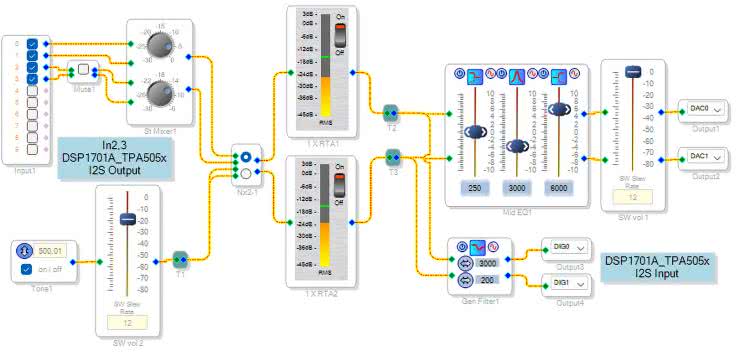

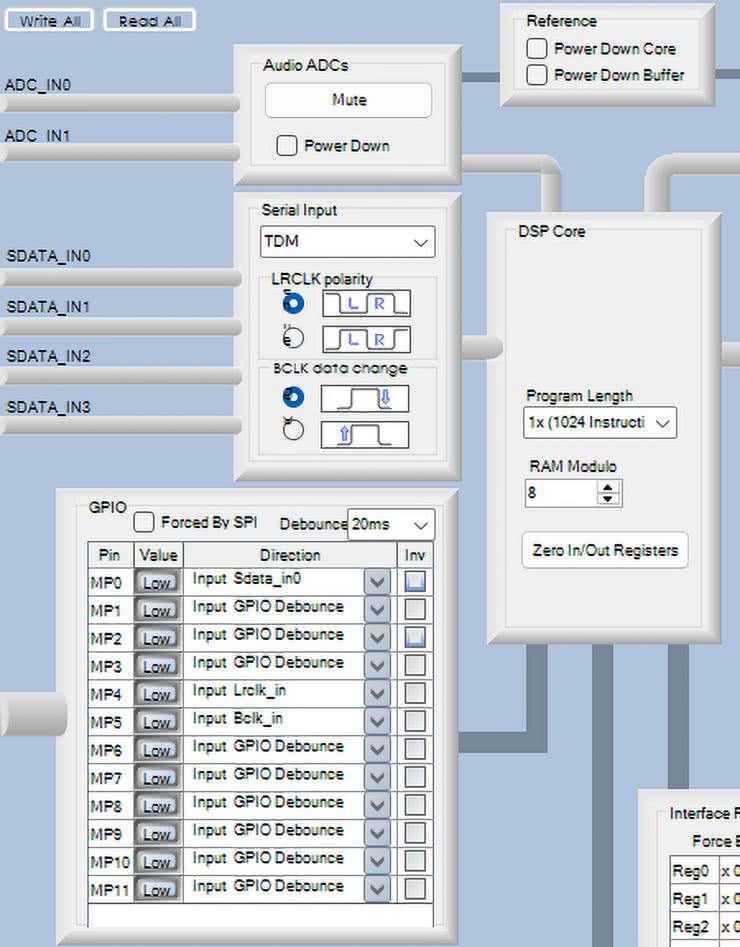

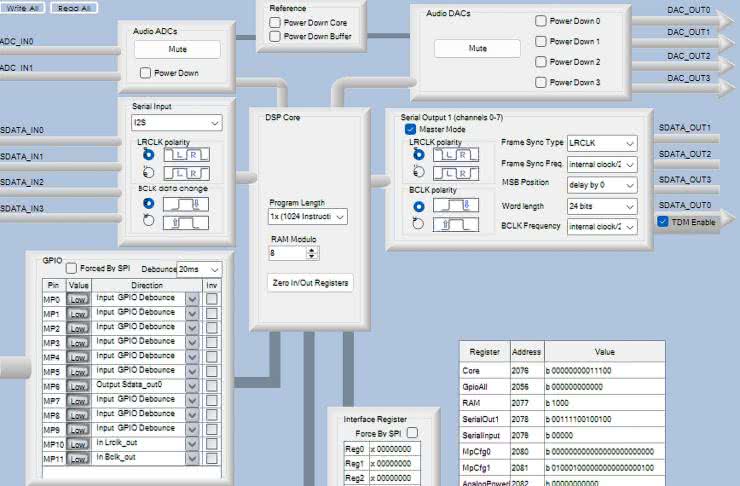

Przed wgraniem aplikacji należy skonfigurować wyprowadzenia GPIO do obsługi interfejsu szeregowego. MP0 ustawiamy jako wejście interfejsu SDI0, MP4 jako wejście sygnału wyboru kanału LRCK, a MP5 jako wejście zegara bitowego BCLK. Trzeba też skonfigurować format interfejsu szeregowego I²S z polaryzacją sygnałów zgodną z rysunkiem 7.

Po uruchomieniu aplikacji możemy multiplekserem wybrać źródło sygnału wejściowego: analogowe z wbudowanego A/D, cyfrowe z modułu PCM1809 oraz sygnał generatora testowego. Po wyborze źródła możliwa jest trzypasmowa regulacja barwy dźwięku oraz regulacja głośności. Sygnał wyjściowy dostępny jest na gnieździe OUT1 i odpowiadających mu złączach szpilkowych OUT1A.

Procesor ADAU1701 nie ma wbudowanego odbiornika standardu SPDIF, a zatem by umożliwić bezpośrednią obróbkę sygnału cyfrowego, np. z odtwarzaczy CD, DVD itp. (w standardzie przewodowym SPDIF lub optycznym TOSLINK), konieczne było opracowanie modułu odbiornika. Moduł DSP1701A_SPDIF_IN_ASRC – oprócz odbiornika SPDIF/I²S opartego na układzie CS8416 – ma także konwerter częstotliwości próbkowania ASRC typu SRC4192. Ze względu na wymóg synchroniczności częstotliwości procesora DSP z sygnałem wejściowym, bez bloku ASRC niemożliwa byłaby obróbka sygnału cyfrowego o fs innej, niż wybrana podczas tworzenia aplikacji. Połączenie wymienionych układów zapewnia współpracę z częstotliwościami fs w zakresie 32...192 kHz, pokrywając większość typowych zastosowań. Przed podłączeniem modułu należy wybrać kwarc o częstotliwości 256×fs, czyli (kwarc 12,288 MHz przy 48 kHz) oraz skonfigurować moduł. Zworami FSO ustawiamy krotność 256, zworę S/L DELAY ustawiamy w położenie S (zdjęta), zworę PD w położenie Hi (zwarta), a zworę INSEL w położenie zgodne z typem źródła sygnału (TOSLINK/SPDIF). Po wgraniu aplikacji i podłączeniu źródła sygnału, na module DSP1701A_SPDIF_IN_ASRC powinna zaświecić się dioda LCK sygnalizująca poprawny odbiór sygnału SPDIF. Podobnie jak poprzednio, multiplekserem możemy wybrać źródło sygnału oraz skorygować barwę i poziom sygnału.

Moduł DSP1701A_SPDIF_IN_ASRC umożliwia podłączenie do DSP1701A_DSP_MK2 sygnału I²S o fs=32...192 kHz z zewnętrznych odbiorników Bluetooth, komputerów SBC (np. Raspberry Pi) lub odbiorników USB/I²S (np. Amanero lub XMOS). Moduł z DSP współpracuje w trybie master I²S lub LJ (16/24-bitowym) i generuje sygnał zegarowy MCLK. Ze względu na taktowanie DSP z modułu ASRC, należy zdjęć zworę OSC, wyłączając wbudowany generator. Port wejściowy ASRC pracuje w trybie I²S lub LJ slave i nie wymaga sygnału zegarowego MCLK. Należy natomiast zapewnić zgodność sygnałów wejściowych LRCKI, BCLKI oraz SDI modułu ASRC ze standardem 3,3 V. Po dobraniu kwarcu, zworami FS0,1 należy ustawić wymaganą krotność fs, zworą FMO – format wyjściowy I²S/LJ, zworą WL – format danych (16/24 bitów), a zworą FMI – tryb odbieranych danych I²S/LJ. Sprawdzenie modułu po doprowadzeniu sygnałów I²S do złącza I²S przebiega identycznie, jak w przypadku DSP1701A_SPDIF_IN_ASRC.

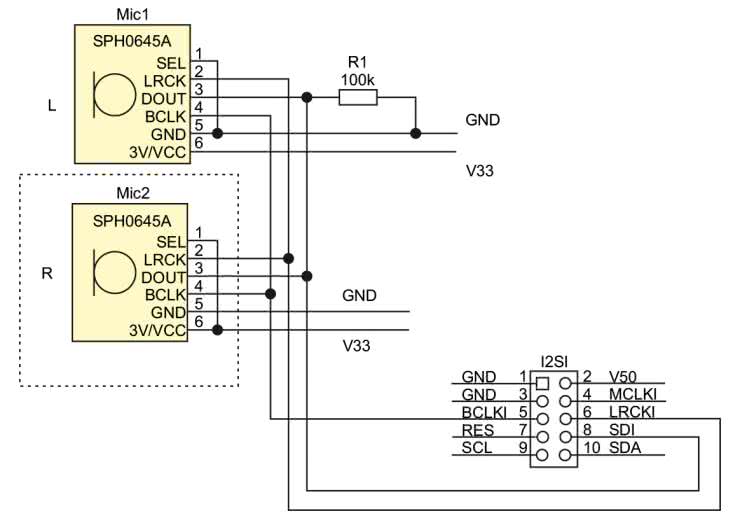

Ostatnim projektem dotyczącym wejść cyfrowych w formacie I²S, jest ADAU1701_MK2_Cz5_ProjektTestowyI²SMicMemsSlaveIn.dspproj. W projekcie źródłem sygnału są dwa mikrofony cyfrowe SPH0645, które pracują tylko w trybie slave. Aby uniknąć konieczności budowania generatora i dzielników niezbędnych do wytwarzania sygnałów BCLKI, LRCKI (potrzebnych do obsługi szeregowego interfejsu wejściowego DSP), można uciec się do pewnej sztuczki. Jeżeli zrezygnujemy z użycia MP10,11 w funkcji GPIO, to szeregowy interfejs wyjściowy może być zastosowany do generacji sygnałów BCLK, LRCK. Mostkując odpowiadające sygnały interfejsu wyjściowego (*I) i wejściowego (*O) zapewniamy taktowanie DSP i współpracującego układu slave, bez użycia zewnętrznych elementów. Po założeniu zwór BCLK, LRCK w płytce bazowej, sygnały BCLKO, LRCKO są dostępne na złączu I2SI, do którego podłączymy mikrofony – zgodnie ze schematem z rysunku 8. Przed podłączeniem do płytki bazowej mikrofonów należy założyć zworę OSC, aby aktywować wbudowany generator. Zasilanie mikrofonów 3,3 V może zostać pobrane ze złącza UPC. Należy pamiętać o zachowaniu możliwie krótkich przewodów I²S.

Schemat aplikacji ADAU1701_MK2_Cz5_ProjektTestowyI²SMicMemsSlaveIn.dspproj zaprezentowano na rysunku 9.

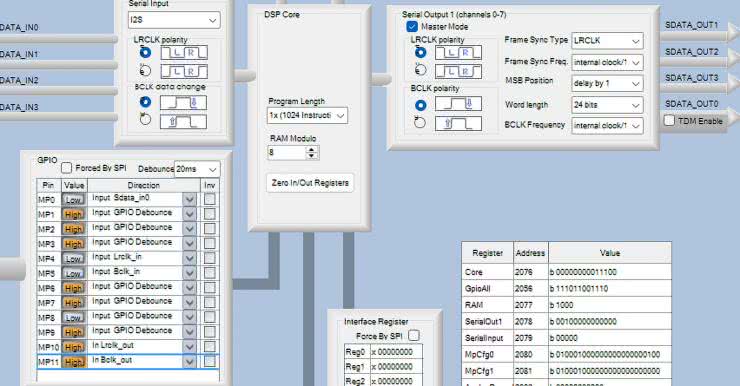

Konfigurację procesora pokazano na rysunku 10. Oprócz konfiguracji wyprowadzeń interfejsu wejściowego MP0, 4, 5, konieczne jest ustawienie MP10 i MP11 do generacji sygnałów LRCK_OUT, BCLK_OUT oraz włączenie interfejsu wyjściowego w formacie master I²S.

Po wgraniu aplikacji, na wyjściach DAC0,1 powinien być słyszalny sygnał z mikrofonów (uwaga na poziom sygnału – istnieje niebezpieczeństwo sprzężenia akustycznego).

Podobny sposób, rezygnując z GPIO na wyprowadzeniach MP10, 11, można zastosować przy tworzeniu własnych modułów rozszerzeń pracujących w trybie slave. Projekt można będzie zastosować też do sprawdzenia działania opracowanych minimodułów ADC_PCM1809 i ADC_TAA5242, które publikujemy w bieżącym numerze EP.

Szeregowy port wyjściowy ADAU1701 może pracować zarówno w trybie slave, jak i master – sygnały OUTPUT_BCLK, OUTPUT_LRCK mogą być zatem generowane także przez DSP. Jedynym odstępstwem jest format TDM z fs=192 kHz, w przypadku którego DSP obsługuje tylko tryb slave. Wyprowadzenia OUTPUT_BCLK, OUTPUT_LRCK są konfigurowane jako wejścia w trybie slave lub wyjścia w trybie master. Sygnał wyjściowy dostępny jest na wyprowadzeniach SDATA_OUT0...3, a w formacie TDM – tylko na SDATA_OUT0 (MP6), bez możliwości mapowania na inny port szeregowy. Podobnie jak w porcie wejściowym, elastycznej konfiguracji pozostawiono formaty, w których przesyłane są dane wyjściowe. W konfiguracji procesora mamy możliwość wyboru: I²S, LJ, RJ, TDM z synchronizacją poziomem lub impulsem.

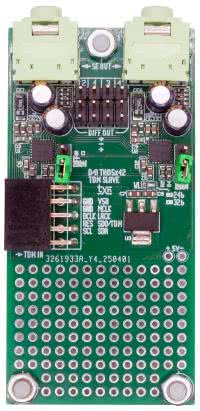

Projekt testowy ADAU1701_MK2_Cz5_ProjektTestowyI2SOutMaster, opracowany w celu zaprezentowania działania wyjściowego interfejsu szeregowego (skonfigurowanego w formacie I²S), umożliwia przetestowanie modułu DSP1701A_SPDIF_OUT_DIT4192, zawierającego interfejs wyjściowy SPDIF w standardzie Coaxial i Toslink. Część sprzętowa modułu została opisana w EP06/2025, a wygląd modułu pokazano na fotografii 2. Projektu można użyć też z opisanymi wcześniej modułami wzmacniaczy mocy SSM2518 (EP07/2025) i SSM3582 (EP01/2021) oraz z opracowanymi minimodułami DAC_PCM5102, DAC_TAD5142, które także opisujemy szerzej w tym numerze EP.

Schemat aplikacji ADAU1701_MK2_Cz5_ProjektTestowyI2SOutMaster.dspproj pokazano na rysunku 11.

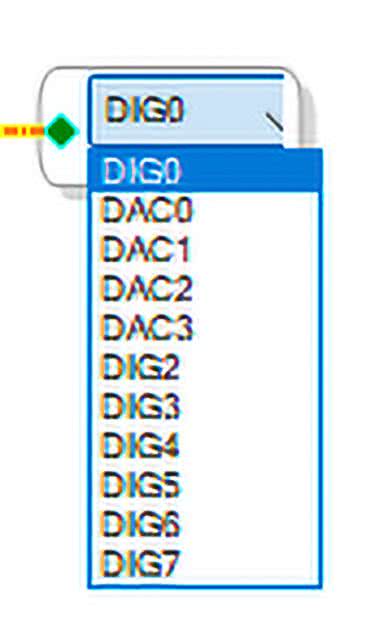

Wyjścia cyfrowe nie mają oddzielnego bloku funkcjonalnego i w celu wyprowadzenia sygnału używany jest tylko blok wyjść Output z biblioteki IO\Output, tak jak w przypadku wbudowanych przetworników DAC. Podczas konfiguracji z listy rozwijalnej należy wybrać odpowiednie wyjście cyfrowe DIG(x), co widać na rysunku 12.

Podobnie jak w przypadku wejść analogowych, kolejne wyjścia przypisane są do interfejsów wyjściowych. Dwa pierwsze wyjścia – oznaczone DIG0, DIG1 – służą do wprowadzania sygnału poprzez interfejs SDO0, a następnie (DIG2...8) przez SDO1...3. Moduły rozszerzeń połączone są z interfejsem SDO0, więc ich sygnały dostępne są na wyprowadzeniach DIG0, 1. W formacie TDM kolejne użyte kanały zajmują wyjścia DIG0...8, a fizycznie wyprowadzone są przez interfejs SDO0 (TDMO).

Przed wgraniem aplikacji testowej należy skonfigurować wyprowadzenia GPIO do obsługi interfejsu szeregowego. MP6 ustawiamy jako wyjście danych interfejsu SDO0, MP10 – jako wyjście sygnału wyboru kanału LRCK, a MP11 – jako wyjście zegara bitowego BCLK. Konfigurujemy też format interfejsu szeregowego I²S master do trybu z polaryzacją sygnałów wg rysunku 13. Nieużywane w projekcie przetworniki DAC należy wyciszyć i wprowadzić w tryb obniżonego poboru mocy.

Na płytce bazowej należy założyć zworę OSC oraz zdjąć zwory LRCK, BCLK, MCLK. Do wejścia IN1 trzeba podłączyć źródło sygnału analogowego, a do wyjść OUT_TOSLINK lub OUT_SPDIF – zewnętrzny przetwornik D/A. W zależności od standardu wejść przetwornika D/A, należy użyć światłowodu lub przewodu koncentrycznego. W module DSP1701A_SPDIF_OUT_DIT4192, podłączonym po prawej stronie płytki bazowej do gniazda I²SO, należy ustawić zworami CK1, 0 krotność fs=256 oraz ustawić tryb slave zworą MST/SLA. Po wgraniu aplikacji, sygnał z wejścia analogowego IN1 – po obróbce – zostanie wyprowadzony przez port szeregowy SDO0 do konwertera/nadajnika I²S/SPDIF, opartego na układzie DIT4192. W identyczny sposób można sprawdzić moduły przetworników D/A i wzmacniacz mocy z interfejsem I²S. W przypadku własnych konstrukcji należy pamiętać o standardzie 3,3 V, niezbędnym do bezpiecznej pracy wyprowadzeń interfejsu I²SO.

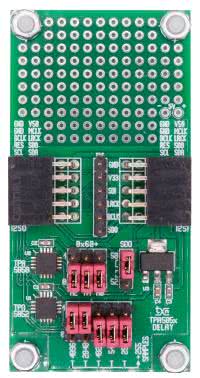

Projektem jednocześnie korzystającym z obu interfejsów cyfrowych DSP jest ADAU1701_MK2_Cz5_ProjektTestowyI2SDelay.dspproj. Aplikacja bazuje na module cyfrowej linii opóźniającej DSP1701A_TPA505x (fotografia 3), opisanej w EP06/2025.

Ograniczone zasoby procesora ADU1701 utrudniają realizację dłuższych opóźnień sygnału, szczególne przydatnych, gdy tworzymy efekty do instrumentów lub zwrotnice głośnikowe, w których opóźnieniem wyrównujemy fazę sygnału. Opisany moduł zawiera dwie linie opóźniające: TPA5052 (użyty w projekcie testowym), w której opóźnienie 0...170 ms (przy fs=48 kHz) regulowane jest zworami, a także TPA5050, w której parametr ten jest ustawiany programowo poprzez magistralę I²C. Układy cyfrowej linii opóźniającej są urządzeniami slave magistrali I²S. Schemat aplikacji testowej pokazano na rysunku 14.

Sygnał analogowy z wbudowanego przetwornika A/D doprowadzony jest do miksera, a następnie do multipleksera sygnału z generatora testowego. Następnie, przez blok regulatora barwy, doprowadzony jest do wyjść przetwornika D/A. Jednocześnie sygnał zostaje podany na filtr umożliwiający kształtowanie charakterystyki sygnału przed doprowadzeniem do linii opóźniającej, podłączonej do wyjść DIG0, 1. Opóźniony sygnał, dostępny na interfejsie SDI0 (na wejściach 2, 3), doprowadzony jest do drugiego kanału miksera, gdzie można ustalić proporcje sygnału wejściowego i opóźnionego. Dzięki wielokrotnemu opóźnieniu sygnału w pętli sprzężenia, aplikacja może realizować efekt echa/pogłosu, zależny od ustawionego opóźnienia. Jeżeli zależy nam na dłuższym opóźnieniu, układy można łączyć kaskadowo lub – w przypadku sygnału jednokanałowego – użyć oddzielnie każdy z dwóch kanałów TPA505x, odpowiednio łącząc wejścia i wyjścia interfejsów cyfrowych. Konfigurację DSP odpowiednią dla opisywanego projektu można zobaczyć na rysunku 15. Blok wyjściowy SDO0 skonfigurowany jest w tryb master w formacie I²S, interfejs wejściowy SDI0 – w tryb slave. Interfejs SDI taktowany jest sygnałami interfejsu wyjściowego LRCKO, BCLKO.

W celu przetestowania aplikacji, do wejścia IN1 należy doprowadzić sygnał ze źródła analogowego, a do wyjścia OUT1 podłączyć wzmacniacz. Moduł DSP1701A_TPA505x należy podłączyć z prawej strony płytki bazowej, do złącza I2SO. Dodatkowo należy połączyć sygnał SDO – ze złącza I²S modułu opóźnienia do wejścia SDI złącza I2SI modułu bazowego, korzystając z krótkiego odcinka przewodu z wtykami żeńskimi. Na płytce bazowej należy założyć zwory OSC, LRCK, BCLK, a na module opóźnienia wybrać zworą SDO układ TPA5050 oraz ustawić zworami opóźnienie (wielokrotność próbek fs, o które zostanie opóźniony sygnał). W aplikacji można ustawić regulatorami miksera poziom sygnału pogłosu, korektorami – wymaganą charakterystykę (np. tłumienie wysokich częstotliwości w torze opóźnienia), zworami w module – zmienić czas opóźnienia, a blokiem Mute1 – odłączyć opóźniony sygnał od toru sygnałowego.

Interfejs wejściowy TDM

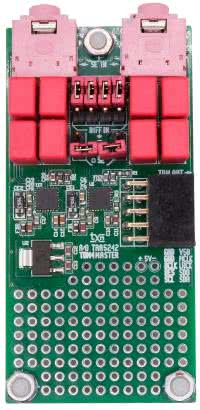

Projekt testowy do obsługi wejściowego interfejsu szeregowego, skonfigurowanego w formacie TDM, przeznaczony jest do sprawdzenia modułu rozszerzeń DSP1701A_ADCTDM_TAA5242 – czterokanałowego przetwornika A/D (fotografia 4). Moduł zwiększa funkcjonalność płytki bazowej o cztery kanały przetwornika A/D, co w połączeniu z przetwornikiem wbudowanym w strukturę ADAU1701 umożliwia realizację przedwzmacniaczy lub mikserów z trzech źródeł sygnału analogowego.

Schemat projektu ADAU1701_MK2_Cz5_ProjektTestowyTDMADC.dspproj widać na rysunku 16.

Aplikacja realizuje funkcję trzykanałowego miksera stereo z regulacją barwy tonu i wzmocnienia, niezależnie dla każdego z kanałów. Całość uzupełnia generator testowy. Miksowane są kanały z wbudowanego przetwornika (blok Input, wejścia 0, 1) oraz z przetworników A/D modułu rozszerzeń TAA5242 (blok Input, wejścia 2...5). Należy zwrócić uwagę na mapowanie kanałów: wejścia IN34 mapowane są na kanały 2, 3, wejścia IN12 na kanały 4, 5. Dodatkowo należy zamienić kanały 23 i 45, dla zachowania zgodności kanałów L/R z gniazdem IN na płytce bazowej. Zamiana kanałów w aplikacji ułatwia zaprojektowanie płytki i zachowanie oznaczeń kanałów przetwornika TAA5242. Sygnał wyjściowy wyprowadzony jest do wbudowanego przetwornika D/A. Konfigurację interfejsu szeregowego DSP do pracy w formacie TDM pokazano na rysunku 17.

Przed wgraniem aplikacji należy skonfigurować płytkę bazową, zakładając zwory generatora OSC oraz MCLK i doprowadzając sygnał zegarowy do złącza I2SI. Moduł DSP1701A_ADCTDM_TAA5242 podłączony jest z lewej strony płytki bazowej do złącza I2SI. W zależności od posiadanego źródła sygnału, należy doprowadzić sygnał niesymetryczny (stereo) do gniazd IN12 i IN34, zwierając zwory w złączach szpilkowych IN1...4 (wyprowadzenia 2–3) oraz zdjąć zwory z SD12, SD34, ustalając niesymetryczną konfigurację wejść przetworników A/D. W przypadku sygnału symetrycznego należy założyć zwory SD12, SD34, a sygnał doprowadzić bezpośrednio do złączy szpilkowych IN1...4 (1: IN+, 2=IN–, 3=GND), pozostawiając złącza IN12, IN34 niepodłączone. Po konfiguracji procesora i wgraniu aplikacji, powinno być możliwe miksowanie i korygowanie barwy każdego z kanałów.

Interfejs wyjściowy TDM

Projekt testowy do demonstracji sposobu obsługi wejściowego interfejsu szeregowego, skonfigurowanego w formacie TDM, przeznaczony jest do sprawdzenia modułu rozszerzeń DSP1701A_DACTDM_TAD5142 – czterokanałowego przetwornika D/A (fotografia 5). Moduł poszerza funkcjonalność płytki o cztery kanały wyjść analogowych, co razem z wbudowanym czterokanałowym przetwornikiem D/A umożliwia przykładowo realizację aktywnych, stereofonicznych zwrotnic głośnikowych.

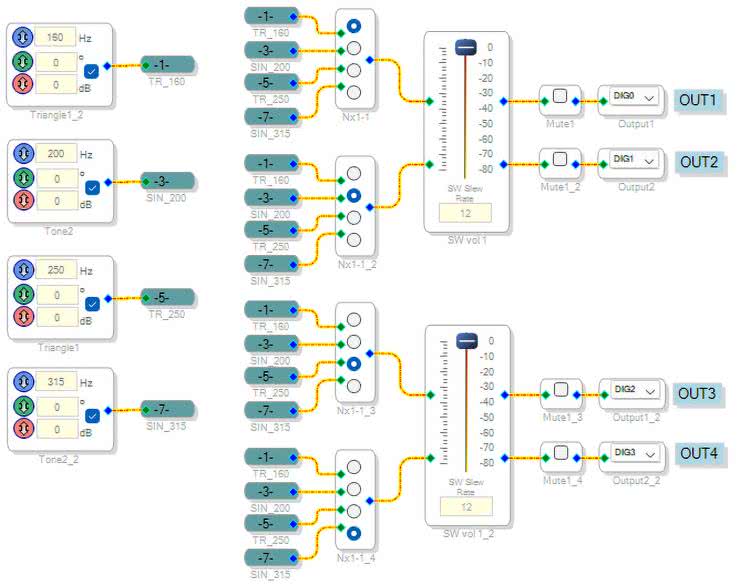

Schemat projektu ADAU1701_MK2_Cz5_ProjektTestowyTDMDAC.dspproj zamieszczono na rysunku 18.

Aplikacja zawiera czterokanałowy generator sinuoidalnego sygnału testowego 200/315 Hz i trójkątnego 160/250 Hz. Sygnał z każdego z generatorów może zostać – przy pomocy multiplekserów – doprowadzony (poprzez regulatory poziomu) do jednego z wyjść cyfrowych, a stąd do przetworników D/A typu TAD5142. Konfigurację wyjściowego interfejsu szeregowego DSP do formatu TDM zaprezentowano na rysunku 19.

Przed wgraniem aplikacji należy skonfigurować płytkę bazową, zakładając zwory generatora OSC. Moduł DSP1701A_DACTDM_TAD5142 podłączony jest z prawej strony płytki bazowej do złącza I2SO. Do kontroli działania aplikacji potrzebny będzie oscyloskop. Na płytce rozszerzeń zdejmujemy zwory SD1, SD2, ustalając w ten sposób niesymetryczną konfigurację wyjść przetworników D/A. Po konfiguracji procesora i wgraniu aplikacji podłączamy sondę oscyloskopu do kolejnych kanałów wyjściowych, sprawdzając obecność wybranego multiplekserem sygnału. Domyślnie aplikacja generuje na każdym wyjściu przebieg o innej częstotliwości, co może zostać zweryfikowane błyskawicznie przy pomocy oscyloskopu czterokanałowego. Obecność sygnału można oczywiście sprawdzić także podłączając wzmacniacz do gniazd OUT12, OUT 34 i zwracając przy tym uwagę na poziom sygnału.

To był już ostatni projekt testowy, kończący krótki kurs DSP na bazie płytki DSP1701A_DSP_MK2. Dziękuję za uwagę i zachęcam do tworzenia własnych aplikacji z ADAU1701 oraz innymi procesorami z rodziny Sigma DSP!

Adam Tatuś, EP

Zaloguj

Zaloguj