Prenumerata - wygodny i prosty sposób na dostęp do projektów i materiałów z poziomu naszej strony

Natychmiastowy dostęp do najnowszych treści oraz pełnego archiwum

Kup teraz

ep w toku

Artykuły w przygotowaniu, które ukażą

się w najbliższych numerach EP

się w najbliższych numerach EP

Elastyczne i sztywno-giętkie obwody...

Prezentacje

Moduł precyzyjnego zegara RTC z interfejsem...

Miniprojekty

Elektroniczny papier

Temat miesiąca

Instalacje nisko- i wysokoprądowe

Elektronika w praktyce

Fuzz klasyczny na LPC55S28

Moduły w aplikacjach

Wzbudzenie drgań rezonatorów kwarcowych...

Notatnik konstruktora

Internet Rzeczy w pomiarach środowiskowych...

Moduły w aplikacjach

Odbiornik FM zbudowany na układzie TEF6686

Projekty SOFT

Wzmacniacz lampowy PCL86 Stereo

Projekty czytelników

Kurs FPGA Lattice (18). Nadajnik UART

Kursy

Zaawansowany selektor audio

Projekty EP

Odbiornik nasłuchowy na pasmo KF 80 m...

Projekty EP

codeLock - efektowny zamek kodowy

Projekty EP

Nakładka z wyświetlaczem OLED do AVTDuino...

Projekty EP

Płytka ewaluacyjna z mikrokontrolerem...

Projekty EP

Miniwyświetlacz LCD 4×10 znaków...

Miniprojekty

Pięciokanałowy termometr I²C

Miniprojekty

Oszczędzanie energii w teorii i w praktyce...

Notatnik konstruktora

Nowoczesne wyświetlacze w ofercie firmy...

Prezentacje

Kompleksowe usługi montażu PCB w ofercie...

Prezentacje

Crash Course STM32C0 - programowanie...

Kursy

Chłodzenie w urządzeniach elektronicznych...

Elektronika w praktyce

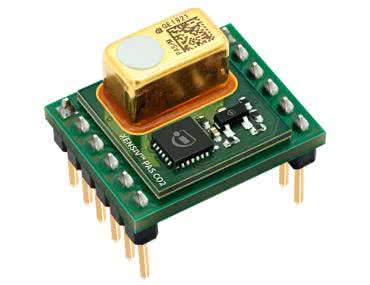

Internet Rzeczy w pomiarach środowiskowych...

Moduły w aplikacjach

Prosty higrometr RGB

Miniprojekty

Dwuportowy mikrohub USB-C do systemów...

Miniprojekty

Zasilacz PoE 5/12 V 30 W

Miniprojekty

Zestawy ewaluacyjne i inteligentne...

Prezentacje

Sterownik silników do AVTDuino UNO R4

Projekty EP

powerTracker. Rejestrator parametrów...

Projekty EP

Przegląd rynku mikrokontrolerów 2024

Temat miesiąca

Narzędzia sprzętowe dla programistów...

Temat miesiąca

Chłodzenie w urządzeniach elektronicznych

Prezentacje

Zasilanie energooszczędnych mikrokontrolerów

Notatnik konstruktora

Multimetr stołowy Owon XDM3051. 5½ cyfry...

Aparatura i narzędzia

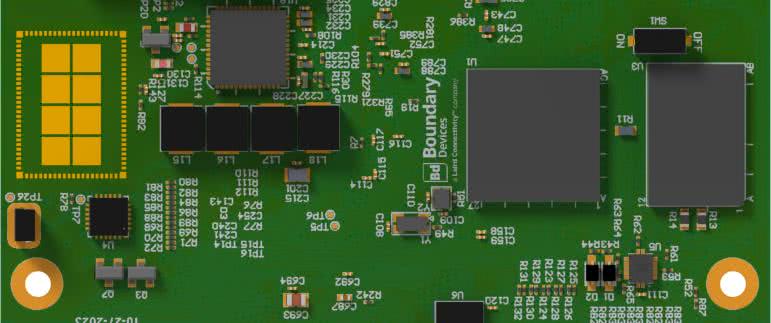

Moduły SoM od Laird Connectivity – gdy...

Prezentacje

Ewolucja peryferiów analogowych...

Prezentacje

Programowanie pamięci mikrokontrolerów

Prezentacje

Nowy enkoder przyrostowy Faulhaber IEP3

Prezentacje

Nowoczesne materiały termoprzewodzące

Prezentacje

Mikrokontrolery z rodziny AVR DB oraz AVR...

Prezentacje

Przekrojowa oferta mikrokontrolerów...

Prezentacje

Wygraj zestaw ewaluacyjny Microchip...

Konkurs

Kurs FPGA Lattice (17). Odtwarzacz melodii

Kursy

Anatomia systemów BMS

Temat miesiąca

Robotyka w medycynie (2). Przegląd...

Podzespoły

Kurs FPGA Lattice (16). Generowanie dźwięków

Kursy

TARS MK4 - wydajny komputer pokładowy...

Projekty SOFT

Zwiększanie wydajności systemów wbudowanych...

Prezentacje

Wybór przełącznika - rodzaje, parametry,...

Elektronika w praktyce

Przełączniki APEM - jakość, której możesz...

Prezentacje

Mikroskop cyfrowy Andonstar AD249S-M....

Aparatura i narzędzia

Internet Rzeczy w pomiarach środowiskowych...

Moduły w aplikacjach

Kontrolery ruchu do miniaturowych napędów...

Prezentacje

Akyga Battery - sprawdzone źródła energii...

Prezentacje

Minimoduł precyzyjnego generatora...

Miniprojekty

Dwukanałowy port szeregowy z pełnym...

Miniprojekty

Sterownik mikrosilników prądu stałego

Miniprojekty

Aktywny hub I²C Grove

Miniprojekty

Uniwersalny przekaźnik dużej mocy...

Miniprojekty

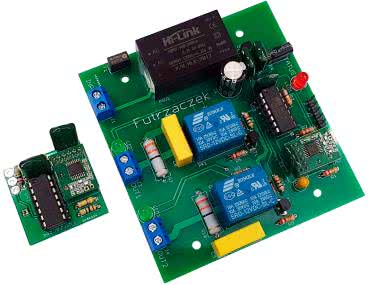

Bezprzewodowy włącznik dwukanałowy

Projekty EP

Odbiornik nasłuchowy na pasmo KF 80 m...

Projekty EP

Wskaźnik wysterowania 2×8 LED

Projekty EP

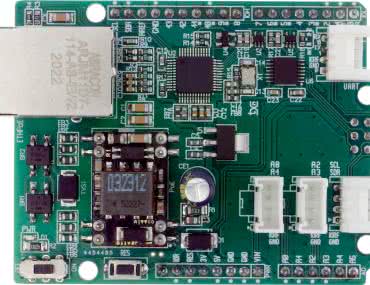

Nakładka Ethernet PoE do AVTDuino

Projekty EP

Zaufany dystrybutor oprogramowania,...

Prezentacje

HZD GmbH – niemiecka rzetelność...

Prezentacje

Trzecia edycja TEK.day Wrocław – to już 14...

Koktajl newsów

Wygraj zestaw ewaluacyjny Microchip PIC32MK...

Konkurs

Robotyka w medycynie (1)

Temat miesiąca

Zamek do drzwi oparty na Arduino, który...

Projekty SOFT

MIDIBox (2). Niezwykły kontroler MIDI

Projekty SOFT

Rozwiązania dla nowoczesnych interfejsów...

Prezentacje

Klawiatury foliowe - przegląd technologii

Elektronika w praktyce

QWERTY - Twój sprawdzony dostawca klawiatur...

Prezentacje

Efekt do gitary na bazie LPC5528

Moduły w aplikacjach

Internet Rzeczy w pomiarach środowiskowych...

Moduły w aplikacjach

Rewolucja w świecie audio - subminiaturowe...

Podzespoły

Zaawansowane obwody PCB do najbardziej...

Prezentacje

Mechaniczny potencjometr cyfrowy

Miniprojekty

Mostek master I²C/1-Wire w standardzie Grove

Miniprojekty

Bufor I²C Grove

Miniprojekty

IP-Coach IV. Reaktywacja

Projekty czytelników

Wygraj płytkę rozwojową Microchip PIC-IoT WG

Konkurs

Progowy licznik impulsów

Projekty EP

Uniwersalny przedwzmacniacz (3)

Projekty EP

e-Nurse - elektroniczny dyspenser leków (2)

Projekty EP

Odbiornik nasłuchowy na pasmo KF 80 m...

Projekty EP

AVTDuino UNO R4 Plus

Projekty EP

Kurs FPGA Lattice (15). Pamięć EBR

Kursy

Systemy akwizycji danych w pracowni...

Temat miesiąca

Uniwersalny przedwzmacniacz (2)

Projekty EP

Termometr z pamięcią wartości skrajnych

Projekty EP

MicroMote - pilot do zdalnego sterowania za...

Projekty SOFT

Translator poziomów 1,2...5,5 V w...

Miniprojekty

e-Nurse - elektroniczny dyspenser leków (1)

Projekty EP

Uniwersalny moduł z przekaźnikiem SSR

Miniprojekty

Sygnalizator napełnienia wanny

Miniprojekty

Bożonarodzeniowe drzewko LED

Miniprojekty

Asystent głosowy na bazie Raspberry Pi 4...

Projekty SOFT

Niezwykły kontroler MIDI - MIDIBox (1)

Projekty SOFT

Automatyka budynkowa - realizacja...

Elektronika w praktyce

Minimoduł z procesorem NXP LPC865

Miniprojekty

Sansuix - lampowy wzmacniacz mocy 2×20 W -...

Projekty EP

RX Ewa 40 m - odbiornik początkującego...

Projekty EP

Wygraj płytkę rozwojową Microchip PIC-IoT WA

Konkurs

Zoptymalizowane systemy obudów do Raspberry...

Prezentacje

LabJack T8

Prezentacje

KKNOON G1200 - prawie dobry mikroskop...

Aparatura i narzędzia

Struktura wielowarstwowych płytek od PCBWay

Prezentacje

Raspberry Pi 5 - długo wyczekiwany następca...

Podzespoły

Kurs FPGA Lattice (14). Enkoder obrotowy

Kursy

Wielowarstwowe płytki drukowane, co każdy...

Elektronika w praktyce

Zagadnienia materiałowe w produkcji...

Elektronika w praktyce

Regulator barwy dźwięku na bazie płytki...

Moduły w aplikacjach

Płytki PCB zoptymalizowane do produkcji

Prezentacje

Uniwersalny przedwzmacniacz (1)

Projekty EP

Aplikacje enkoderów obrotowych z...

Podzespoły

Laminat FR-4 - używany przez wielu, znany...

Prezentacje

Produkcja wielowarstwowych płytek PCB krok...

Prezentacje

Banki energii. Zarządzanie ciepłem i...

Prezentacje

Skazani na lit

Temat miesiąca

Mikrowzmacniacz mocy 20 W na układzie PAM8320

Miniprojekty

Sygnalizator utraty ciągłości

Miniprojekty

Wygraj płytkę rozwojową Microchip PIC24F...

Konkurs

multiLock

Projekty EP

Bezpieczne złącza do magazynów energii

Prezentacje

Wskaźnik stanu emocjonalnego

Miniprojekty

Moduł czterech wyjść HighSide dla RPi Pico

Miniprojekty

Wielowarstwowe PCB, od prostych do...

Prezentacje

Kompleksowa produkcja elektroniki z...

Prezentacje

MIDIXCV - konwerter MIDI do modułowego...

Projekty SOFT

Kurs FPGA Lattice (13). Wyświetlacz LCD...

Kursy

Oscyloskop Siglent SDS1104X-U. Jeden z...

Aparatura i narzędzia

GPSDO - jak GPS pilnuje czasu

Notatnik konstruktora

Maksymalizuje sprawność elektroniki

Prezentacje

Dwukanałowy konwerter USB-C z układem FT2232H

Projekty EP

Czujniki optyczne (4). Sensory koloru oraz...

Podzespoły

Moduł czterech wyjść przekaźnikowych z...

Miniprojekty

Wzmacniacz lampowy o mocy 2×80 W z...

Projekty czytelników

Obudowy dla elektroniki. Konstrukcja,...

Prezentacje

Technika spiekania laserowego w produkcji...

Elektronika w praktyce

Modyfikacja i tworzenie obudów w firmie...

Prezentacje

XXXI Międzynarodowy Salon Przemysłu...

Koktajl newsów

Najnowsze płytki Raspberry Pi 5 dostępne w...

Koktajl newsów

Termostat do elektrozaworu z silnikiem DC

Projekty EP

Wykrywanie usterek na gorąco. Diagnostyka...

Temat miesiąca

Ładowanie Qi, które zapewnia pełne...

Prezentacje

Nowoczesne obudowy do automatyki domowej i...

Prezentacje

Tworzenie innowacyjnych projektów w...

Elektronika w praktyce

Nowa rzeczywistość w przemyśle

Prezentacje

Wygraj programator Microchip MPLAB PICkit 5

Konkurs

Wyzwanie projektowe „Upcycle IoT”

Konkurs

Arduino Nano ESP32

Koktajl newsów

Kurs FPGA Lattice (12). Symulacja w Icarus...

Kursy

Wielofunkcyjne kamery termowizyjne i...

Prezentacje

MultiHub - uniwersalny hub serwisowy do...

Projekty EP

toneCtrl – regulator barwy dźwięku

Projekty EP

Prosty sejsmograf na bazie Arduino

Projekty SOFT

Zasilacz do płytek stykowych ze złączem USB-C

Miniprojekty

Izolowany interfejs RS232 dla Raspberry Pi

Miniprojekty

Sygnalizator poboru prądu

Miniprojekty

Regulowany zasilacz napięcia ujemnego

Miniprojekty

Standby killer

Miniprojekty

Pozycjonowanie GNSS centymetrowej precyzji,...

Prezentacje

Moduł wejść cyfrowych z optoizolacją i...

Miniprojekty

Filtr zasilania do Raspberry Pi

Miniprojekty

Pomiary odległości i prędkości

Elektronika w praktyce

Nie tylko GPS. Przegląd alternatywnych...

Temat miesiąca

Wzmacniaczu operacyjny, nie wzbudzaj się!

Notatnik konstruktora

Poprawa jakości sygnału uwalnia prawdziwy...

Notatnik konstruktora

Wygraj programator/debugger Microchip ICD 5

Konkurs

Precyzja i dokładność w Systemach Globalnej...

Temat miesiąca

Arduino UNO R4 Minima - wydajna i...

Nowe produkty

Kinetyczne wzory na piasku, sterowane przez...

Projekty SOFT

Solarna ładowarka akumulatorów z MPPT (2)

Projekty SOFT

Narzędzia do szybkiego prototypowania z...

Prezentacje

Kurs FPGA Lattice (11). Statyczna analiza...

Kursy

Sansuix - lampowy wzmacniacz mocy 2×20 W (2)

Projekty EP

Płytki rozwojowe do kursu FPGA Lattice

Projekty EP

Urządzenia zasilające (4). Praktyczne...

Notatnik konstruktora

Ball & Beam (3)

Moduły w aplikacjach

Nowoczesne prototypowanie

Elektronika w praktyce

Proste i elastyczne transceivery interfejsu...

Notatnik konstruktora

Miniaturowy termostat cyfrowy

Miniprojekty

Cyfrowy miernik kąta z magnesami...

Projekty SOFT

Mikrokontrolery MEGAWIN. Od 8051 do Cortex-M3

Prezentacje

Izolator sygnału analogowego 0...100 VDC

Miniprojekty

Trójfazowy przetwornik prądu przemiennego z...

Miniprojekty

Regulowany stabilizator napięcia ujemnego

Miniprojekty

Solarna ładowarka akumulatorów z MPPT (1)

Projekty SOFT

Wyświetlacze vs. słońce, czyli Sunlight...

Temat miesiąca

Sansuix - lampowy wzmacniacz mocy 2×20 W (1)

Projekty EP

IoT z zastosowaniem Wi-Fi 6

Prezentacje

Wyświetlacze do aplikacji zewnętrznych

Prezentacje

Nowy poziom interakcji z użytkownikiem w...

Prezentacje

Elektroniczny gong

Miniprojekty

Głowa robota InMoov

Projekty EP

Czujnik punktu rosy

Miniprojekty

Ekspander GPIO RPi z taśmą FPC

Miniprojekty

Wyświetlacze od AZ Displays. Optymalne do...

Prezentacje

Wygraj zestaw ewaluacyjny Microchip...

Konkurs

Niepotrzebne źródła szumu

Notatnik konstruktora

Szczególnie polecamy

Projekty

Klub Aplikantów Próbek

Rozdajemy za darmo próbki atrakcyjnych podzespołów modułów i urządzeń

Zobacz więcej

Artykuły

Zaloguj

Zaloguj